Изобретение относится к вычислительной технике и может быть использовано для обработки цифровых сигналов в реальном времени, в том числе для построения дафровых фильтров и цифровых систем автоматического регулирования .

Цель изобретения - сокращение объема оборудования устройства при точности результата до т-го разряда.

В процессе умножения двух чисел в дополнительном коде получается округленный результат с числом разрядов не менее максимального числа разрядов сомножителей (т).

Произведение при округлении до m разрядов (тип- число разрядов первого и второго сомножителей соответственно, ) вычисляется по формуле

n m ,

i;,2-4-.x,

4,1 J

X II 9 j- , +

4i

-1:2 :jm n-x

.2-.2-.

где

п-к УП,

J

- частичные произведения, суммируемые с определенными весами. Число S находится из условия, чтобы при округлении результата произведения до m старших разрядов () погрешность вычисления не превышала половины единицы младщего разряда округленного результата произведения

Д -(m4 n-i 11(1+1)2

14

-()

2 - вес младшего разряда округленного результата произведения .

Количество вычислительных операсокращается на число, соответстее члену, определяемому числом S заданных значениях тип, t

1.--0

X,

У L

который заменяется на константу + )

При этом сокращается число вычисляемых частичных произведений на

S(S+1)

операции суммирования на

(S-1) S

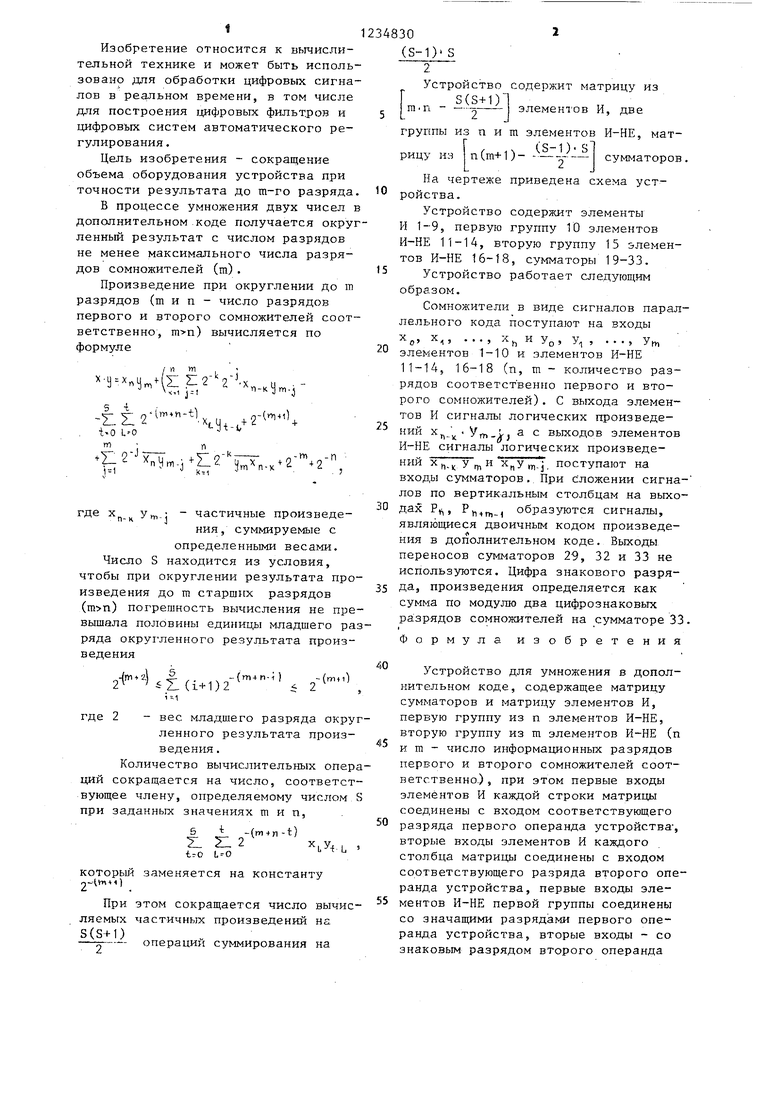

Устройство содержит матрицу из

S(S+1),

элементов И, две

т п группы из п и m элементов И-НЕ, мат , ,, (S-1)- Sl рицу и;- п(т+1) сумматоров.

На чертеже приведена схема устройства.

Устройство содержит элементы И 1-9, первую группу 10 элементов И-НЕ 11-14, вторую группу 15 элементов И-НЕ 16-18, сумматоры 19-33.

Устройство работает сле.дугощим образом.

Сомножители в виде сигналов параллельного кода поступают на входы

о 1 элементов

и у

о

у.

1-10 и элементов И-НЕ 11-14, 16-18 (п, m - количество разрядов соответственно первого и второго сомножителей). С выхода элементов И сигналы логических произведении X

п-к

r.-, a

с выходов элементов

И-НЕ сигналы логических произведе0

5

5

0

0

5

нии X

и-к

m.j

поступают на

входы сумматоров,. При Сложении сигна- лов по вертикальным столбцам на выходах Р, Ph4m-i образуются сигналы, являющиеся двоичным кодом произведения в дополнительном коде. Выходы переносов сумматоров 29, 32 и 33 не используются. Цифра знакового разряда, произведения определяется как сумма по модулю два цифрознаковых ра зрядов сомножителей на сумматоре 33.

Формула изобретения

Устройство для умножения в дополнительном коде, содержащее матрицу сумматоров и матрицу элементов И, первую группу из п элементов И-НЕ, вторую группу из m элементов И-НЕ (п и га - число информационных разрядов первого и второго сомножителей соответственно.) , при этом первые входы элементов И каждой строки матрицы соединены с входом соответствующего разряда первого операнда устройства-, вторые входы элементов И каждого столбца матрицы соединены с входом соответствующего разряда второго операнда устройства, первые входы элементов И-НЕ первой группы соединены со значащими разрядами первого опе- ранд,а устройства, вторые входы - со знаковым разрядом второго операнда

устройства, первые входы элементов И-НЕ второй группы соединены со значащими разрядами второго операнда устройства, а вторые входы - со знаковым разрядом первого операнда устройства, выходы элементов И-НЕ первой группы соединены с входами первого слагаемого сумматоров (т-1)-й строки матрицы, выходы элементов И-НЕ вто12348304

ды переноса сумматоров (т+1)-й строки матрицы соединены соответственно с входами переноса последующих сумматоров той же строки, входы переноса первого сумматора (1п+1)-й строки матрицы соединены с шиной логического нуля устройства, знаковые разряды первого и второго сомножителей устройства соединены с входами п-го

рои группы соединены с входами второ- Ю сумматора (т+1)-й строки матрицы,

го слагаемого сумматоров первого вход переноса которого соединен с шистолбца матрицы выходы элементов И ной логического нуля устройства, кажго столбца (1-2, ..., т-1) матрицы дал i-я строка матрицы элементов И соединены соответственно с входами содержит (m-S+k-1) элементов И, где первого слагаемого сумматоров (|-1)-й J5 при ,1,...,S и при строки матрицы, выходы j-x элемен- ..., п-1 (S - величина, определяемая тов И (, ,,., n-t) первого столбца ма.трицы соединены с входами второго слагаемого сумматоров, j-x столб20

цов первой строки, входы переноса сумматоров ш-го и п-го столбцов первой строки матрицы соединены с шиной логической единицы устройства, выхополучением необходимой точности вычисления S-i+1«m), отличающееся тем, что, с целью сокращения объема оборудования, входы переноса первого сумматора (п-2)-го столбца матрицы соединены с шиной логической единицы устройства.

Ж

jif

Ll

2348304

ды переноса сумматоров (т+1)-й строки матрицы соединены соответственно с входами переноса последующих сумматоров той же строки, входы переноса первого сумматора (1п+1)-й строки матрицы соединены с шиной логического нуля устройства, знаковые разряды первого и второго сомножителей устройства соединены с входами п-го

Ю сумматора (т+1)-й строки матрицы,

дал i-я строка матрицы элементов И содержит (m-S+k-1) элементов И, где при ,1,...,S и при ..., п-1 (S - величина, определяемая

получением необходимой точности вычисления S-i+1«m), отличающееся тем, что, с целью сокращения объема оборудования, входы переноса первого сумматора (п-2)-го столбца матрицы соединены с шиной логической единицы устройства.

гЩ.

Редактор Е. Копча

Составитель 0. Маркелова

Техред М.ХоданичКорректор Г. Решетник

Заказ 2986/51 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU849208A1 |

| Устройство для умножения | 1982 |

|

SU1037247A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Устройство для вычисления сумм произведений | 1984 |

|

SU1166101A1 |

| Устройство для умножения двоичных чисел в дополнительном коде | 1983 |

|

SU1191907A1 |

| Устройство для возведения в квадрат,извлечения квадратного корня,умножения и деления | 1981 |

|

SU1059571A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

Изобретение относится к области вычислительной техники и предназначено для применения в цифровой фильтрации. Изобретение позволяет повысить быстродействие устройства и уменьшить количество затрачнваемог о оборудования за счет исключевсия из 5(5+1) 2 полной матрицы элементов И ()S элементов И, сумматоров, участвующих в вычислении произведения младших разрядов. Освободившиеся входы переносов сумматоров 5-й строки 1-го столбца, (5-1)-й строки 11-го столбца, ., 2-й строки (S-l)-ro столбца соединены с шиной логического нуля устройства, а вход переноса сумматора 1-й строки : (п-2)-го столбца соединен с шиной логической единицы. 1 ил. (Л

| Устройство для умножения | 1981 |

|

SU1024906A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричное устройство для умножения | 1981 |

|

SU999044A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для умножения | 1982 |

|

SU1037247A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-03-01—Подача