(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1037247A1 |

| Матричное устройство для умножения | 1981 |

|

SU999044A1 |

| Устройство для умножения в дополнительном коде | 1984 |

|

SU1234830A1 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Матричное вычислительное устройство | 1982 |

|

SU1034032A1 |

| Устройство для умножения | 1989 |

|

SU1697078A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU938282A1 |

1

Изобретение откосится к вычислительной технике и может .быть использовано при построении специализированных вычислителей, предназначенных для цифровой обработки сигналов в реальном масштабе времени.

Известны устройства умножения, состоящие из регистра множителя, регистра множимого и накапливающего сумматора ..

Недостатком данных устройств является низкое быстродействие.

Известно устройство умножения, содержащее матрицу mxnэлементов И (п и m - число информационных разрядов первого и второго сомножителей соответственно), матрицу (m-l)xn сумматоров, при этом первые входы элементов И каждой строки матрицы объединены и являются входами соответствующих разрядов первого операнда устройства, вторые входы элементов И каждого столбца матрицы объединены и являются входами соответствующих разрядов второго операнда устройства, выходы элементов И I -го столбца ( Е- 2,...,т) матрицы соединены соответственно с входами первого слагаемого сумматоров (2 -1)-ой строки матрицы, выходы (г+1)-ых элементов И (г 1,...,п-1) первого столбца матрицы соединены с входами второго слагаемого сумматоров г-ых столбцов первой строки, выход эле- . мента И первой строки первого столбца матрицы является выходом первого разряда произведения устройства, выходы сумматоров первого, столбца матрицы являются соответственно вы10ходами разрядов 2,...,т произведения устройства, выходы переноса сумматоров (&-1)-го столбца матрицы соединены с соответствующими входами сумматоров К -ой строки матрицы, |5 выходы суммы (г+1)-ых сумматоров (-1)-ой строки матрицы соединены с входами второго слагаемого соответственно сумматоров г-ых столбцов &-ОЙ строки матрицы 2.

20

Недостаток известного устройства заключается в отсутствии возможности умножения чисел, представленных дополг нительным кодом.

Цель изобретения - расширение

25 функциональных возможностей устройства за счет т«ножения операндов,предоставленных дополнительным кодом.

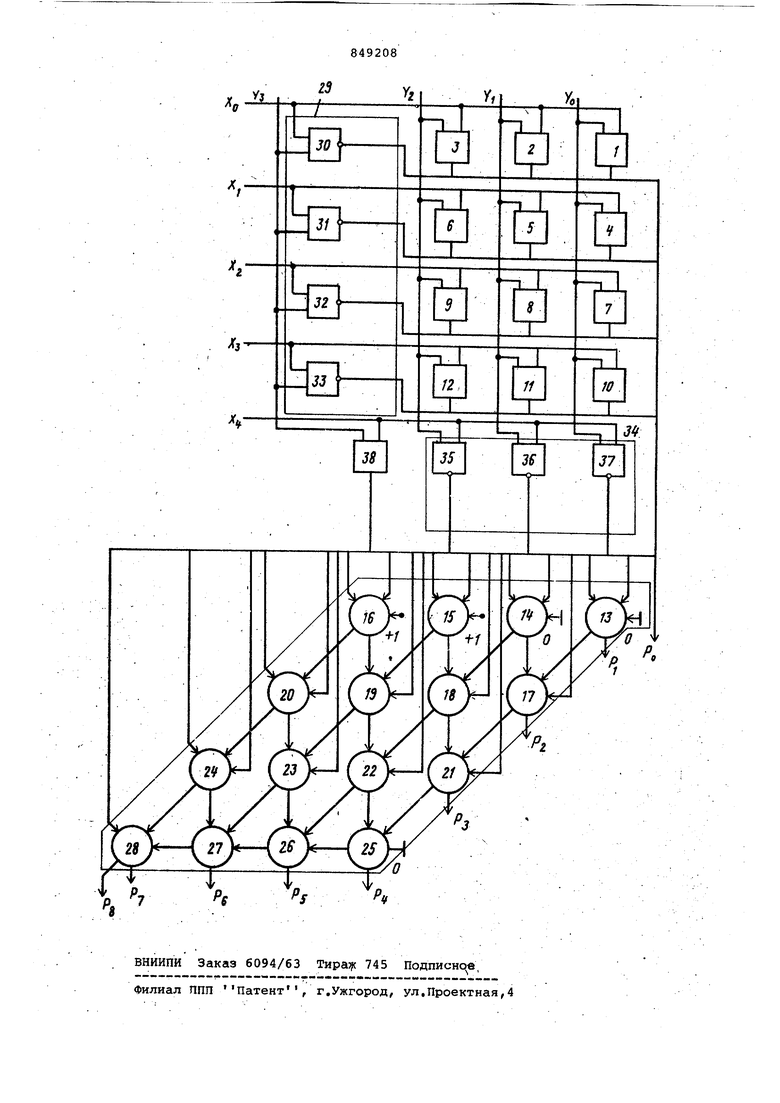

Поставленная цель достигается тем, что устройство, содержащее матрицу , тип элементов И (п и п-число инфор30мационных разрядов первого и второго Сомножителей соответственно), ,матрицу (ш-1)кп сумматоров, при этом первые входы элементов И каждой |Строки матрицы объединены и .являются входами соответствующих разрядов первого операнда устройства, вторые входы элементов И каждого столбца матрицы объединены и являются входами соответствующих разрядов второго операнда устройства, выходы элементов ИИ -го столбца (6 2,..,,т) матрицы соединены соответственно с входами первого слагаемого сумматоров (6-1)-ой строки матрицы, выходы (г+1)-ых элементов И (,...,п-1) первого столбца матрицы соединена с входами второго слагаемого сумматоров г-ых столбцов первой строки, выход элемента И первой строки первого столбца матрицы является выходом первого разряда произведения устройства, выходы сумматоров перво столбца матрицы являются соответственно выходами разрядов 2,...,т произведения устройства, выходы переноса сумматоров (B-l)-rp столбца матрицы соединены с соответствующими входами сумматоров 6 -ой строки матрицы, выходы суммы (г+1)-ых сумматоров (0-1)-ой строки матрицы сое динены с входами второго слагаемого соответственно сумматоров г-ых стол цов и -ой строки матрицы, дополнительно содержит первую группы из п элементов И-Кр, вторую группу из m элементов И-НЕ, элемент И, а также содержит в матрице дополнительные т-ую и (т+1)-ую строки-по п суммато ров, причем первые входы элементов И-НЕ первой группы соединены с входами соответствующих разрядов перво операнда устройства, вторые входы с входом знакового разряда второго операнда устройства, первые входы элементов И-НЕ второй группы соедин с входами соответствующих разрядов второго операнда устройства, а втор входы - с входом знакового разряда первого операнда устройства, первый и второй входы элемента И соединей с входами знаковых разрядов соответ ственно парвого и второго операндов выходы элементов И-НЕ первой группы соединены соответственно с входами первого слагаемого сумматоров т-ой строки матрицы, выходы элементов Ивторой группы соединены соответстве но с входами второго слагаемого сум маторов п-го столбца матрицы, выход элемента И соединен с первым входом сумматора п-го столбца itrn-l -ой строки матрицы, выходы переноса сумматоров (т-1)-ой и т-ой строк -соединены с соответствующими входам сумматоров соответственно т-рй и (т+1)-ой строк матрицы, выходы суммы сумматоров (г+1)-ых столбцов (т-1)-ой строки матрицы соединены с входами второго слагаемого соответствующих сумматоров i-ых столбцов т-ой строки матрицы, выходы суммы сумматоров (г+1)-ых столбцов т-ой троки матрицы - с входами второго лагаемого сумматоров г-ых столбцов т+1)-ой строки матрицы, выходы пееноса сумматров г-ых столбцов (т+1)-рй строки матрицы.соединены соответственно с входами второго слагаемого сумматоров (г+1)-ых столбцов, выход суммы сумматора первого столбца 1л-ой строки матрицы является выходом {т+1)-го разряда произведения устройства, а выходы суммы сумматров 1,.., ,п (т+1)-ой строки матрицы являются выходами соответственно m+2,.,.m+n+l разрядов произведения устройства, входы переноса сумматоров столбцов 1,...п-2 первой строки матрицы соединены с шиной потенциала логического нуля, а входы переноса сумматоров п-го и (п+1)-го столбцов - с шиной потенциала логической единицы. . На чертеже приведена схема предлагаемого устройства. Устройство содержит элементы 1-12 И,сумматоры 13-28, первую группу 29 элементов 30-33 И-НЕ, вторую группу 34 элементов 35-37 И-НЕ и элемент 38 И. Матрица сумматоров содержит т+1 строк, в каждой строке имеется п сумматоров (п m). Устройство работает следующим образом. Входные числа (сомножители) в виде сигналов параллельного кода поступают на входы X д. . . X „ и Уо , . у m элементов 1-12 и 38 И и элементов 30-33 и 35-37 И-НЕ (пит- количество разрядов соответственно первого и второго сомножителей. С выхода элементов 1-12 и 38 И и элементов 30-33 и 35-37 И-НЕ сигналы логических произведений вида Угпk и j принимают соответственно значения от О до пи от О до т, поступают на входы сумматоров, причем сигналы вида х„-ку „и i-j, где k меняется от 1 до п и j - от 1 до m, поступают на входы сумматоров с выходов элементов И-НЕ. При сложении сигналов по вертикгшьным столбцам на выходах р , . . . ,рц-ц71 образуются сигналы, являющиеся разрядами выходного числа - произведения ху. Инвертирование сигналов вида И5)у,к,а также добавление сигналов логической единицы в ш-ом и п-ом разрядах выходного числа позволяют обойтись только операциями суммирования. Произведение, получаемое на выходах р о Рп4т ражается формулой ;vi « | Vrn-f l/ Wr

г2-.,.,.2

Предлагаемый матричный умножитель содержит сумматоры только одного типа, что существенно упрощает практическое построение устройства, расширяя его функциональные возможности.

Формула изобретения Устройство для умножения, содержащее матрицу ткп элементов И (п и m число информационных разрядов первбго и .второго сомножителей соответственно) , матрицу (m-l)x п сумматоров,при этом первые входы элементов И каждой строки матрицы объединены и являются входами соответствующих разрядов первого операнда устройства, вторые входы элементов И каждого столбца матрицы объединены и являются входами .соответствующих разрядов второго операнда устройства, выходы элементов И Е -го столбца (В 2,...,т) матрицы соединены соответственно с входами первого слагаемого сумматоров (2-1)-ой строки матрицы, выходы .(г+1)-ых элементов И (г 1,.. . ,п-1) первого столбца матрицы соединены с входами второго слагаемого сумма.торов г-ых столбцов первой строки, выход элемента И первой строки первого столбца матрицы является выходом первого разряда произведения устройства, выходы сумматоров первого столбца матрицы являются соответственно выходами разрядов 2,...,т произведения устройства, выходы переноса сумматоров (Й-1)-го столбца матрицы соединены с соответствующими входами сумматоров В-ой строки матрицы, выходы суммы (г+1)-ых сумматоров (&-1)-ой строки матрицы соединены с входами второго слагаемого соответственно сумматоров г-ых столбцов . й-ой строки матрицы, отличаю-, щ е е с я тем, что,, с целью расширения функциональных возможностей за счет умножения операндов, представленных дополнительным, кодом, оно содержит первурт группу из л элементов И-НЕ, вторую группу из m элементов И-НЕ, элемент И, а также содержит в матрице дополнительные т-ую и (т+1)-ую строки по п сумматоров,причем первые входы элементов И-НЕ первой группы соединены с входами соответствующих разрядов первого операнда устройства, вторые входы - с входом знакового разряда второго операнда устройства, первые входы элементов И-НЕ второй группы соединены с входами соответствующих разрядов второго операнда устройства, а вторы входы - с входом знакового разряда первого операнда устройства, первый и Второй входы элемента И соединены с входами знаковых разрядов соответственно яервого и второго операндов, выходы элементов И-НЕ первой группы соединены соответственно с входами первого слагаемого сумматоров т-ой строки матрицы, выходы элементов И-Н второй группы соединены соответственно с входси и второго слагаемого сумматоров п-го столбца матрицы, выход элемента И соединен с первым входом сумматора п-го столбца (т+1)-ой строки матрицы, выходы переноса сумматоров (п1-1)-ой и т-ой строк соединены с соответствующими входами сумматоров-соответственно т-ой и (т+1)-ой строк матрицы, выходы суммы сумматоров (г-1-1)-ых столбцов (т-1)-ой строки матрицы соединены с входами второго слагаемого соответствующих сумматоров г-ых столбцов т-ой строки матрищл, выходы суммы сумматоров (г+1)-х столбцов т-ой строки матрицы - с входами второго слагаемого сумматор ов г-ых столбцов (т+1)-ой строки матрицы., выходы переноса сумматоров г-ых столбцов (т+1)-ой строки матрицы соединены соответственно с входами второго слагаемого сумматоров (г+1)-ых столбцов, выход суммы сумматора первого столбца т-ой строки матрицы является выходом (т+1)го оазояда пооизведения устройства, а выхо.ты суммы сумматоров 1,.. . ,п , (т+1)-ой строки матрицы являются выходами соответственно m+2,.,;m+n+l разрядов произведения устройства, входы переноса сумматоров .столбцов 1,. .., п-2 первой строки матрицы соединены с шиной потенциала логического нуля, а входы переноса сумматоров п-го (п+1)-го столбцов - с шиной потенциала логической единицы. .

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-07-23—Публикация

1979-11-28—Подача