1 .13

.Изобретение относится к вычислительной технике и может быть использовано в измерительно-вычислительных комплексах и системах регистрации цифровых потоков информации, например, на магнитные носители.

Цель изобретения - повышение быстродействия устройства.

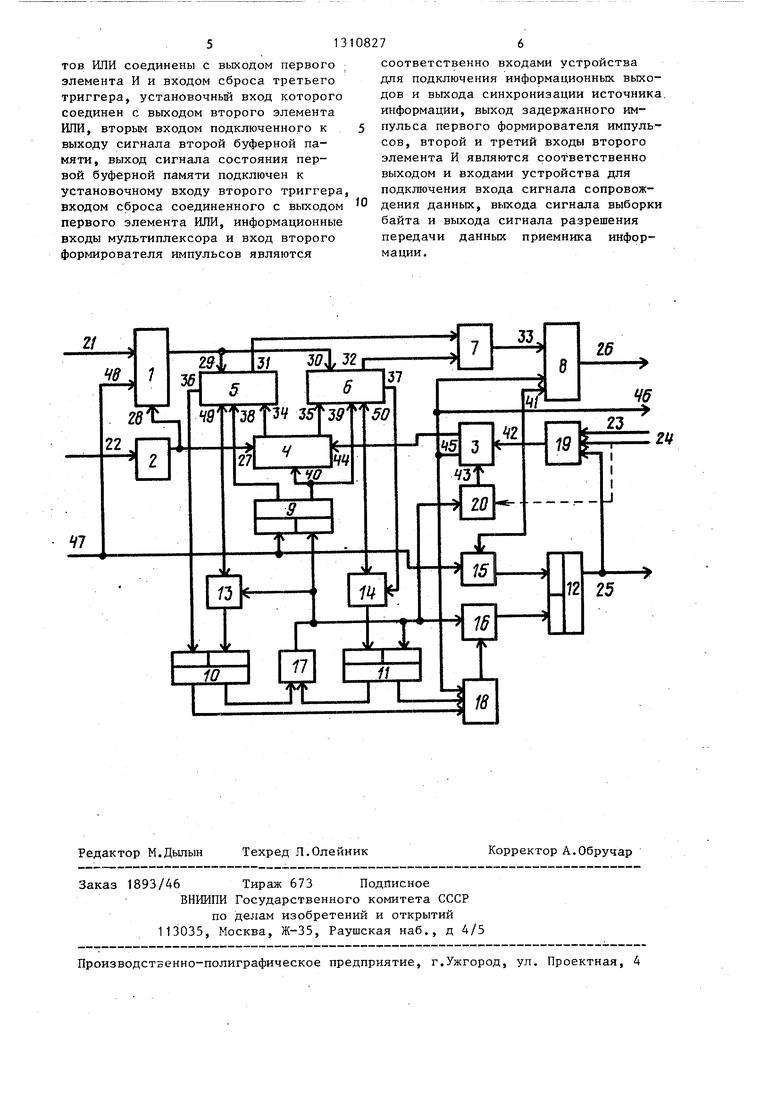

На чертеже показана функциональна схема устройства.

Устройство содержит мультиплексор 1, второй и первый формирователи 2 и 3 импульсов, коммутатор 4 тактов, буферные памяти (БЗУ) 5 и 6, группу элементов ИЛИ 7, выходной регистр 8, триггеры 9-12, элементы ИЛИ 13-16, первый, третий и второй элементы И 17-19. На чертеже показаны также связи 20-50 между элементами устройства

Начальное состояние устройства устанавливается сигналом Общий сброс на входе 47. При этом в начальное состояние приводится мультиплексор 1, БЗУ 5 и 6, сбрасываются триггеры 9, 10 и 12 и устанавливается триггер 11, Уровень О на входе 40 коммутатота 4 разрешает прохождение сигналов с выхода формирователя 2 через вход 27 на тактовый вход 34 БЗУ 5 и сигналов с выхода 43 формирователя 3 через вход 44 на тактовый вход 35 БЗУ 6. Уровень 1 на выходе 38 разрешает запись информации в БЗУ 5, элементы И 17-20 закрыты. В начальном состоянии устройство открыто для приема информации по входам 20 и 22.

Устройство работает следующим об-разом.

Каждый сигнал конца преобразования, поступающий из источника на вход 22, запускает формирователь 2, который вырабатывает серию тактовых сигналов записи информации в БЗУ. Число тактов определяется разностью (в байтах) входных информационных шин входа 20. Тактовые сигналы с выхода формирователя 2 поступают на вход 28 мультиплексора 1 и через вход 27 коммутатора 4 - на вход 34 БЗУ 5.

. По каждому тактовому сигналу, поступившему на вход 28 мультиплексора, происходит опрос входных информационных шин входа 21 и передача соот-. ветствующего байта данных с выхода мультиплексора 1 через вход 29 БЗУ 5. После опроса всех входных

272

информационных шин устройство переходит в режим ожидания следующего синхросигнала на входе 22.

Описанный цикл повторяется до тех

пор, пока не заполнится БЗУ 5 и не вьфаботается сигнал состояния Блок данных с выхода 36. Сигнал Блок данных вырабатьгоается при записи или чтении информации из последнего адреса БЗУ. По этому сигналу устанавливается триггер 10 и,.так как триггер 11 установлен (исходное состояние) , то открывается элемент И 17. По сигналу с его выхода устанавливается триггер 9, сбрасьшается триггер 10, а через элемент ИЛИ 16 устанавливается триггер 12. Переключение триггера 9 переводит устройство в следующее состояние,Тактовые сигналы с формирователя 2 через вход 27 коммутатора 4 поступают на вход 35 БЗУ 6, а тактовые сигналы с выхода формирователя 3 через вход

44 коммута тора 4 - на вход 34 БЗУ 5, При этом информация, поступающая на вход 21, записывается в БЗУ 6 (уровень 1 на входе 39). С установкой триггера 12 на выходе 25 появляется высокий уровень .сигнала запроса приемника на передачу данных Требование абонента, (ТРБ-А), т.е. устройство переходит в состояние готовности к передаче данных из БЗУ 5 на выходной регистр 8. В ответ

на сигнал ТРБ-А на вход 23 от ЦВМ поступает синхросигнал выборки байта данных при наличии сигнала разрешения передачи данных (отсутствие сигнала блокировки канала на входе

24)открывается элемент И 19. При

этом на выходе 4.1 сбрасывается выходной регистр 8,через элемент ИЛИ 15 сбрасывается триггер 12 (тем самым снимается запрос на передачу данных ТРБ-А) и запускается формирователь 3.

Тактовый сигнал выхода формирователя 3 поступает через вход 44 коммутатора 4 на вход 34 и выполняется такт чтения информации из БЗУ 5. При этом байт данных с выхода 31 БЗУ 5 поступает через элементы ИЛИ 7 на вход 33 выходного регистра 8 и по тактовому сигналу выхода 45 формирователя 3 заносится в выходной регистр 9. Сигнал выхода 45 формирователя 3 сигналов задержан относительно сигнала Время выборки байта

данных на выходе из БЗУ. Этот сигнал поступает также на выход 46 устройства.

Таким образом, с выхода 26 в ЦВМ передается байт данных, сопровождае- мый синхросигналом по выходу 46. Одновременно сигнал выхода 45 формирователя 3 проходит через элемент И 18 так как триггеры 10 и 11 сброшены, элемент ИЛИ 16 устанавливает, .триг гер 12, тем самым на выходе 25 появляется высокий уровень сигнала ТРБ-Л, Устройство переходит в режим ожидания очередного сигнала от ЦВМ на входе 23. Передача данных производится до тех пор, пока полностью не очистится БЗУ 5. тогда по сигналу Блок данных на его выходе 36 устанавливается триггер 10. С установкой триг

20

30

гера 10 закрывается элемент И 18, так что после передачи последнего байта данных из БЗУ 5 запрос на передачу данных ТРБ-А на выходе 25 не выставляется. Передача данных в ЦВМ приостанавливается.

После установки триггера 10 устройство продолжает работу только в режиме приема информации по входу 20. Как только заполнится БЗУ 6, на его выходе 37 появляется сигнал Блок данных, который через элемент ИЛИ 14 устанавливает триггер 11. При этом открывается элемент И 17, переключается триггер 9, сбрасывается триггер 11, через элемент ШШ 13 сбрасывается триггер 10 и через элемент ИЛИ 16 устанавливается триггер 12. Снова происходит переключение режимов устройства: разрешается запись информации в БЗУ 5, чтение информации из БЗУ 6 и устанавливается запрос на передачу данных ТРБ-А на выходе 25.

Дальнейшая работа устройства происходит аналогично.

Формула изобретения Устройство для сопряжения источни25

с выходом задержанного импульса пе вого формирователя импульсов, причем счетный вход первого триггера соединен с выходом первого элемент И, первый и второй входы которого подключены соответственно к прямым выходам второго и третьего триггер выход четвертого триггера подключе к первому входу второго элемента И отличающееся тем, что, с целью повышения быстродействия устройства, в него введены вторая буферная память, мультиплексор, ко мутатор тактов, элемент И и два эл мента ИЛИ, причем информационные входы первой и второй буферных па мятей подключены соответственно к выходу мультиплексора, а выходы и тактовые входы - соответственно к первым и вторым входам элементов И группы и первому и второму выходам коммутатора тактов, управляющий вх которого соединен с прямым выходом первого триггера, а первый и второ информационные входы - соответстве но с выходом второго формирователя импульсов, управляющим входом муль плексора и с выходом первого форми вателя импульсов, входы записи/чте ния первой и второй буферных памятей соединены соответственно с инверсным и прямым выходами первого триггера, а входы сброса - с входо общего сброса устройства, входами 35 сброса первого триггера, входом установки мультиплексора и первыми входами первого, второго и третьег элементов ИЛИ, инверсные выходы вт рого и третьего триггеров соединен соответственно с первым и вторым входами третьего элемента И, выход подключенного к первому входу четвертого элемента ИЛИ, а третьим вх дом - к выходу задержанного импульса первого формирователя импульсов, вх которого подключен к второму входу т тьего элемента ИЛИ, выходу второго элемента И и входу сброса выходного регистра, информационным входом со

40

45

ка и приемника информации, содержащее50 диненного с выходами элементов ИЛИ

первую буферную память, группу элементов ИЛИ, четыре триггера, два элемента И, два элемента ИЛИ, два формирователя импульсов- и выходной регистр, выход которого является выходом устройства для подключения к информационному входу приемника информации, а синхровход соединен

5 , Ш

t5

20

30

25

с выходом задержанного импульса первого формирователя импульсов, причем счетный вход первого триггера соединен с выходом первого элемента И, первый и второй входы которого подключены соответственно к прямым выходам второго и третьего триггеров, выход четвертого триггера подключен к первому входу второго элемента И, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены вторая буферная память, мультиплексор, коммутатор тактов, элемент И и два элемента ИЛИ, причем информационные входы первой и второй буферных памятей подключены соответственно к выходу мультиплексора, а выходы и тактовые входы - соответственно к первым и вторым входам элементов ИЛИ группы и первому и второму выходам коммутатора тактов, управляющий вход которого соединен с прямым выходом первого триггера, а первый и второй информационные входы - соответственно с выходом второго формирователя импульсов, управляющим входом мультиплексора и с выходом первого формирователя импульсов, входы записи/чтения первой и второй буферных памятей соединены соответственно с инверсным и прямым выходами первого триггера, а входы сброса - с входом общего сброса устройства, входами 35 сброса первого триггера, входом установки мультиплексора и первыми входами первого, второго и третьего элементов ИЛИ, инверсные выходы второго и третьего триггеров соединены соответственно с первым и вторым входами третьего элемента И, выходом подключенного к первому входу четвертого элемента ИЛИ, а третьим вхо- дом - к выходу задержанного импульса первого формирователя импульсов, вход которого подключен к второму входу третьего элемента ИЛИ, выходу второго элемента И и входу сброса выходного регистра, информационным входом сое-

40

45

е50 диненного с выходами элементов ИЛИ

группы, вход сброса и установочный вход четвертого триггера подключены соответственно к выходам третьего- и четвертого элементов ИЛИ, а выход является выходом устройства для подключения входа сигнала запроса приема данных приемника информации, вторые входы первого и четвертого элемен513

тов или соединены с вькодом первого элемента И и входом сброса третьего триггера, установочньй вход которого соединен с выходом второго элемента ИЛИ, вторым входом подключенного к выходу сигнала второй буферной памяти, выход сигнала состояния первой буферной памяти подключен к установочному входу второго триггера, входом сброса соединенного с выходом первого элемента ИЛИ, информационные входы мультиплексора и вход второго формирователя импульсов являются

Редактор М.Дылын Заказ 1893/46

Техред Л.Олейник

Тираж 673 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

08276

соответственно входами устройства для подключения информационных выходов и выхода синхронизации источника, информации, выход задержанного им- 5 пульса первого формирователя импуль- сов, второй и третий входы второго элемента И. являются соответственно выходом и входами устройства для подключения входа сигнала сопровождения данных, выхода сигнала выборки байта и выхода сигнала разрешения передачи данных приемника информации.

0

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для передачи и приема данных | 1987 |

|

SU1510105A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1984 |

|

SU1254498A2 |

| Устройство для сопряжения ЭВМ с абонентом | 1988 |

|

SU1615728A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для ввода информации | 1987 |

|

SU1432544A1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

Изобретение относится к области вычислительной техники и может быть использовано в измерительно-вычислительных комплексах и системах регистрации цифровых потоков информации, например, на магнитные носители. Цель изобретения - повьппение быстродействия . Устройство содержит мультиплексор 1, формирователи 2 и 3 импульсов, коммутатор 4 тактов, буферные памяти 5 и 6, группу элементов ИЛИ 7, выходной регистр В, триггеры 9-12, элементы ИЛИ 13-16, элементы 17-19. 1 нл. 00 го

| Авторское свидетельство СССР № 1055267, кл | |||

| С, 06 F 3/04, 1982 | |||

| Шкаф с приспособлением для уборки в него кровати | 1924 |

|

SU1179A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-05-15—Публикация

1984-07-31—Подача