31510

Изобретение относится к технике связи и может использоваться при построении полудуплексных приемопередатчиков цифровой информации.

Цель изобретения - увеличение пропускной способности в полудуплексном режиме работы.

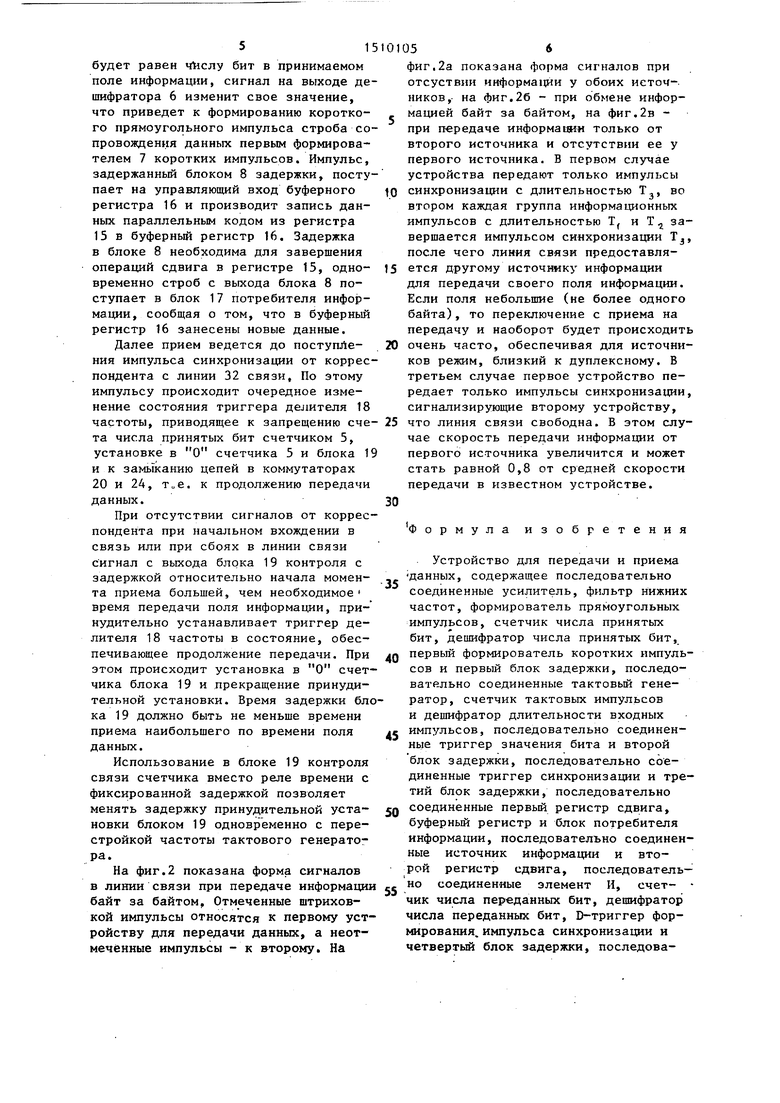

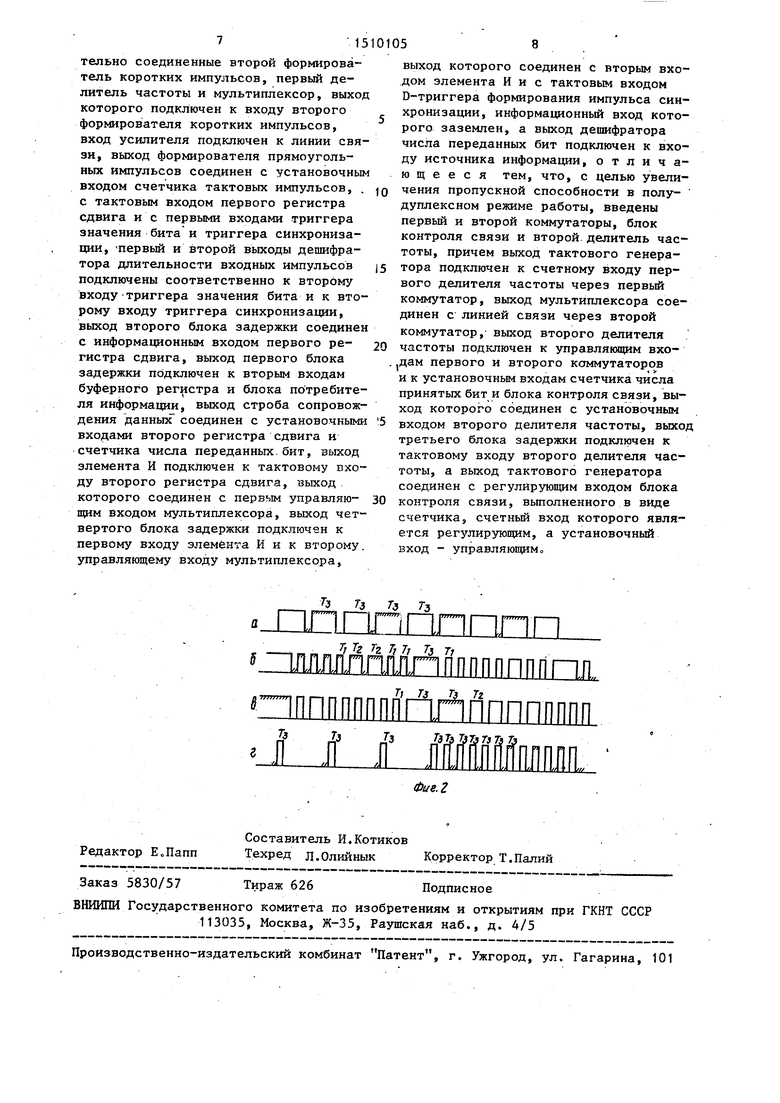

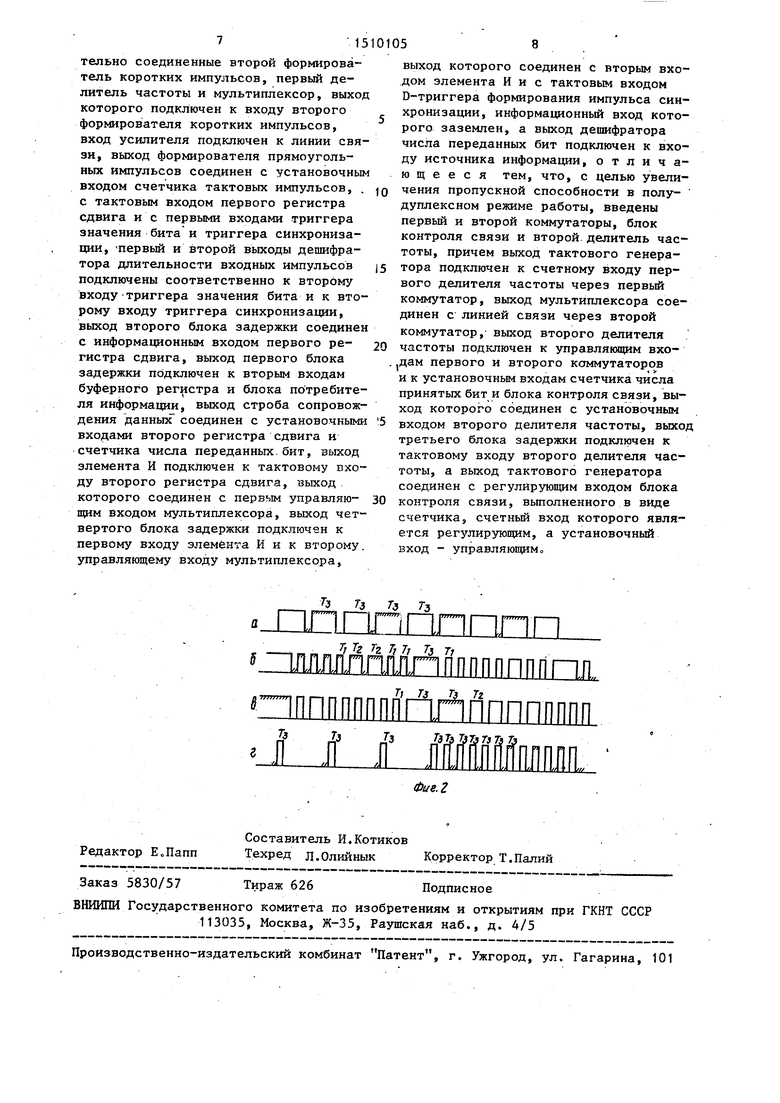

На фиг.1 приведена структурная электрическая схема устройстваj на фиг.2 - временные диаграммы, поясня- кяцие его работу.

Устройство содержит тактовый генератор 1, усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоуголь- ных импульсов, счетчик 5 числа принятых бит, дешифратор 6 числа принятых бит, первый формирователь 7 коротких импульсов, первьм блок 8 задержки, счетчик 9 тактовых импульсов, дешиф- ратор 10 длительности входных импульсов, триггер 11 значения бита, триггер 12 синхронизации, второй 13 и третий 14 блоки задержки, первый регистр 15 сдвига, буферный регистр 16 блок 17 потребителя информации, второй делитель 18 частоты, блок 19 контроля связи, первый коммутатор 20, второй регистр 21 сдвига, первый делитель 22 частоты, мультиплексор 23, второй коммутатор 24, элемент И 25, четвертый блок 26 задержки, второй формирователь 27 коротких импульсов, счетчик 28 числа переданных бит, дешифратор 29 числа переданных бит, D-триггер 30 формирования импульса синхронизации, источник 31 информации, линию 32 связи.

Устройство работает следующим образом.

Делитель 22 частоты делит входную частоту тактового генератора 1 и формирует три последовательности импульсов различной длительности, поступающие на входы мультиплексора 23. Вы- бор последовательности импульсов и их длительность на выходе мультиплексора 23 зависит от значения сигналов на его управляющих входах. С помощью формирователя 27 коротких импульсов по заднему фронту каждого импульса происходит сброс счетчиков делителя 22 частоты для получения импульсов со скважностью 1/2. Данные от источника 31 информации записываются в параллельном коде в регистр 21. Строб сопровождения данных устанавливает в О счетчик 28 бит. Очередным задним фронтом импульса с. выхода мультиплексора 23 D-триггер 30 устанавливается в состояние, разрешающее через элемент И 25 выполнение сдвига в регистре 21 и счет числа переданных бит счетчиком 28. Кроме того, на управляющем входе мультиплексора 23 устанавливается зна чение сигнала, обеспечивающее формирование импульсов длительностью Т и Т в зависимости от значения сигнала на выходе регистра 21. После передачи всех бит данных в счетчике 28 устанавливается код, равный числу передаваемых бит, и на выходе дешифратора 29 появляется сигнал готовности к передаче очередного поля данных, поступающий к источнику 31 информации. Этим сигналом D-триггер 30 устанавливается в состояние, обеспечивающее формирование мультиплексором 23 импульсов синхронизации длительностью Т.

С выхода мультиплексора 23 через коммутатор 24 импульсы поступают в линию 32 связи и на вход усилителя 2. Усиленный аналоговый сигнал посту- |пает через фильтр 3 нижних частот, необходимый для защиты от высокочастотных помех, на формирователь 4 прямоугольных импульсов. Определение длительности принятых импульсов осуществляется счетчиком 9 и дещифра- тором 10. При поступлении импульса синхронизации на первом и втором выходах дешифратора 10, соответствующих 0, 0,75Тз при ,j:Tj 1:2:4, появляются импульсы, устанав- ливаняцие триггеры 11 и 12 в состояние 1. Сброс триггеров 11 и 12 происходит в моменты времени, когда наступает пауза между импульсами. По заднему фронту импульса синхронизации с выхода блока 14 задержки происходит переход триггера делителя 18 частоты в инверсное состояние и разрыв цепи коммутаторами 20 и 24, т.е. прекращение передачи данных. Одновременно выдается разрешение на счет счетчику 5 принятых бит и счетчику блока 19 контроля связи.

При поступлении сигнала от корреспондента с линии 32 связи осуществляется определение длительности поступающих импульсов счетчиком 9, дешифратором 10, триггерами 11 и 12 и последовательная запись значения принятых бит в регистр 15 по заднему фронту импульсов. После того, как код в счетчике 5 числа принятых бит

будет равен бит в принимаемом поле информации, сигнал на выходе дешифратора 6 изменит свое значение, что приведет к формированию короткого прямоугольного импульса строба сопровождения данных первым формирователем 7 коротких импульсов. Импульс, задержанный блоком 8 задержки, поступает на управляющий вход буферного регистра 16 и производит запись данных параллельным кодом из регистра 15 в буферный регистр 16. Задержка в блоке 8 необходима для завершения операций сдвига в регистре 15, одновременно строб с выхода блока 8 поступает в блок 17 потребителя информации, сообщая о том, что в буферный регистр 16 занесены новые данные.

Далее прием ведется до поступления импульса синхронизации от корреспондента с линии 32 связи. По этому импульсу происходит очередное изменение состояния триггера делителя 18 частоты, приводящее к запрещению счета числа принятых бит счетчиком 5, установке в О счетчика 5 и блока 19 и к замьТканию цепей в коммутаторах 20 и 24, т„е. к продолжению передачи данных.

При отсутствии сигналов от корреспондента при начальном вхождении в связь или при сбоях в линии связи сигнал с выхода блока 19 контроля с задержкой относительно начала момента приема большей, чем необходимое время передачи поля информации, принудительно устанавливает триггер делителя 18 частоты в состояние, обеспечивающее продолжение передачи. При этом происходит установка в О счетчика блока 19 и прекращение принудительной установки. Время задержки блока 19 должно быть не меньше времени приема наибольшего по времени поля данных.

Использование в блоке 19 контроля связи счетчика вместо реле времени с фиксированной задержкой позволяет менять задержку принудительной установки блоком 19 одновременно с перестройкой частоты тактового генератора.

На фиг.2 показана форма сигналов в линии связи при передаче информации байт за байтом, Отмеченные штриховкой импульсы относятся к первому устройству для передачи данных, а неотмеченные импульсы - к второму. На

фиг,2а показана форма сигналов при отсуствии информации у обоих источников,- на фиг.26 - при информацией байт за байтом, на фиг.2в - при передаче информацией только от второго источника и отсутствии ее у первого источника. В первом случае устройства передают только импульсы

синхроннзахщи с длительностью Т, во втором каждая группа информационных импульсов с длительностью Т и Т завершается импульсом синхронизации Т, после чего линия связи предоставляется другому источ1даку информации для передачи своего поля информации. Если поля небольшие (не более одного байта), то переключение с приема на передачу и наоборот будет происходить

очень часто, обеспечивая для источников режим, близкий к дуплексному. В третьем случае первое устройство передает только импульсы синхронизации, сигнализирующие второму устройству,

что линия связи свободна. В этом случае скорость передачи информации от первого источника увеличится и может стать равной 0,8 от средней скорости передачи в известном устройстве.

формула изобретения

5

Устройство для передачи и приема данных, содержащее последовательно соединенные усилитель, фильтр нижних частот, формирователь прямоугольных импульсов, счетчик числа принятых бит, дешифратор числа принятых бит,

д первый формирователь коротких импульсов и первый блок задержки, последовательно соединенные тактовый генератор, счетчик тактовых импульсов и дешифратор длительности входных

e импульсов, послвдовательно соединенные триггер значения бита и второй блок задержки, последовательно соединенные триггер синхронизации и третий блок задержки, последовательно

g соединенные первьй регистр сдвига, буферный регистр и блок потребителя информации, последовательно соединенные источник информации и вто- рой регистр сдвига, последователь- , но соединенные элемент И, счет- - чик числа переданных бит, дешифратор числа переданных бит, D-триггер формирования, импульса синхронизации и четвертый блок задержки, последовательно соединенные второй формирователь коротких импульсов, первый делитель частоты и мультиплексор, выход которого подключен к входу второго формирователя коротких импульсов, вход усилителя подключен к линии связи, выход формирователя прямоугольных импульсов соединен с установочным входом счетчика тактовых импульсов, . с тактовым входом первого регистра сдвига и с первыми входами триггера значения бита и триггера синхронизации, -первый и второй выходы дешифратора длительности входных импульсов подключены соответственно к второму входу триггера значения бита и к второму входу триггера синхронизации, выход второго блока задержки соединен с информационным входом первого ре- гистра сдвига, выход первого блока задержки подключен к вторым входам буферного репнстра и блока потребителя информацииi выход строба сопровождения данных соединен с установочными входами второго регистра сдвига и счетчика числа переданных.бит, выход элемента И подключен к тактовому входу второго регистра сдвига, выход которого соединен с первым управляю- щим входом мультиплексора, выход четвертого блока задержки подключен к первому входу элемента Инк второму управляющему входу мультиплексора.

выход которого соединен с вторым входом элемента И и с тактовым входом D-триггера формирования импульса синхронизации, информационный вход которого заземлен, а выход дешифратора числа переданных бит подключен к входу источника информации, отличающееся тем, что, с целью увеличения пропускной способности в полудуплексном режиме работы, введены первый и второй коммутаторы, блок контроля связи и второй, делитель частоты, причем выход тактового генератора подключен к счетному входу первого делителя частоты через первый коммутатор, выход мультиплексора соединен с линией связи через второй коммутатор, выход второго делителя частоты подключен к управляющим входам первого и второго ксгммутаторов и к установочным входам счетчика числа принятых бит и блока контроля связи, выход которого соединен с установочным входом второго делителя частоты, выхо третьего блока задержки подключен к тактовому входу второго делителя частоты, а выход тактового генератора соединен с регулирующим входом блока контроля связи, выполненного в виде счетчика, счетный вход которого является регулирующим, а установочный вход - управляющим

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи и приема данных в полудуплексном режиме | 1990 |

|

SU1732485A1 |

| Устройство для передачи и приема данных | 1990 |

|

SU1786678A1 |

| Устройство для приема и передачи данных в дуплексном режиме | 1987 |

|

SU1506576A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1748276A1 |

| Устройство для приема и передачи двоичной информации | 1984 |

|

SU1748275A1 |

| Устройство для приема и передачи данных | 1989 |

|

SU1688438A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1665529A1 |

| Устройство для передачи информации | 1990 |

|

SU1753615A1 |

| Устройство для передачи и приема данных | 1989 |

|

SU1721836A2 |

| Устройство для передачи и приема данных | 1988 |

|

SU1589417A1 |

Изобретение относится к технике связи. Цель изобретения - увеличение пропускной способности устройства в полудуплексном режиме работы. Устройство содержит тактовый генератор 1, усилитель 2, фильтр 3 нижних частот, формирователь 4 прямоугольных импульсов, счетчики 5 и 28 числа принятых и переданных бит, дешифраторы 6 и 29 числа принятых и переданных бит, формирователи 7 и 27 коротких импульсов, блоки 8,13,14 и 26 задержки, счетчик 9 тактовых импульсов, дешифратор 10 длительности входных импульсов, триггер 11 значения бита, триггер 12 синхронизации, регистры 15 и 21 сдвига, буферный регистр 16, блок потребителя 17 информации, делители 18 и 22 частоты, блок 19 контроля связи, коммутаторы 20 и 24, мультиплексор 23, элемент И 25, Д-триггер 30 формирования импульса синхронизации, источник 31 информации и линию связи 32. Цель достигается за счет увеличения скорости передачи информации от источника 31 с помощью введенных делителя 18, блока 19 контроля связи и коммутаторов 20 и 24, обеспечивающих либо прекращение передачи данных, либо ее продолжение. 2 ил.

| Сурнин АоИо, Савельев А.И | |||

| Способ получения молочной кислоты | 1922 |

|

SU60A1 |

| Серия препринтов сообщений Автоматизация научных исследований | |||

| - Сыктывкар: Коми филиал АН СССР, 1984, Соб-10, рис.3 | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-09-23—Публикация

1987-07-21—Подача