ной памяти, состоящего из регистров 14. Многокоординатньш цифровой интерполятор содержит также блок 4 двухкоординатной интерполяции, счетчик 13 перемещений. Устройство позволяет осуществить многокоординатную интерполяцию на одном двухкоор- динатном блоке интерполяции. Возможность же организовать выход тактовоИзобретение относится к автоматике и вычислительной технике и может быть использовано в системах ЧПУ станками.

Цель изобретения - повьшение быстродействия интерполятора.

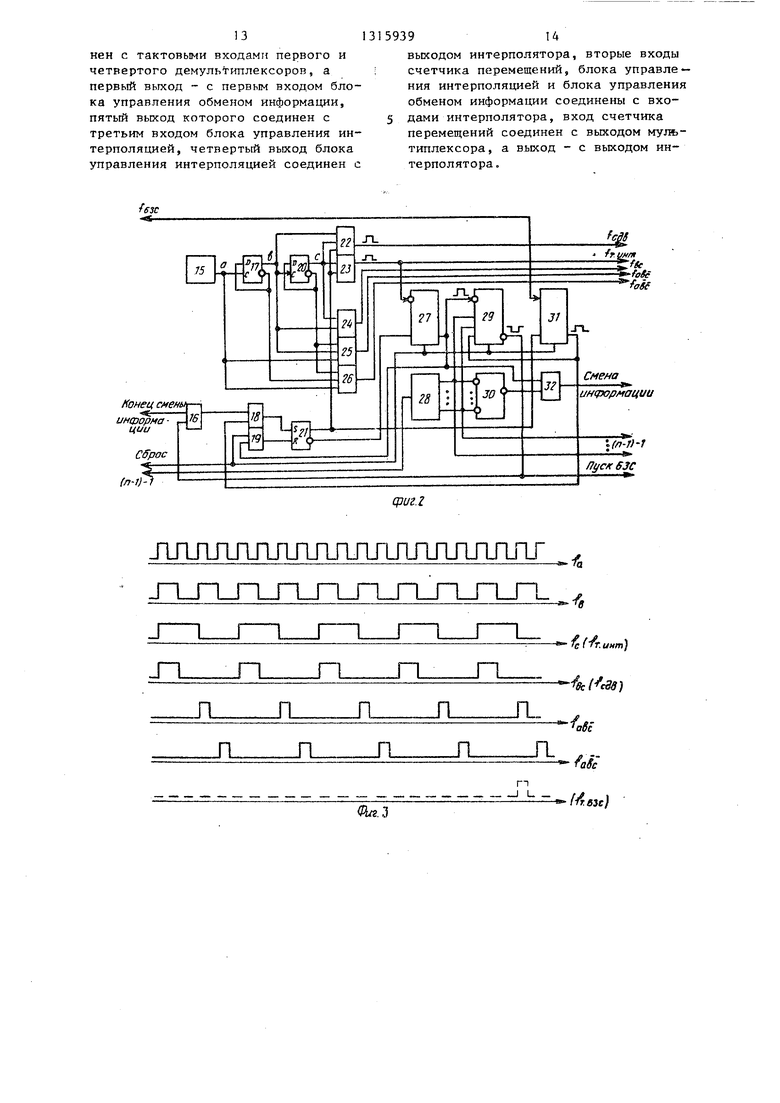

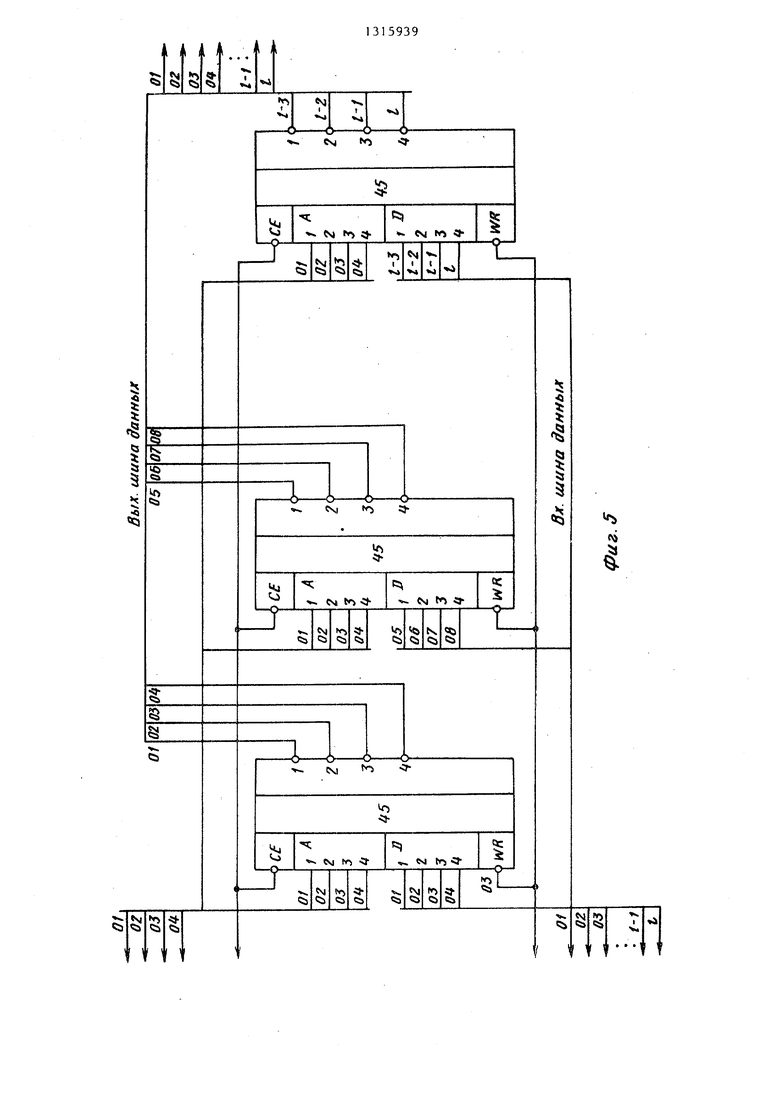

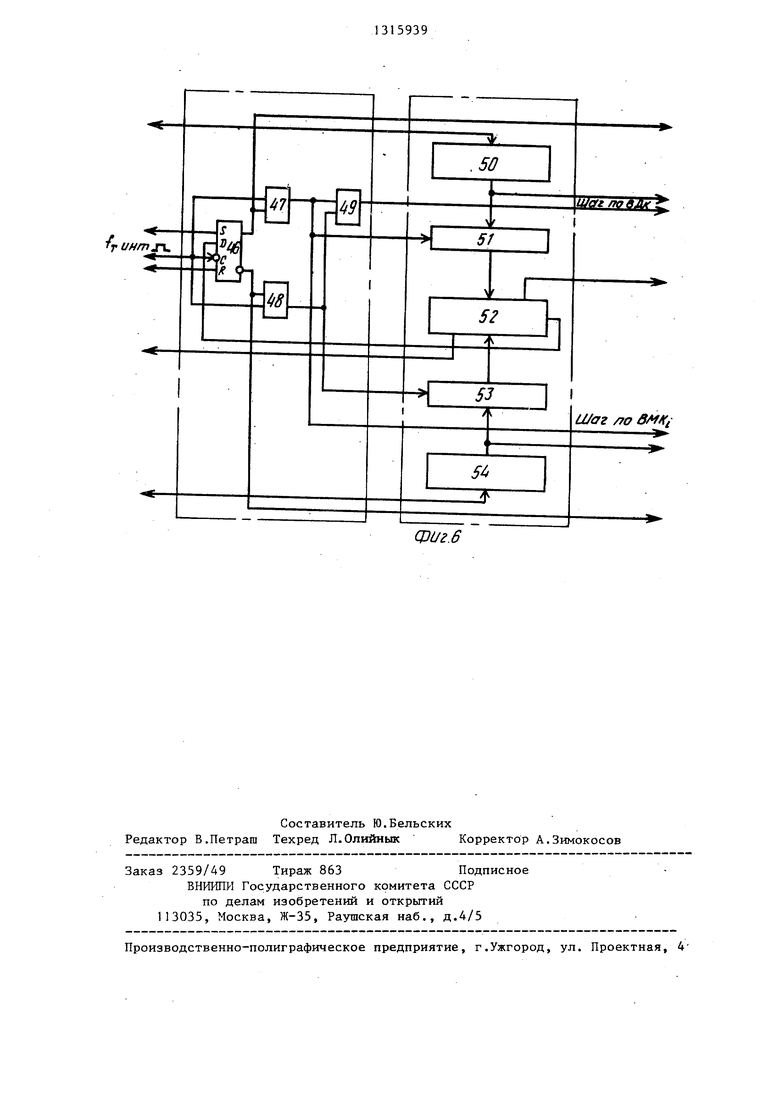

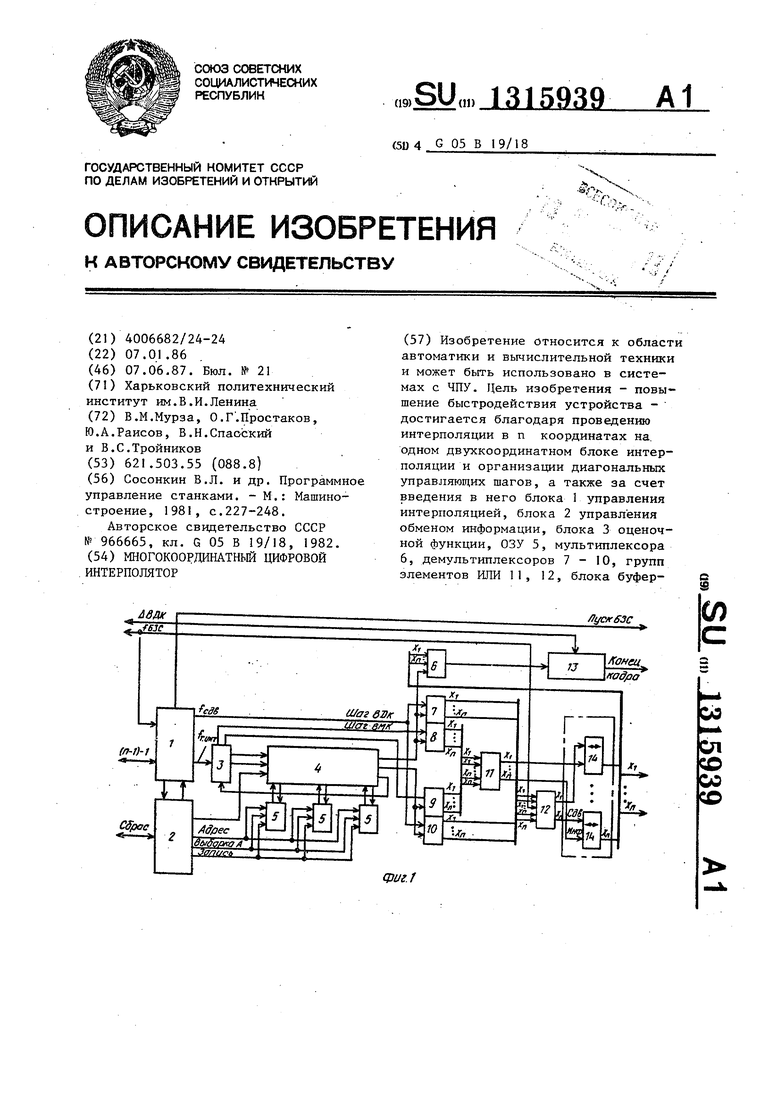

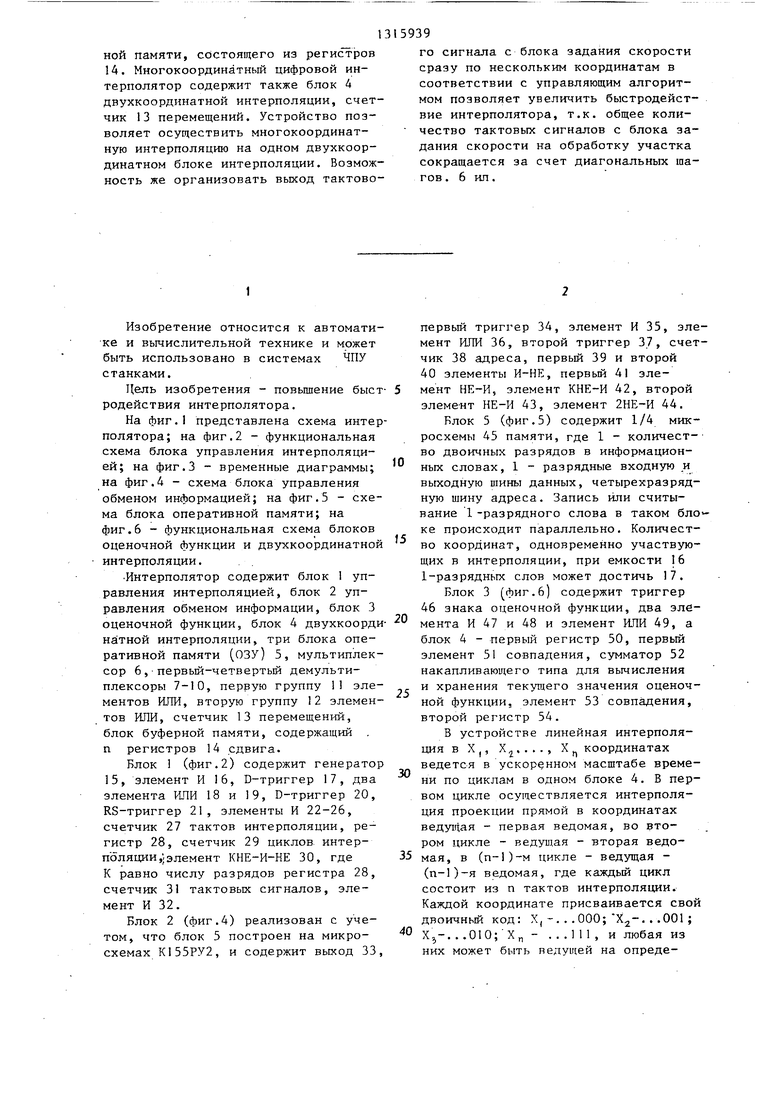

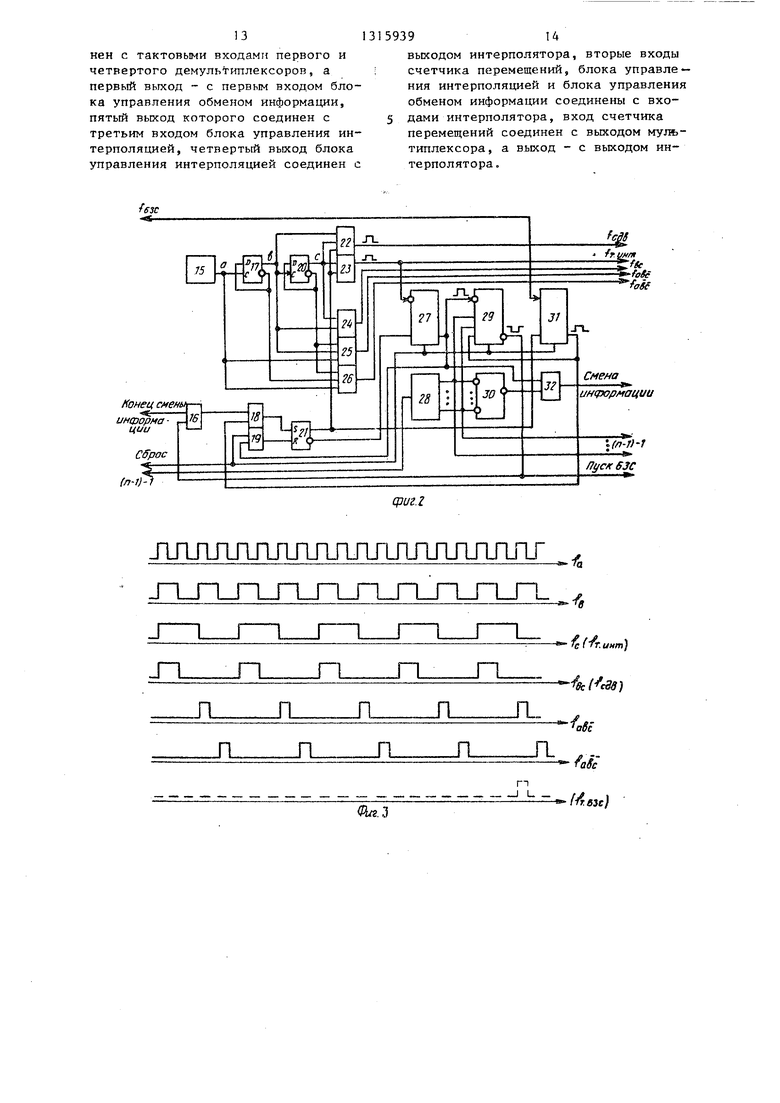

На фиг.1 представлена схема интерполятора; на фиг.2 - функциональная схема блока управления интерполяцией; на фиг.З - временные диаграммы; на фиг.4 - схема блока управления обменом информацией; на фиг.5 - схема блока оперативной памяти; на фиг.6 - функциональная схема блоков оценочной функции и двухкоординатной интерполяции.

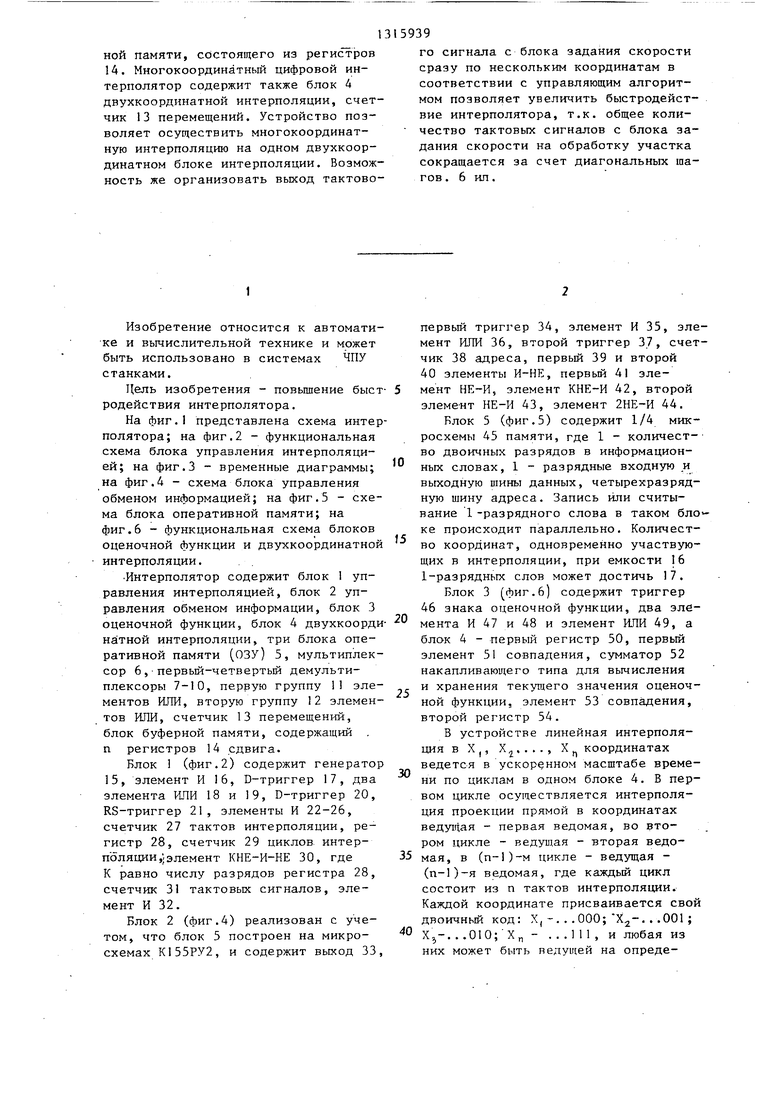

Интерполятор содержит блок 1 управления интерполяцией, блок 2 управления обменом информации, блок 3 оценочной функции, блок 4 двухкоординатной интерполяции, три блока оперативной памяти (ОЗУ) 5, мультиплексор 6,первый-четвертый демульти- плексоры 7-10, первую группу И элементов ИЛИ, вторую группу 12 элементов ИЛИ, счетчик 13 перемещений, блок буферной памяти, содержащий . п регистров 14 сдвига.

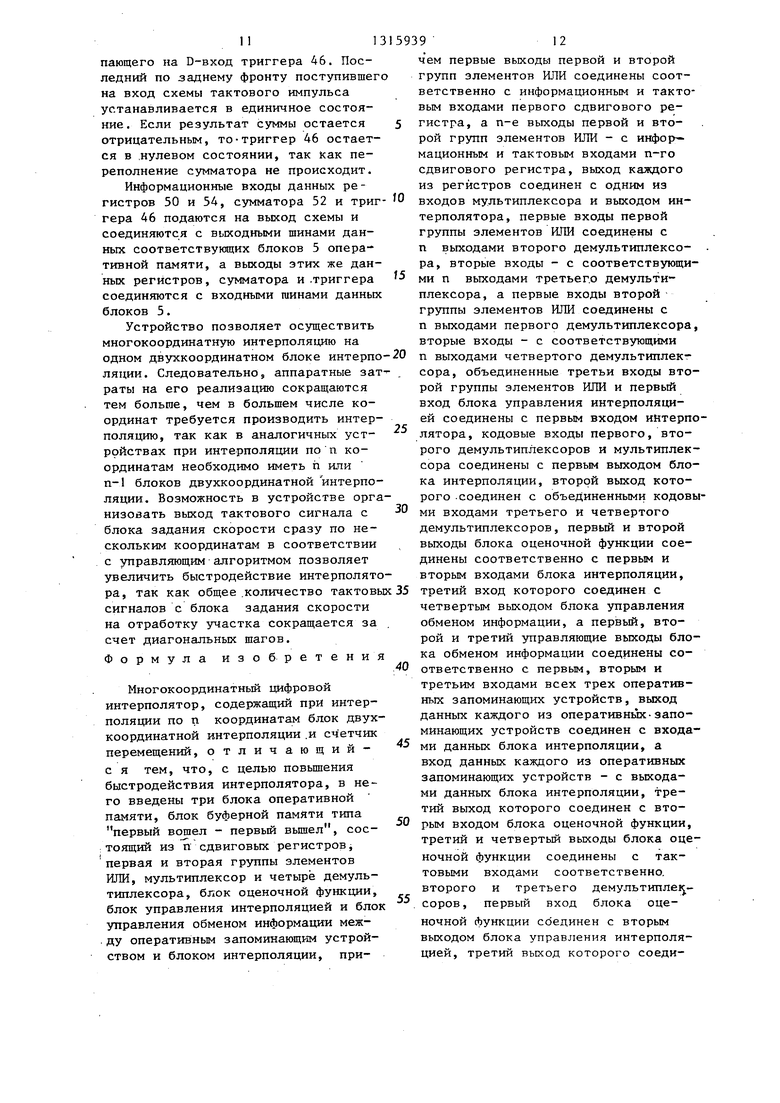

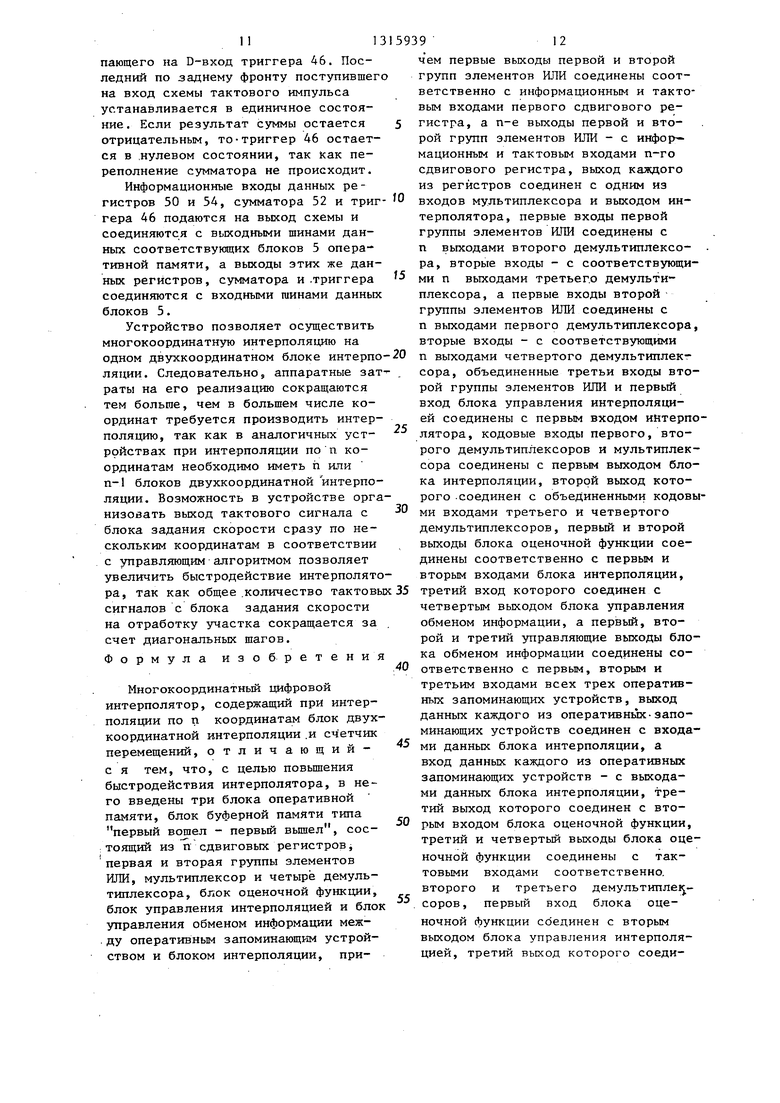

Блок 1 (фиг.2) содержит генератор 15, элемент И 16, D-триггер 17, два элемента ИЛИ 18 и 19, D-триггер 20, RS-триггер 21, элементы И 22-26, счетчик 27 тактов интерполяции, регистр 28, счетчик 29 циклов интерполяции,; элемент КНЕ-И-НЕ 30, где К равно числу разрядов регистра 28, счетчик 31 тактовых сигналов, элемент И 32.

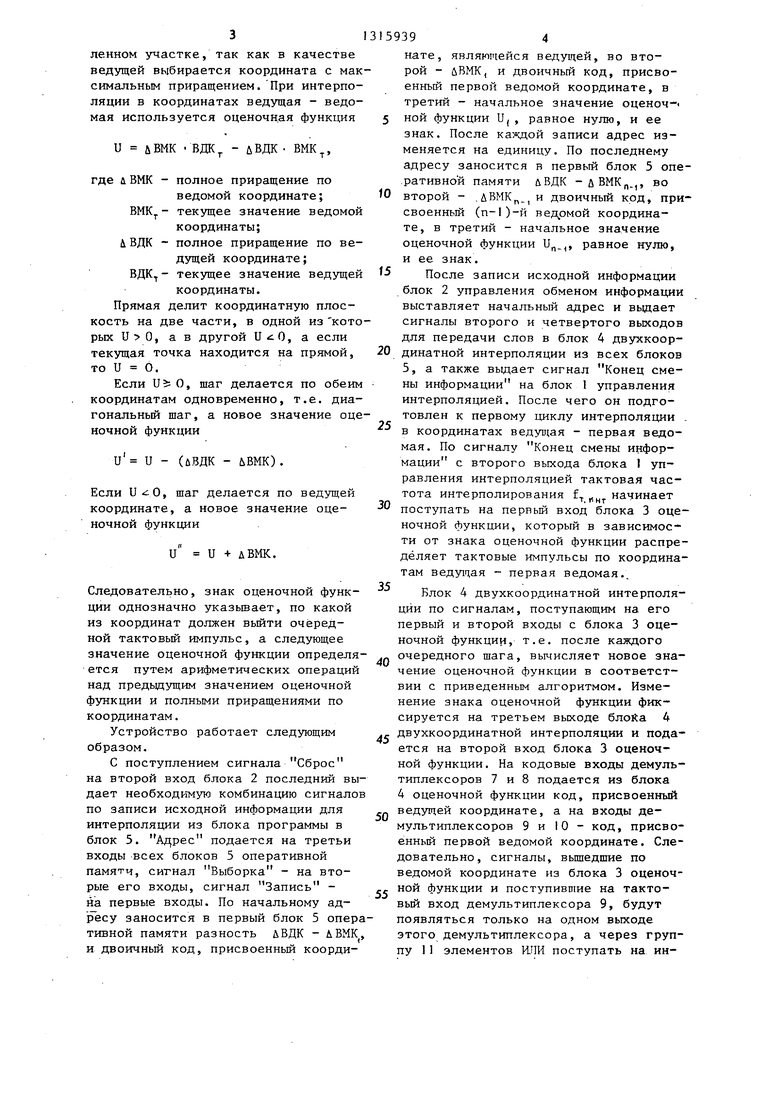

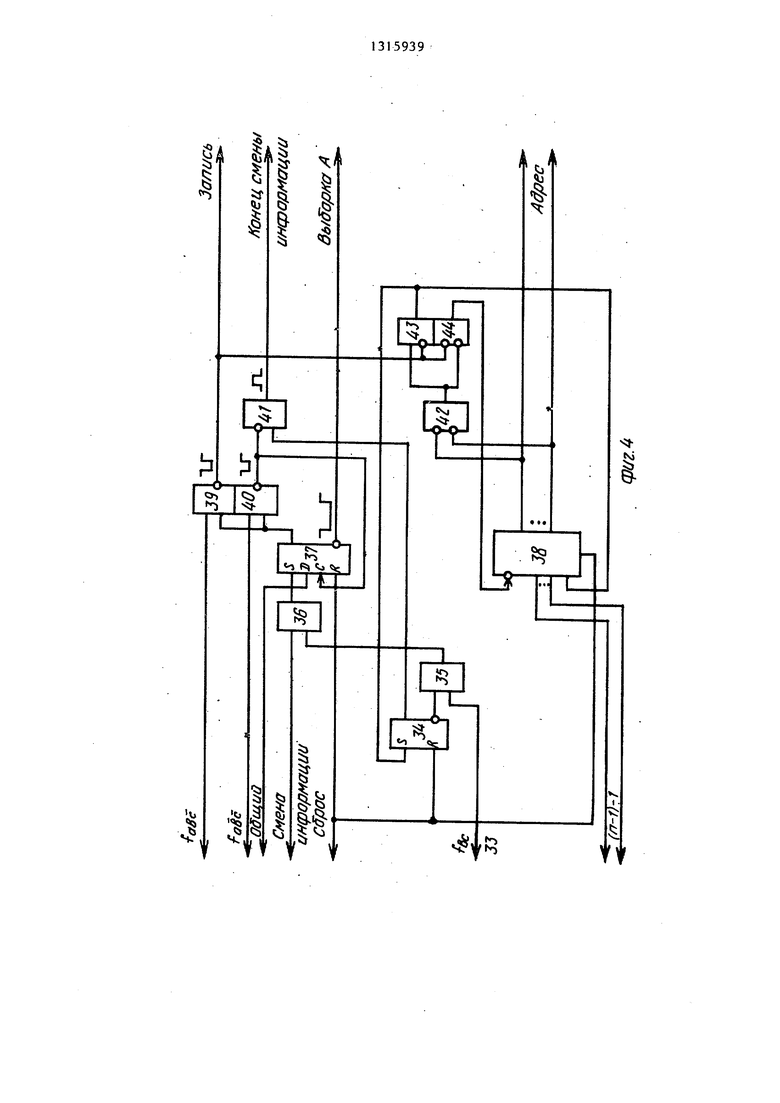

Блок 2 (фиг.4) реализован с учетом, что блок 5 построен на микросхемах К155РУ2, и содержит выход 33,

5939

го сигнала с блока задания скорости сразу по нескольким координатам в соответствии с управляющим алгоритмом позволяет увеличить быстродействие интерполятора, т.к. общее коли чество тактовых сигналов с блока задания скорости на обработку участка сокращается за счет диагональных шагов . 6 ил.

5

0

5

0

5

0

первый триггер 34, элемент И 35, элемент ИЛИ 36, второй триггер 37, счетчик 38 адреса, первый 39 и второй 40 элементы И-НЕ, первый 41 элемент НЕ-И, элемент КНЕ-И 42, второй элеме-нт НЕ-И 43, элемент 2НЕ-И 44.

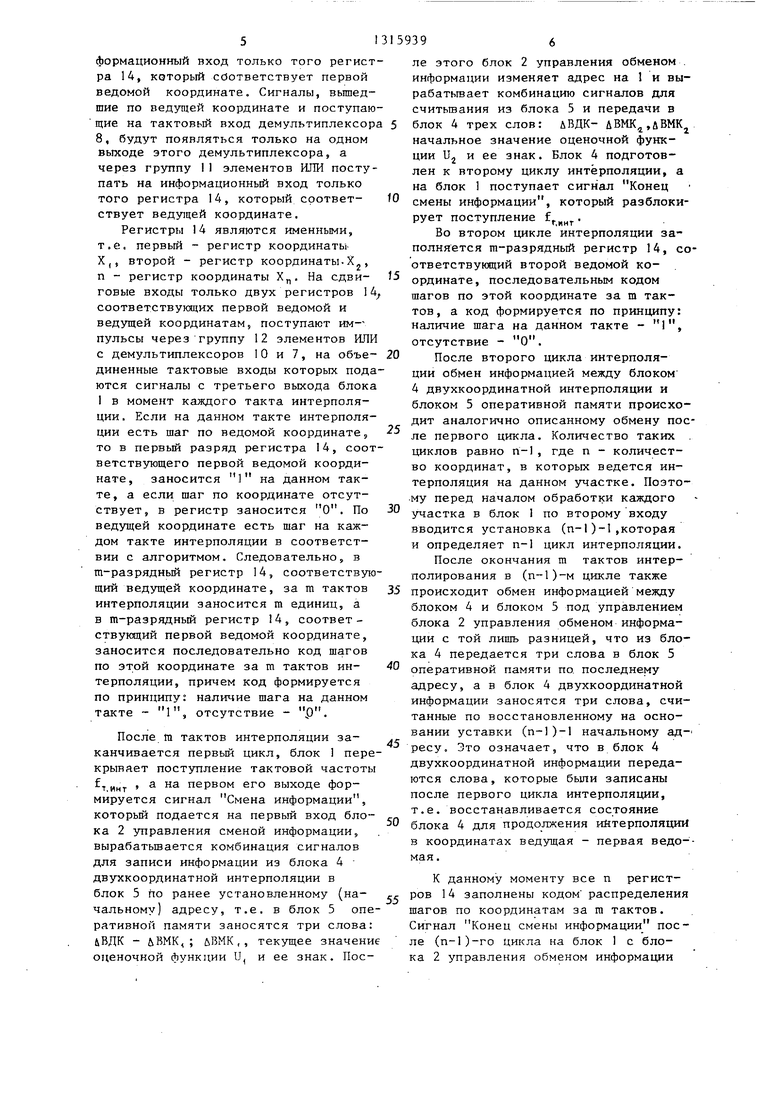

Блок 5 (фиг.5) содержит 1/4 микросхемы 45 памяти, где 1 - количество двоичных разрядов в информационных словах, 1 - разрядные входную и выходную шины данных, четырехразрядную шину адреса. Запись или считывание 1-разрядного слова в таком блo ке происходит параллельно. Количество координат, одновременно участвующих в интерполяции, при емкости 16 1-разрядньгх слов может достичь 17.

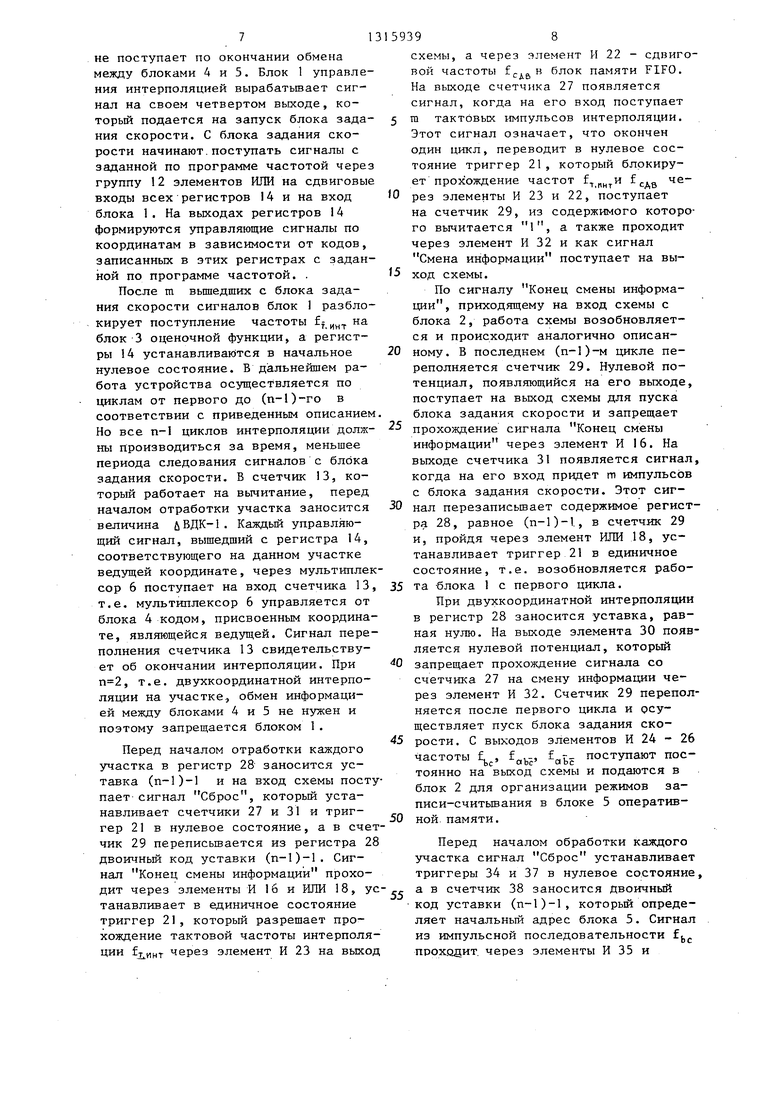

Блок 3 фиг.б содержит триггер 46 знака оценочной функции, два элемента И 47 и 48 и элемент ИЛИ 49, а блок 4 - первый регистр 50, первый элемент 51 совпадения, сумматор 52 накапливающего типа для вычисления и хранения текущего значения оценочной функции, элемент 53 совпадения, второй регистр 54.

В устройстве линейная интерполяция в X,, Х,...., Х координатах ведется в ускоренном масштабе времени по циклам в одном блоке 4. В первом цикле осуществляется интерполяция проекции прямой в координатах ведутцая - первая ведомая, во втором цикле - ведущая - вторая ведомая, в (п-1)-м цикле - ведущая - (п-1)-я ведомая, где каждый цикл состоит из п тактов интерполяции. Каждой координате присваивается свой двоичный код: X,-...000; Х -...001; X,,-. ..010; Х„ - ...111, и любая из них может быть ведущей на определенном участке, так как в качестве ведущей выбирается координата с максимальным приращением. При интерполяции в координатах ведущая - ведомая используется оценочная функция

и йВМК ВДК - йВДК

ВМК.

где л ВМК - полное приращение по

ведомой координате; текущее значение ведомой

координаты;

iВДК - полное приращение по ведущей координате; текущее значение ведущей

координаты.

Прямая делит координатную плоскость на две части, в одной из которых и О, а в другой и ;0, а если текущая точка находится на прямой, то и О.

Если и5: О, шаг делается по обеим координатам одновременно, т.е. диагональный щаг, а новое значение оценочной функции

и и - (йВДК - ЬВМК).

Если V 0, шаг делается по ведущей координате, а новое значение оценочной функции

и

и + двмк.

Следовательно, знак оценочной функции однозначно указьшает, по какой из координат должен выйти очередной тактовый импульс, а следующее значение оценочной функции определяется путем арифметических операций над предьщущим значением оценочной функции и полными приращениями по координатам.

Устройство работает следующим образом.

С поступлением сигнала Сброс на второй вход блока 2 последний выдает необходимую комбинацию сигналов по записи исходной информации для интерполяции из блока программы в блок 5. подается на третьи входы всех блоков 5 оперативной памяти, ситнал Выборка - на вторые его входы, сигнал Запись - На первые входы. По начальному адресу заносится в первый блок 5 оперативной памяти разность ЛВДК - АВМК и двоичный код, присвоенный коорди5

нате, являю1цейся ведущей, во второй - йВМК, и двоичный код, присвоенный первой ведомой координате, в третий - начальное значение оценоч-

ной функции и,, равное нулю, и ее знак. После каждой записи адрес изменяется на единицу. По последнему адресу заносится в первый блок 5 опе- .ративно й памяти йВДК - и ВИК.,, во

О второй - .йВМК и двоичный код, присвоенный (п-)-й координате, в третий - начальное значение оценочной функции U,, равное нулю, и ее знак.

5 После записи исходной информации блок 2 управления обменом информации выставляет начальный адрес и выдает сигналы второго и четвертого выходов для передачи слов в блок 4 двухкоор0 динатной интерполяции из всех блоков 5, а также вьщает сигнал Конец смены информации на блок 1 управления интерполяцией. После чего он подготовлен к первому циклу интерполяции . в координатах ведущая - первая ведомая. По сигналу Конец смены информации с второго выхода &лрка 1 управления интерполяцией тактовая частота интерполирования f.. „., начинает

Лт, п н т

поступать на первьй вход блока 3 оценочной функции, который в зависимости от знака оценочной функции распределяет тактовые импульсы по координатам веду1цая - первая ведомая..

Блок 4 двухкоординатной интерполяции по сигналам, поступающим на его первый и второй входы с блока 3 оценочной функции, т.е. после каждого очередного шага, вычисляет новое значение оценочной функции в соответствии с приведенным алгоритмом. Изменение знака оценочной функции фиксируется на третьем вьсходе блоАа 4 двухкоординатной интерполяции и подается на второй вход блока 3 оценочной функции. На кодовые входы демуль- типлексоров 7 и 8 подается из блока 4 оценочной функции код, присвоенный ведущей координате, а на входы де- мультиплексоров 9 и 10 - код, присвоенный первой ведомой координате. Следовательно, сигналы, вьш1ед11ше по ведомой координате из блока 3 оценочной функции и поступившие на тактовый вход демультиплексора 9, будут появляться только на одном выходе этого демультиплексора, а через группу 11 элементов Ш1И поступать на ин0

5

5

формационный вход только того регистра 14, который соответствует первой ведомой координате. Сигналы, вышедшие по ведущей координате и поступаю- ие на тактовый вход демультиплексора 5 8, будут появляться только на одном выходе этого демультиплексора, а через группу 11 элементов ИЛИ поступать на информационный вход только того регистра 14, который соответствует ведущей координате.

Регистры 14 являются именными, т.е. первый - регистр координатыfO

X., второй - регистр координаты-X,

( п

регистр координаты Х„, На сдвиговые входы только двух регистров 14 соответствующих первой ведомой и ведущей координатам, поступают им- пульсы через группу 12 элементов ИЛИ с демультиплексоров 10 и 7, на объе- диненные тактовые входы которых подаются сигналы с третьего выхода блока 1 в момент каждого такта интерполяции. Если на данном такте интерполяции есть шаг по ведомой координате, то в первый разряд регистра I4, соответствующего первой ведомой координате, заносится 1 на данном такте, а если шаг по координате отсутствует, в регистр заносится О. По ведущей координате есть шаг на каждом такте интерполяции в соответствии с алгоритмом. Следовательно,, в т-разрядный регистр 14, соответствующий ведущей координате, за га тактов интерполяции заносится m единиц, а в т-разрядный регистр 14, соответ- ствукядий первой ведомой координате, заносится последовательно код шагов по этой координате за га тактов интерполяции, причем код формируется по принципу: наличие шага на данном такте 1, отсутствие - Р.

После и тактов интерполяции заканчивается первый цикл, блок перекрывает поступление тактовой частоты ff , а на первом его выходе формируется сигнал Смена информации, которьй подается на первый вход блока 2 управления сменой информации, вырабатьшается комбинация сигналов для записи информации из блока 4 - двухкоординатной интерполяции в блок 5 по ранее установленному (начальному) адресу, т.е. в блок 5 оперативной памяти заносятся три слова: &ВДК - &ВМК,; ьВМК , , текущее значение оценочной функции U и ее знак. Пос5 fO

)5

20

ле этого блок 2 управления обменом . информации изменяет адрес на 1 и вы- рабатьгеает комбинацию сигналов для считьшания из блока 5 и передачи в блок 4 трех слов: лВДК- йВМК,дВМК начальное значение оценочной функции Uj и ее знак. Блок 4 подготовлен к второму циклу интерполяции, а на блок 1 поступает сигнаш Конец смены информации, который разблокирует поступление втором цикле интерполяции заполняется т-разрядный регистр 14, соответствующий второй ведомой координате, последовательньм кодом шагов по этой координате за m тактов, а код формируется по принципу: наличие шага на данном такте - 1, отсутствие - О.

После второго цикла интерполяции обмен информацией между блоком 4 двухкоординатной интерполяции и блоком 5 оперативной памяти происходит аналогично описанному обмену после первого цикла. Количество таких . циклов равно п-1, где п - количество координат, в которых ведется интерполяция на данном участке. Поэтому перед началом обработки каждого участка в блок 1 по второму входу вводится установка (п-1)-1,которая и определяет п-1 цикл интерполяции.

После окончания m тактов интерполирования в (п-1)-м цикле также 35 происходит обмен информацией между блоком 4 и блоком 5 под управлением блока 2 управления обменом информации с той лишь разницей, что из блока 4 передается три слова в блок 5 оперативной памяти по. последнему адресу, а в блок 4 двухкоординатной информации заносятся три слова, считанные по восстановленному на основании уставки (n-l)-l начальному ад- ресу. Это означает, что в блок 4 двухкоординатной информации передаются слова, которые были записаны после первого цикла интерполяции, т.е. восстанавливается состояние 0 блока 4 для продолжения ийтерполяции в координатах ведущая - первая ведо-- мая.

30

40

45

К данному моменту все п регистров 14 заполнены кодом распределения шагов по координатам за m тактов. Сигнал Конец смены информации после (п-1)-го цикла на блок 1 с блока 2 управления обменом информации

71

не поступает по окончании обмена между блоками 4 и 5. Блок 1 управления интерполяцией вырабатьшает сигнал на своем четвертом выходе, который подается на запуск блока задания скорости. С блока задания скорости начинают.поступать сигналы с заданной по программе частотой через группу 12 элементов ИЛИ на сдвиговые входы всех регистров 14 и на вход блока 1. На вькодах регистров 14 формируются управляющие сигналы по координатам в зависимости от кодов, записанных в этих регистрах с заданной по программе частотой. .

После m вышедших с блока задания скорости сигналов блок 1 разблокирует поступление частоты ff. „ на блок 3 оценочной функции, а регистры 14 устанавливаются в начальное нулевое состояние. В д1альнейшем работа устройства осуществляется по циклам от первого до (n-l)-ro в соответствии с приведенным описанием Но все п-1 циклов интерполяции должны производиться за время, меньшее периода следования сигналов с блока задания скорости. В счетчик 13, который работает на вычитание, перед началом отработки участка заносится величина йВДК-1. Каждый управляющий сигнал, вышедший с регистра 14, соответствующего на данном участке ведущей координате, через мультиплексор 6 поступает на вход счетчика 13, т.е. мультиплексор 6 управляется от блока 4 кодом, присвоенным координате, являющейся ведущей. Сигнал переполнения счетчика 13 свидетельствует об окончании интерполяции. При , т.е. двухкоординатной интерполяции на участке., обмен информацией между блоками 4 и 5 не нужен и поэтому запрещается блоком 1.

Перед началом отработки каждого участка в регистр 28 заносится уставка (п-1)-1 и на вход схемы поступает сигнал Сброс, который устанавливает счетчики 27 и 31 и триггер 21 в нулевое состояние, а в счетчик 29 переписьшается из регистра 28 двоичный код уставки (n-l)-l. Сигнал Конец смены информации проходит через элементы И I б и ИЛИ 18, устанавливает в единичное состояние триггер 21, который разрешает прохождение тактовой частоты интерполяции через элемент И 23 на выход

159398

схемы, а через элемент И 22 - сдвиговой частоты fр... в блок памяти FIFO.

д ti

На выходе счетчика 27 появляется сигнал, когда на его вход поступает 5 га тактовых импульсов интерполяции. Этот сигнал означает, что окончен один цикл, переводит в нулевое состояние триггер 21, который блокирует прохождение частот f-„ и ,.„ чет.пнт AD

и рез элементы И 23 и 22, поступает на счетчик 29, из содержимого которого вычитается 1, а также проходит через элемент И 32 и как сигнал Смена информации поступает на вы15

ход схемы.

По сигналу Конец смены информации , приходящему на вход схемы с блока 2, работа схемы возобновляется и происходит аналогично описанному. В последнем (п-1)-м цикле переполняется счетчик 29. Нулевой потенциал, появляющийся на его выходе, поступает на выход схемы для пуска блока задания скорости и запрещает

прохождение сигнала Конец смены информации через элемент И 16. На выходе счетчика 31 появляется сигнал, когда на его вход придет m импульсов с блока задания скорости. Этот сигнал перезаписьшает содержимое регистра 28, равное (п-1)-1,, в счетчик 29 и, пройдя через элемент ИЛИ 18, устанавливает триггер 21 в единичное состояние, т.е. возобновляется работа -блока 1 с первого цикла.

При двухкоординатной интерполяции в регистр 28 заносится уставка, равная нулю. На выходе элемента 30 появляется нулевой потенциал, который

запрещает прохождение сигнала со счетчика 27 на смену информации через элемент И 32. Счетчик 29 переполняется после первого цикла и осуществляет пуск блока задания скорости. С выходов элементов И 24 - 26 частоты , fg,-, fgbc поступают постоянно на выход схемы и подаются в блок 2 для организации режимов за- писи-считьшания в блоке 5 оперативной памяти.

Перед началом обработки каждого участка сигнал Сброс устанавливает триггеры 34 и 37 в нулевое состояние, а в счетчик 38 заносится двоичный код уставки (n-l)-l, который определяет начальный адрес блока 5. Сигнал из импульсной последовательности f ПРОХОДИТ, через элементы И 35 и

ИЛИ 36 и устанавливает триггер 37 в единичное состояние, с инверсного выхода которого подается сигнал Выборка А. На выходе элемента И-НЕ 39 появляется сигнал Запись, когда на первый вход этого элемента поступает импульс из последовательности . Схемой выработана необходимая комбинация сигналов для записи слов из блока программы в блок 5 оперативной памяти.

Одновременно сигнал Запись проходит через элемент 44 и по зад,нему фронту уменьшает содержимое счетчика 38 на единицу, тем самым устанавливается новый адрес. Следующий за этим сигнал импульсной последовательности f ; проходит через элемент ИОЬ С

НЕ 40 и по своему заднему фронту переводит триггер 37 в нулевое состояние, так как его D-вход соединен с общей шиной схемы. Элемент 41 закрыт по второму входу нулевым потенциалом с прямого выхода триггера 34 поэтому сигнал Конец смены информации на выход схемы не подается,

Следующий сигнал из последовательности f опять устанавливает триггер 37 в единичное состояние. Схема вьщает сигналы Выборка А и Запись, а адрес после этого уменьшается на единицу Когда счетчик 38 выходит в нулевое состояние5что соответствует последнему адресу блока 5, на выходе элемента 42 появляется положительный потенциал, который запрещает прохождение сигнаша Запись через элемент 44. Сигнал Запись проходит в этом случае; -через элемент 43, записывает в счетчик 38 код уставки (п-1)-1 и переводит триггер 34 в единичное состояние. Это означает, что в блок 5 загрузилась из блока программы вся исходная информация для интерполяции.

Следующий за этим импульс из последовательности f ,,,1,- проходит через элемент И-НЕ 40 и элемент 41 и как сигнал Конец смены информации поступает на вькод схемы. В данньй момент с соответствующих выходов схемы в блок 5 подается начальный адрес и сигнал Выборка А. Следовательно, на выходах данных блока 5 оперативной памяти присутствует код записанных ранее по начальному адресу слов. Передний фронт сигнала Конец смены информации используется для передачи слон из блока 5 в блок 4 двухкоординатной интерполяции. В момент заднего фронта сигнала Конец смены информации триггер

37 устанавливается в нулевое состоя- ние и снимается сигнал Выборка А.

В дальнейшем при отработке заданного участка триггер 34 остается в единргчном состоянии, а триггер

37 устанавливается в единичное состояние только сигналом Смена информации, поступающим на вход схемы. Появляется сигнал Выборка А, а сигналом Запись происходит занесение слов из блока 4 двухкоординатной интерполяции по адресу, находящемуся в счетчике 38. В момент заднего фронта сигнала Запись изменяется адрес на единицу и передний

фронт сигнала Конец смены информации осуществляет передачу слов в блок 4 из блока 5 уже по измененному на единицу адресу.

В завис1-1мости от знака оценочной функции и ДВМК лВДК-ВМК триггер 46 находится з единичном или нулевом состоянии, причем в единичном состоянии он находится при Ui О, а в нулевом - при U .

Если , то очередной импульс ия тактовой частоты интерполяции f проходит через элемент И 47 по ведомой координате, а через элемент ИЛИ 49 - на выход по ведущей

координате, т.е. делается диагональный шаг. Этот же импульс поступает на вход элемента 51 совпадения, происходит передача дополнительного кода .содержимого регистра 50 в

сумматор 52 для вычисления нового значения оценочной функции

и и - (ДВДК - лВМК;) .

Если и 0, то очередной импульс проходит через элементы И 48 и ИЛИ 49 на выход по ведущей координате. Этот же импульс поступает на вход элемента 53, передается прямой код содержимого регистра 54 в сумматор 52 для вычисления нового значения оценочной функции U U +ЛВМК;. Если в результате суммирования содержимого регистра 54 (ЛВЖ) с содержимым сумматора 52 (U) изменяется знак суммы с отрицательного на положительный, то на выхэде сумматора 52 возникает сигнал переполнения в виде высокого потенциала, ПОСТУ111

пающего на D-вход триггера 46. Последний по заднему фронту поступившег на вход схемы тактового импульса устанавливается в единичное состояние. Если результат суммы остается отрицательным, то-триггер 46 остается в .нулевом состоянии, так как переполнение сумматора не происходит.

Информационные входы данных ре - гистров 50 и 54, сумматора 52 и триггера 46 подаются на выход схемы и соединяются с выходными шинами дан- ньк соответствующих блоков 5 оперативной памяти, а выходы этих же данных регистров, сумматора и .триггера соединяются с входными шинами данных блоков 5.

Устройство позволяет осуществить многокоординатную интерполяцию на одном двухкоординатном блоке интерполяции. Следовательно, аппаратные затраты на его реализацию сокращаются тем больше, чем в большем числе координат требуется производить интерполяцию, так как в аналогичных устройствах при интерполяции по п координатам необходимо иметь h или п-1 блоков двухкоординатной интерполяции. Возможность в устройстве организовать выход тактового сигнала с блока задания скорости сразу по нескольким координатам в соответствии с управляющим алгоритмом позволяет увеличить быстродействие интерполятора, так как общее .количество тактовы сигналов с блока задания скорости на отработку участка сокращается за счет диагональных шагов. Формула изобретения

Многокоординатный цифровой интерполятор, содержащий при интерполяции по п координатам блок двухкоординатной интерполяции .и сч етчик перемещений, отличающий- с я тем, что, с целью повьш1ения быстродействия интерполятора, в него введены три блока оперативной памяти, блок буферной памяти типа первый вошел - первый вышел, сос:тоящий из п сдвиговых регистров первая и вторая группы элементов ИЛИ, мультиплексор и четыре демуль- типлексора, блок оценочной функции, блок управления интерполяцией и блок управления обменом информации меж. ду оперативным запоминающем устройством и блоком интерполяции, при912

чем первые выходы первой и второй групп элементов ИЛИ соединены соответственно с информационным и такто- Bbw входами первого сдвигового регистра, а п-е выходы первой и второй групп элементов ИЛИ - с информационным и тактовым входами п-го сдвигового регистра, выход каждого из регистров соединен с одним из

входов мультиплексора и выходом интерполятора, первые входы первой группы элементов ИЛИ соединены с п выходами второго демультиплексо- ра, вторые входы - с соответствующи

ми п выходами третьего демульти

плексора, а первые входы второй- группы элементов ИЛИ соединены с п выходами первого демультштлексора, вторые входы - с соответствующими

п выходами четвертого демультиплек- сора, объединенные третьи входы второй группы элементов ИЛИ и первый вход блока управления интерполяцией соединены с первым входом интерполятора, кодовые входы первого, второго демультиплексоров и мультиплексора соединены с первым выходом блока интерполяции, второй выход которого .соединен с объединенными кодовыми входами третьего и четвертого демультиплексоров, первый и второй выходы блока оценочной функции соединены соответственно с первым и вторым входами блока интерполяции,

третий вход которого соединен с четвертым выходом блока управления обменом информации, а первый, второй и третий управляющие выходы блока обменом информации соединены соответственно с первым, вторым и

третьим входами всех трех оперативных запоминающих устройств, выход данных каждого из оперативных-запоминающих устройств соединен с входами данных блока интерполяции, а вход данных каждого из оперативных запоминающих устройств - с выходами данных блока интерполяции, третий выход которого соединен с вторым входом блока оценочной функции, третий и четвертый выходы блока оценочной функции соединены с тактовыми входами соответственно, второго и третьего демультипле соров, первый вход блока оценочной функции соединен с вторым выходом блока управления интерполяцией, третий выход которого соедннен с тактовыми входами первого и четвертого демуль гиплексоров, а первый выход с первым входом блока управления обменом информации, пятый выход которого соединен с третьим входом блока управления интерполяцией, четвертый выход блока управления интерполяцией соединен с

JiJiJiTinjiruiJinjijmj

Уя

31593914

выходом интерполятора, вторые входы ; счетчика перемещений, блока управления интерполяцией и блока управления обменом информации соединены с вхо- 5 дами интерполятора, вход счетчика перемещений соединен с выходом мультиплексора , а выход - с выходом интерполятора.

фиг.6

| название | год | авторы | номер документа |

|---|---|---|---|

| Многокоординатный цифровой линейный интерполятор | 1987 |

|

SU1522154A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Многокоординатный цифровой интерполятор | 1984 |

|

SU1200246A1 |

| Цифровой линейный интерполятор | 1991 |

|

SU1807450A1 |

| Линейный интерполятор | 1991 |

|

SU1809421A1 |

| Линейный интерполятор | 1988 |

|

SU1538166A2 |

| Круговой интерполятор | 1988 |

|

SU1566321A1 |

| Линейный интерполятор | 1987 |

|

SU1439532A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1631518A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах с ЧПУ. Цель изобретения - повышение быстродействия устройства - достигается благодаря проведению интерполяции в п координатах на. одном двухкоординатном блоке интерполяции и организации диагональных управляющих шагов, а также за счет введения в него блока I управления интерполяцией, блока 2 управления обменом информации, блока 3 оценочной функции, ОЗУ 5, мультиплексора 6, демультиплексоров 7 - 10, групп элементов 1ШИ 11, 12, блока буферс S со СП 00 i;o

| Сосонкин В.Л | |||

| и др | |||

| Программное управление станками | |||

| - М.: Машиностроение, 1981, с.227-248 | |||

| Многокоординатный цифровой интерполятор | 1981 |

|

SU966665A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-06-07—Публикация

1986-01-07—Подача