11

Изобретение относится к вычислительной технике и может быть использовано в .цифровых вычислительных и измерительных системах.

Цель изобретения - уменьшение аппаратурных затрат.

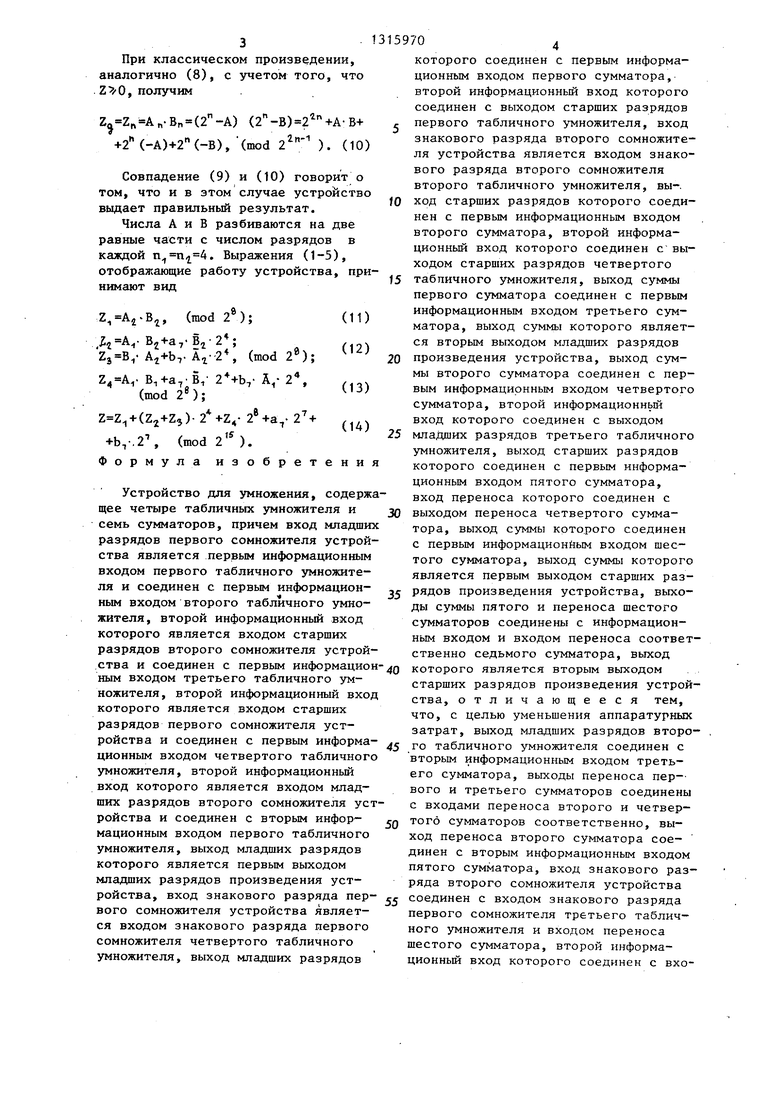

На чертеже представлена функциональная схема устройства.

Устройство содержит первый 1, четвертый 2, второй 3 и третий 4 табличные умножители, семь сумматоров 5-11, входы 12-14 младших, старших и знакового .разряд ов второго сомножителя, входы 15-17 младших, старших и знакового разрядов первого сомножителя, выходы 18 и 19 первых и вторых младших разрядов произведения, выходы 20 и 21 первых и вторых старших разрядов произведения.

Кодирование функциональных преобразователей при п-разрядных входных числах А и В, при разбиении каждого из них на две части (,, А.; В,), где разрядность частей А, В, -п; Aj, Bj-nj осуществляется по следующим формулам:

.Bj, (mod ); (1) Bj+Ef,- ;

Z A B +bn-AI-2 , (mod 2); (2) Z,A,- В,+а„-В,,-A,-2 . ,(3)

Окончательный результат произведения, реализуемый устройством, вычисляется по формуле

, + () 2 +Z,. 2 Чап- 2%-t-b -2, (mod ),

(4)

где mod 2 обозначает, что результат представляется в х-разрядной секе, а, и Ь - знаковые разряды операндов.

Устройство работает следующим образом.

При положительных сомножителях (А,) коэффициенты а, Ь,0, поэтому коррекции не происходит. Выражение (4) принимает вид

,2n

1

,-.В,. 2 (A,- B +Aa-B)-2 +

(5)

+A2B, (mod 2)

Поскольку Z7/0, запись его в прямом коде эквивалентна записи в дополнительном коде.

59702

Если один из сомножителей отрицателен, например , с выходов табличных умножителей частичные произведения поступают с предварительной

5 коррекцией и после суммирования дают следующий рез5гльтат: ,- . 2. (А, В4+

+Aj.Bi+Bi-2 М X 2 +Ai-В2- -2 (mod ),

fO

(6)

так как а,1, .

Выражение (6) можно представить в виде суммы двух слагаемых z , рав- ного произведению кодов А,. В и корректирующего коэффициента с

Z Z +C A-B+2(B+1)Z +2 (-В),

(mod )„(7)

Рассмотрим теперь процесс перемножения с преобразованием сомножителей в прямой код и с последующим преобразованием произведения в дополнительньш код. Поскольку АО, , то , следовательно

,2п

,2п

,()()-B

2 +А В-2 +Z +2 - (-В), (mod ).(8)

Как видим, выражения (7) и (8) тождественны (коэффициент 2 выходит за пределы ()-разрядной сетки и поэтому не оказывает влияния на результат) , что говорит о правильности Выполнения произведения устройством.

Аналогично выполняется произведение в случае , . При равенст- ве нулю одного из сомножителей (например, В), выражение (4) примет вид

Zn,

,- 2 -2 2+Bi-2

+2

Zn-i

45

(В+1), (mod 2 ),

т.е. даже при з множении отрицательного числа на нуль, выходной нулевой результат будет положительным, что соответствует представлению чисел в 50 дополнительных кодах.

В случае, если оба сомножителя отрицательны, результат произведения согласно (4) выглядит следующим образом:

+ (A,- B +B AJ+BI- )2 +

+ (A,B,+BV 2 +А, 2 М-2 2+2%2 А-В+2 - (-В)+2;(-А), (mod ). (9)

При классическом произведении, аналогично (8), с учетом того, что , получим

А а п I

.Вп () ()2 +А-В-н

)+2(-В), (mod 2 ). (10)

Совпадение (9) и (10) говорит о том, что и в этом случае устройство выдает правильный результат.

Числа А и В разбиваются на две равные части с числом разрядов в каждой . Выражения (1-5), отображающие работу устройства, принимают вид

B гBj+a

(mod

2Ъ;

Aj+b,- , (mod

2«);

(11) (12)

, ,- A,- 2, (mod 2);

+ (Z2+Z5) ,-2 +

.2, (mod 2 ). Формула изобрет

Устройство для умножения, содержащее четыре табличных умножителя и семь сумматоров, причем вход младших разрядов первого сомножителя устройства является первым информационным входом первого табличного умножителя и соединен с первым информационным входом второго табличного умножителя, второй информационный вход которого является входом старших разрядов второго сомножителя устрой

45

.ства и соединен с первым информацион- д которого является вторым выходом ным входом третьего табличного умножителя, второй информационный вход которого является входом старших разрядов первого сомножителя устройства и соединен с первым информационным входом четвертого табличного умножителя, второй информационный вход которого является входом младших разрядов второго сомножителя устройства и соединен с вторым информационным входом первого табличного умножителя, выход младших разрядов которого является первым выходом младших разрядов произведения уст50

старших разрядов произведения уст ства, отличающееся те что, с целью уменьшения аппаратур затрат, выход младших разрядов вт го табличного умножителя соединен вторым информационным входом трет его сумматора, выходы переноса пе вого и третьего сумматоров соедин с входами переноса второго и четв того сумматоров соответственно, в ход переноса второго сумматора со динен с вторым информационным вхо пятого сумматора, вход знакового ряда второго сомножителя устройст

ройства, вход знакового разряда пер- соединен с входом знакового разряда

вого сомножителя устройства является входом знакового разряда первого сомножителя четвертого табличного умножителя, выход младших разрядов

первого сомножителя третьего табличного умножителя и входом переноса шестого сумматора, второй информа- ционньй вход которого соединен с вхо

зо3159704

которого соединен с первым информационным входом первого сумматора, второй информационный вход которого соединен с выходом старших разрядов

г первого табличного умножителя, вход знакового разряда второго сомножителя устройства является входом знакового разряда второго сомножителя второго табличного умножителя, вы-.

fO ход старших разрядов которого соединен с первым информационным входом второго сумматора, второй информационный вход которого соединен с выходом старших разрядов четвертого

t5 табличного умножителя, выход суммы первого сумматора соединен с первым информационным входом третьего сумматора, выход суммы которого является вторым выходом младших разрядов

20 произведения устройства, выход суммы второго сумматора соединен с первым информационным входом четвертого сумматора, второй информационньш вход которого соединен с выходом

25 младших разрядов третьего табличного умножителя, выход старших разрядов которого соединен с первым информационным входом пятого сумматора, вход переноса которого соединен с выходом переноса четвертого сумматора, выход суммы которого соединен с первым информационйым входом шестого сумматора, выход суммы которого является первым выходом старших раз35 рядов произведения устройства, выходы суммы пятого и переноса шестого сумматоров соединены с информационным входом и входом переноса соответственно седьмого сумматора, выход

которого является вторым выходом

старших разрядов произведения устройства, отличающееся тем, что, с целью уменьшения аппаратурных затрат, выход младших разрядов второго табличного умножителя соединен с вторым информационным входом третьего сумматора, выходы переноса пер-- вого и третьего сумматоров соединены с входами переноса второго и четвертого сумматоров соответственно, выход переноса второго сумматора соединен с вторым информационным входом пятого сумматора, вход знакового разряда второго сомножителя устройства

первого сомножителя третьего табличного умножителя и входом переноса шестого сумматора, второй информа- ционньй вход которого соединен с вхо513159706

дом знакового разряда первого сомно- разряда второго сомножителя третье- жителя устройства и входом знакового го табличного з множителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Матричное множительное устройство | 1980 |

|

SU942003A1 |

| УМНОЖИТЕЛЬ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2024 |

|

RU2839987C1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Устройство для вычисления функции | 1985 |

|

SU1280614A1 |

| Устройство для вычисления сумм произведений | 1988 |

|

SU1569826A1 |

| Устройство для умножения | 1982 |

|

SU1059569A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для вычисления сумм произведений | 1980 |

|

SU905814A1 |

| Устройство для умножения | 1981 |

|

SU1019442A1 |

Устройство для умножения двоичных чисел, представленных в дополнительном коде, может быть использова/2 « lit 15 пГ 2 17 но в цифровых вычислительных и измерительных системах.Устройство содержит четыре табличных умножителя 1-4 и семь сумматоров 5-11, причем 12, 13, 14 - входы соответственно младших, старших и знакового разрядов второго сомножителя, а 15, 16, 17 - входы соответствующих разрядов первого сомножителя, 18-21 - выходы устройства. За счет совмещения операции вычисления «частичных произведений с предварительной частичной коррекцией результата в табличных умножителях удалось уменьшить аппаратурные затраты устройства. 1 ил. 18 (Л СО Ю 20 ел QD И 21

| Электроника, 1970, № 10, с | |||

| Насос | 1917 |

|

SU13A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения | 1981 |

|

SU1019442A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-11—Подача