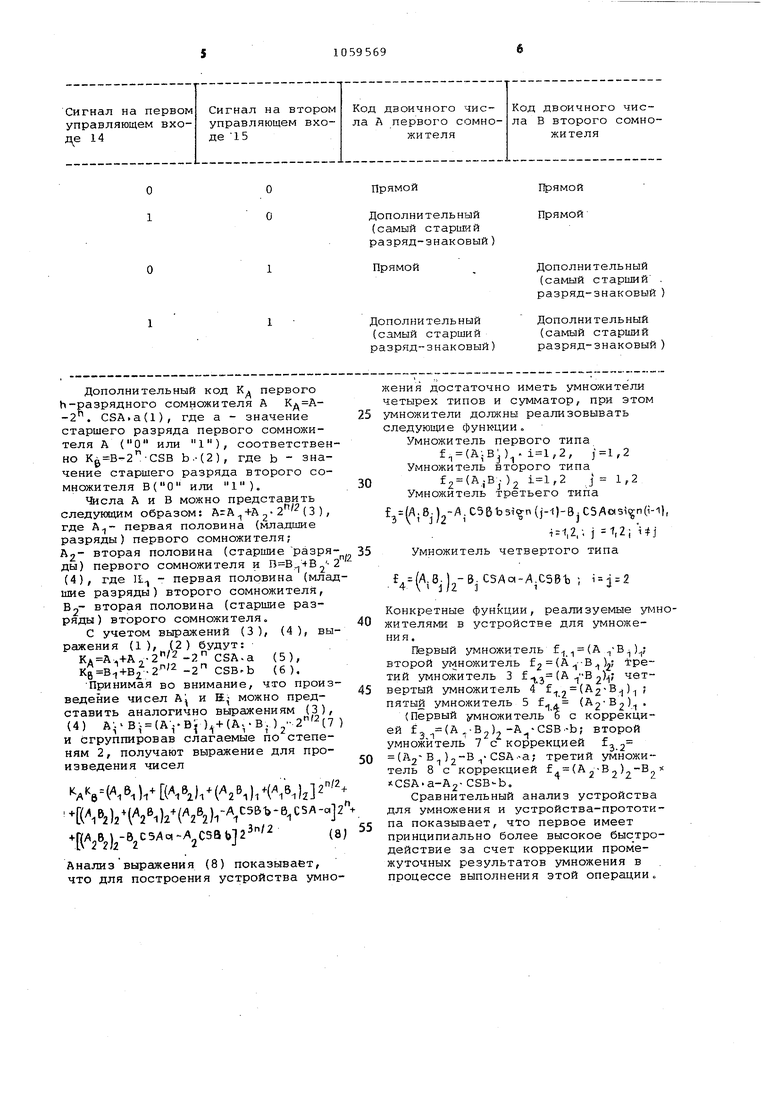

содержит узел умножения, коммутатор и вычитатель, причем первая и втора группы входов узла умножения соединены с первой и второй группами информационных входов.умножителя соответственно, а выходы подключены к входам уменьшаемого вычитателя, выходы которого являются выходами умножителя, а входы вычитаемого соединены с выходами коммутатора, информационные входы которого подключены к третьей группе информационных входов умножителя, а управляющие входы - к первому и второму входам умножителя.

3. Устройство по п. 1, О т л и чающееся тем, что третий умножитель с коррекцией содержит узел умножения два коммутатора и вычитатель, причем первая и вторая группы входов узла умножения соединены с первой и второй группйми информационных входов умножителя соответственно, а выходы подключены к-входам уменьшаемого вычитателя, выходы которого являются выходами умножителя, а входы первого и второго вычитаемых соединены соответственно с выходами первого и второго коммутаторов, информационные входы которых соединены соответственно с третьей и четвертой группами информационных входов умножителя, управляющие входы первого коммутатора подключены к первому и второму управляющим входам умножителя, третий и четвертый управляющие входы которого подключены к управляющим входам второго коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

1. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее пять умножителей и сумматор, причем входы младших разрядов первого сомножителя устройства соединены с первыми группами входов первого, второго и третьего умножителей, входы старших разрядов первого сомножителя устройства соединены с первыми группами входов четвертого и пятого умножителей, входы младших разрядов второго сомножителя устройства подключены к вторым группам входов первого, второго и четвертого умножителей, входы старших разрядов второго сомножителя устройства подключены к вторым группам входов третьего и пятого умножителей, выходы первого умножителя соединены с выходами младших разрядов результата устройства, выходы второго, третьего, четвертого и пятого умножителей подключены соответственно к первой, второй, третьей и четвертой группам входов сумматора, выходы которого соединены с выходами старших разрядов результата устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит первый, второй и третий умножители с коррекцией, причем первая, вторая и третья группы входов первого умножителя с коррекцией соединены соответстбенно с входами младших разрядов первого сомножителя, входами старших разрядов . второго сомножителя и входами младших разрядов первого сомножителя устройства, первая группа информационных входов второго умножителя с коррекцией соединена с входами старших разрядов первого сомножителя устройства, вторая и третья группы информационных входов второго умножителя с коррекцией соединены с входами младших разрядов второго сомножителя устройства, первая и вторая группы информационных входов третьего умножителя с коррекцией соединены с входами старших разрядов соответственно (Л первого и второго сомножителей устройства, третья и четвертая группы информационных входов третьего умножителя с коррекцией подключены к входам старших разрядов соответственно второго и первого сомножителей устройства, первый управляющий вход устройства и вход сл самого старшего разряда первого сомножителя устройства подключены со00 ответственно к первым и вторым О1 управлягацим входам второго, и третьо его умножителей с коррекцией, второй управляющий вход устройства со и вход самого старшего разряда второго сомножителя подключены соответственно к первому и второму управляющим входам первого умножителя с коррекцией и третьему и четвертому управляющим входам третьего умножителя с коррекцией, выходы первого, второго и третьего умножителей с коррекцией подключены соответственно к пятой, шестой и седьмой группам входов сумматора. 2, Устройство по п. 1, о т л и чающееся тем, что i-и умножитель с коррекцией (, 2)

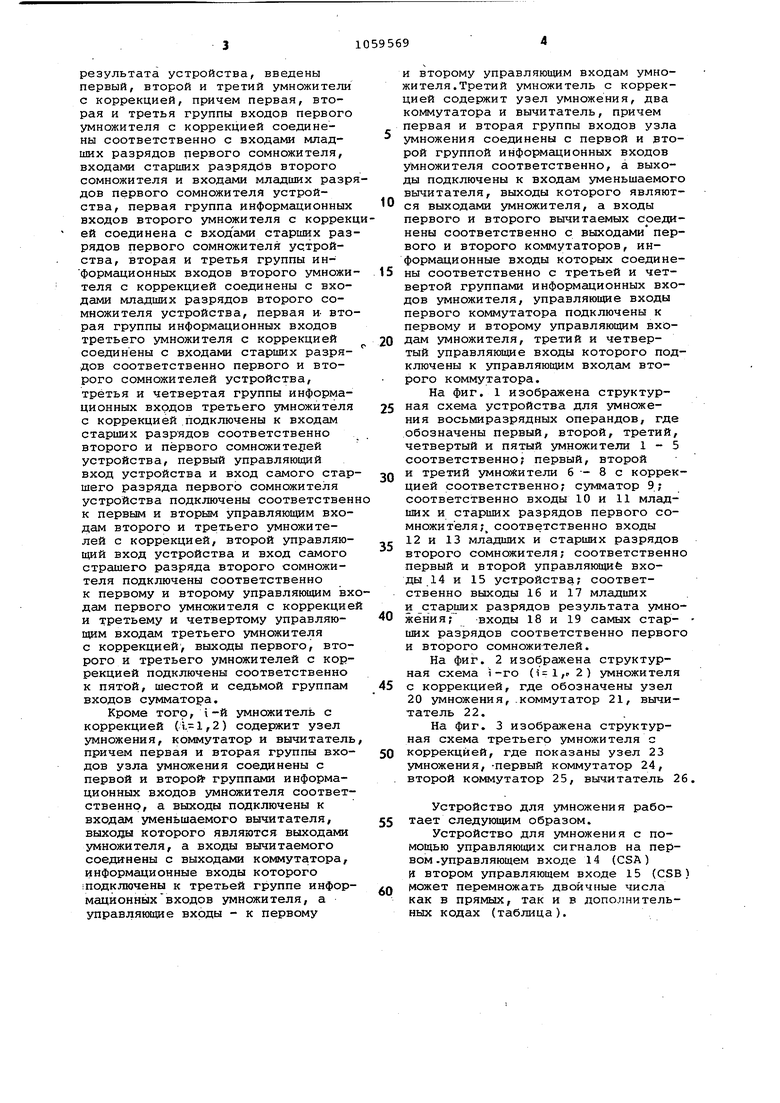

Изобретение относится к вычисли тельной технике и может быть использовано при построении быстродействующих вычислительных машин. Известно устройство для умножеНИН, содержащее декодирующий блок, пять мультиплексоров, блок сдвигаи группу сумматоров, выходы которы соединены с выходами устройства, фсоды - с входами сигналов управления режимами работы устройства и с выходами мультиплексоров, входы которых подключены к входам устройства, на которые подаются разря ды множимого и множителя Cl3Недостатком указанного устройства является малое быстродействие Наиболее близким к предлагаемо.му является устройство для умножения, содержащее пять Змножителей и сумматор, причем входы младших р рядов первого сомножителя устройства соединены с первыми группами входов первого, второго и третьего умножителей, входы старших разрядо первого сомножителя устройства соединены с первыми группами входов четвертого и пятого умножителей, входы младших разрядов второго сомножителя устройства подключены к вторым группам входов первого, второго и четвертого умножителей, входы старших разрядов второго сомножителя устройства подключены к вторым группам входов третьего и пятого умножителей, выходы перво умножителя соединены с выходами младших разрядов результата устройства, выходы второго, третьего. четвертого и пятого умножителей подключены соответственно к первой, второй, третьей и четвертой группам входов сумматора,, выходы которого соединены с выходами старших разрядов результата устройства СзХ Недостатком известного устройства для умножения является низкое быстродействие . Цель изобретения - повышение быстродействия устройства для умножения. Поставленная цель достигается тем, ЧТО в устройство для умножения, содержащее пять умножителей и сумматор, причем входы младших разрядов первого сомножителя устройства соединены с первыми группами входов первого, второго и третьего умножителей, входы старших разрядов первого сомножителя устройства соединены с первыми группами входов четвертого и пятого умножителей, входы младших разрядов второго сомножителя устройства подключены к вторьзм группам входов первого, второго и четвертого умножителей, входы старших разрядов второго сомножителя устройства подключены к вторым группам входов третьего и пятого умножителей, выходы первого умножителя соединены с выходами младших разрядов результата устройства, выходы второго, третьего, четвертого и пятого умножителей подключены соответственно к первой, второй, третьей и четвертой группам входов сумматора, выходы которого соединены с выходами старших разрядов результата устройства, введены первый, второй и третий умножители с коррекцией, причем первая, вторая и третья группы входов первого умножителя с коррекцией соединены соответственно с входами младших разрядов первого сомножителя, входами старших разрядив второго сомножителя и входами младших разр дов первого сомножителя устройства, первая группа информационных входов второго умножителя с коррек ей соединена с входами старших раз рядов первого сомножителя устройства, вторая и третья группы информационных входов второго умножи теля с коррекцией соединены с входами младших разрядов второго сомножителя устройства, первая и- вто рая группы информационных входов третьего умножителя с коррекцией соединены с входами старших разрядов соответственно первого и второго сомножителей устройства, третья и четвертая группы информационных вхрдов третьего умножителя с коррекцией подключены к входам старших разрядов соответственно второго и первого сомножителей устройства, первый управляющий вход устройства и вход самого стар шего разряда первого сомножителя устройства подключены соответствен к первым и вторым управляющим входам второго и третьего умножителей с коррекцией, второй управляющий вход устройства и вход самого страшего разряда второго сомножителя подключены соответственно к первому и второму управляющим вх дам первого умножителя с коррекцие и третьему и четвертому управляющим входам третьего умножителя с коррекцией, выходы первого, второго и третьего умножителей с коррекцией подключены соответственно к пятой, шестой и седьмой группам входов сумматора. Кроме Torpf i-й умножитель с коррекцией (Л. 1,2) содержит узел умножения, коммутатор и вычитател причем первая и вторая группы вхо дов узла умножения соединены с первой и второй- группами информационных входов умножителя соответ ственно, а выходы подключены к входам уменьшаемого вычитателя, выходы которого являются выходами умножителя, а входы вычитаемого соединены с выходами коммутатора, информационные входы которого подключены к третьей группе инфор мационных входов умножителя, а управляющие входы - к первому и второму управляющим входам умножителя. Третий умножитель с коррекцией содержит узел умножения, два коммутатора и вычитатель, причем первая и вторая группы входов узла умножения соединены с первой и второй группой информационных входов умножителя соответственно, а выходы подключены к входам уменьшаемого вычитателя, выходы которого являются выходами умножителя, а входы первого и второго вычитаемых соединены соответственно с выходами первого и второго коммутаторов, информационные входы которых соединены соответственно с третьей и четвертой группами информационных входов умножителя, управляющие входы первого коммутатора подключены к первому и второму управляющим входам умножителя, третий и четвертый управляющие входы которого подключены к управляющим входам второго коммутатора. На фиг. 1 изображена структурная схема устройства для умножения восьмиразрядных операндов, где обозначены первый, второй, третий, четвертый и пятый умножители 1-5 соответственно; первый, второй и третий умножители б - 8 с коррекцией соответственно; сумматор 9; соответственно входы 10 и 11 младших и старших разрядов первого сомножителя; соответственно входы 12 и 13 младших и старших разрядов второго сомножителя; соответственно первый и второй управляющие входы 14 и 15 устройства; соответственно выходы 16 и 17 младших и старших разрядов результата умножения; входы 18 и 19 самых стар- ших разрядов соответственно первого и второго сомножителей. На фиг. 2 изображена структурная схема i-го (,r 2) умножителя с коррекцией, где обозначены узел 20 умножения,.коммутатор 21, вычитатель 22. На фиг. 3 изображена структурная схема третьего умножителя с коррекцией, где показаны узел 23 умножения, -первый коммутатор 24, второй коммутатор 25, вычитатель 26. Устройство для умножения работает следующим образом. Устройство для умножения с помощью управляющих сигналов на первом -управляющем входе 14 (CSA) Я втором управляющем входе 15 (CSB) может перемножать двойч 1ые числа как в прямых, так и в дополнительных кодах (таблица).

Сигнал на втором управляющем входе 15

О О Дополнительный код Кд первого h-разрядного сомножителя А . CSA.a(l), где а - значение старшего разряда первого сомножителя А (О или 1), соответствен но b.-(2), где b - значение старшего разряда второго сомножителя В (О или 1). сла А и В можно представить следуняцим образом: (3 ), где первая половина (младшие разряды) первого сомножителя; А2- вторая половина (старшие разряды) первого сомножителя и n B -tB -2 (4), где 11-, - первая половина (млад шие разряды) второго сомножителя, Bj- вторая половина (старшие разряды) второго сомножителя. С учетом выражений (3), (4), выражения (1), (2) будут: .+А„-2 2 -2 CSA-a (5), KB Bi+B2-2 2 -2 CSB.b (6), Принимая во внимание, что произведение чисел А и К можно представить аналогично выражениям (3), (4) . (А-В )+(.)(7 и сгруппировав слагаемые по степеням 2, получают выражение для произведения чисел )1(z)-,(2)/{) Ч(2ЬЧ)2(2«2) RA.Bj-e с5Ас,А сзаыа (а ( 2 Анализ выражения (8) показывает, что для построения устройства умно

Код двоичного числа В второго сомножителя

ПрямойЩзямой

Дополнительный Прямой (самый старший разряд-знаковый)

Прямой

Дополнительный (самый старший . разряд-знаковый )

Дополнительный (самый старший разряд-знаковый) жения достаточно иметь умножители четырех типов и сумматор, при этом умножители должны реализовывать следующие функции. Умножитель первого типа f (AjB:,). ,2, ,2 Умножитель второго типа f2(A,,-B,|. )2 ,2 1,2 Умножитель третьего типа f3 (AiB.).C36b3i jn{j-i)-BjC5Aasi n(,-i), i l,2,-, j 1,2; Hj Умножитель четвертого типа ,-(&-).-В-С5А -А.СЪЬ ; 3 2 Конкретные функции, реализуемые y шoжителями в устройстве для умножения. Первый умножитель f,, (А .,В ); второй умножитель f2 (А --В )2; третий умножитель 3 f j (А уВ 2); четвертый умножитель 4 f (A2B) ; пятый умножитель 5 (А2-В2). (Первый умножитель 6 с коррекцией f 2 (А .В2)2-A -CSB-b; второй умножитель 7 с коррекцией f 2 (А2-В )2-В CSA.-a; третий умножитель 8 с коррекцией f.(А„-В„) -В « CSA.a-A2-CSB--bo Сравнительный анализ устройства для умножения и устройства-прототипа показывает, что первое имеет принципиально более высокое быстродействие за счет коррекции промежуточных результатов умножения в процессе выполнения этой операции.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент CUR № 4153938, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке № 3368105/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-07—Публикация

1982-03-29—Подача