ройства а выход соединен с вторыми управляющими входами пятого и шестого блоков памяти, вход второго элемента НЕ соединен со-знаковым входом второго сомножителя устройства, а выход соединен с управляющим входом блока инверсии, третьи управлящие входы третьего и четвертого блоков памяти соединены со знаковым входом первого сомножителя устройства, третий информационный вход пятого блока памяти соединен с входом младших разрядов второго сомножителя устройства, выход пятого блока памяти соединен с первым входом третьего сумматора, третий информационный вход шестого блока памяти соединен с входом старших разрядов второго сомножителя устройства, выход шестого блока памяти соединен с первым входом пятого сумматора, первый вход блока коррекции соединен с вторым выходом третьего сумматора, второй вход блока коррекции соединен со знаковым входом первого сомножителя устройства, третий вход блока коррекции соединен с входом младших разрядов второго сомножителя устройства, первый выход, шестого сумматора является третьим выходом устройства, второй вход шестого сумматора соединен с вторым выходом четвертого сумматора, выход седьмого сумматора является четвертым выходом устройства,/второй вход седьмого сумматора соединен с вторым выходом шестого сумматора, третий вход которого соединен с вторым выходом второго сумматора, второй выход первого сумматора соединен с третьим входом четвертого сумматора, третий вход третьего сумматора соединен со знаковым входом второго сомножителя устройства, выход пятого сумматора соединен с третьим входом седьмого сумматора, третий, четвертый и пятый выходы блока формирования знака являются пятым выходом устройства, шестой и седьмой входы блока формрования знака соединены с входом старших разрядов второго сомножителя

устройства, знаковым входом второго сомножителя устройства, знаковым входом первого сомножителя устройства, выходом второго элемента НЕ и выходом первого элемента НЕ соответственно.

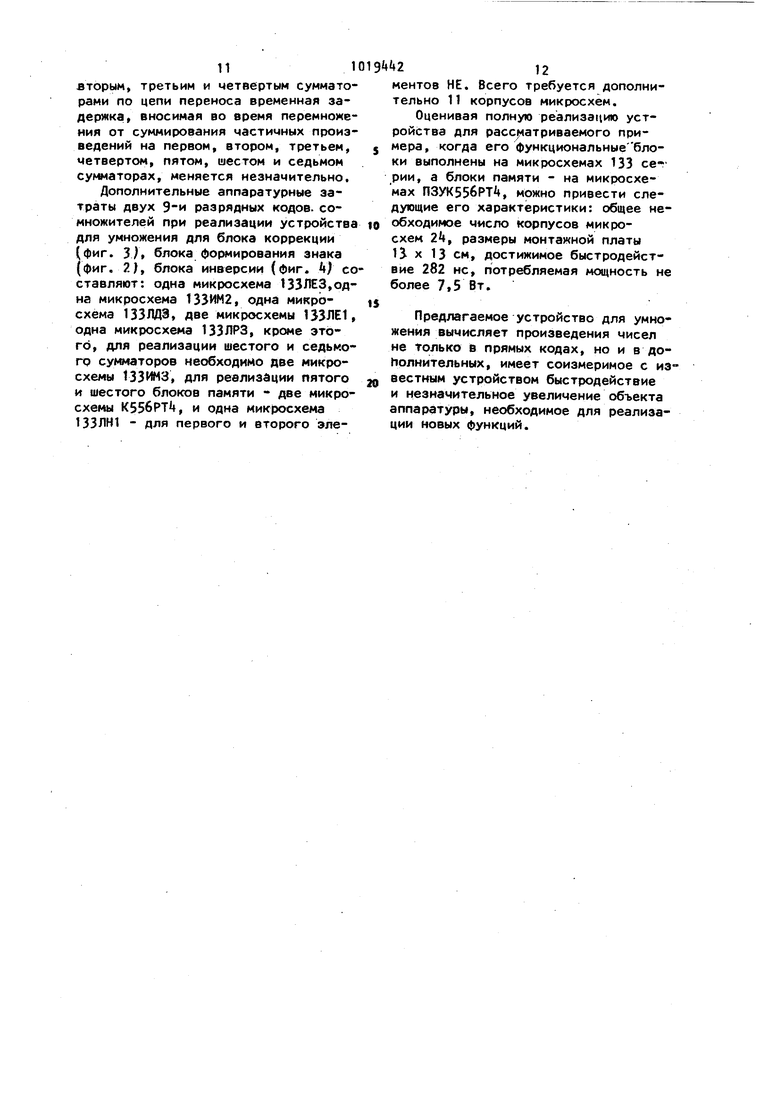

2.Устройство по п. 1, о т л и ч аю щ е е с я тем, что блок формирования знака содержит два элемента И-ИЛИ-НЕ и расширитель, при этом первый вход первой группы второго элемента И-ИЛИ-НЕ является шестым входом блока, второй вход первой группы второго, элемента И-ИЛИ-НЕ является седьмым входом блока, первый вход второй группы второго элемента И-ИЛИ-НЕ является четвертым входом блока, второй вход второй группы и первый вход третьей группы второго элемента И-ИЛИНЕ являются пятым входом блока, второй вход третьей группы второго эле мента И-ИЛИ-НЕ подключен к выходу первого элемента И-ИЛИ-НЕ, третий вход третьей группы второго элемента И-ИЛИНЕ является первым входом блока, первый и второй входы четвертой группы второго элемента И-ИЛИ-НЕ подключены

к первому и второму выходам расширителя соответственно, третий вход блока подключен к первым входам групп с пер вой по четвертую первого элемента И-ИЛИ-НЕ, к вторым входам групп с первой по четвертую первого элемента И-ИЛИ-НЕ подключен первый вход блока, к ёходам расширители подключен второй вход блока, выход второго элемента И-ИЛИ-НЕ является выходом блока.

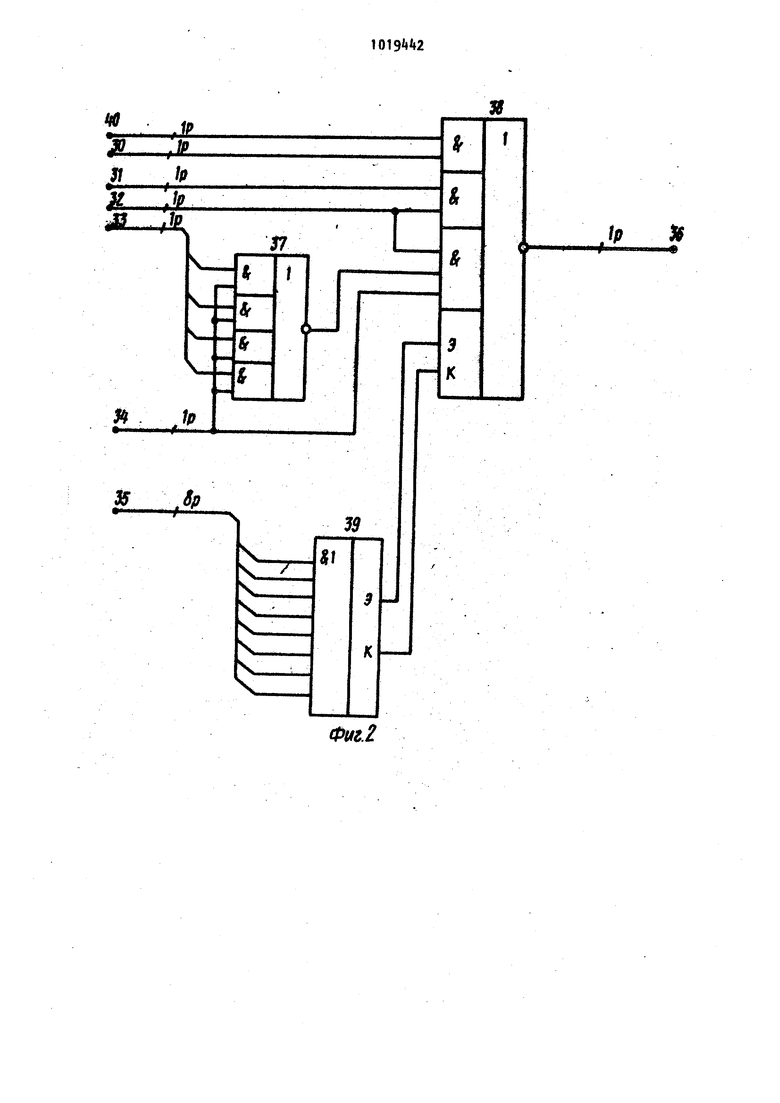

3.Устройство по п. 1, о т л и ч аю щ е е с я тем, что блок коррекции содержит элемент И-ИЛИ-НЕ и сумматор, при этом первые входы групп с первой по четвертую элемента И-ИЛИ-НЕ являются третьим входом блока, вторые входы групп с первой по четвертую элемента И-ИЛИ-НЕ являются вторым входом блока, выход элемента И-ИЛИ-НЕ подк.лючен к второму выходу блока и к первому входу сумматора, к второму входу которого подк.пючен первый вход блока, выходы сумматора подключены к первому выходу блока.

110

Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых вычислительных машинах, а также в цифровых системах контроля и управления.

Известны устройства умножения, использующие матричный, табличный и смешанный способы выполнения операции умножения.

Известно-устройство, использующее табличный способ выполнения операции умножения, содержит специализированный блок памяти, в котором хранится результат выполнения операции умножения Cv J

Недостатком этого устройства являются ограниченные возможности в его реализации для многоразрядных сомножителей, так как существущие и разрабатываемые микросхемы памяти пока имеют ограниченное число ячеек.

Известно устройство, выполняющее умножение в дополнительном коде и со держащее матрицу по ,гп полных сумматоров в ряду и (т -1 ) элементов И, выходы которых соединены с входами соответствующих сумматоров. Кроме того, устройство содержит входную и выходную корректирующие схемы. Выходы входной корректирующей схемы, предназначенной для специального пресйразования входных сигналов в новые двоичные переменные , соединены с соответствующими входами элементов И,

а выходы сумматоров последнего ряда матрицы - с входом корректирующей схемы, которая преобразует произведение сомножителей в дополнительный код 23.

Недостатком этого устройства в сравнении с устройством, использующим, табличный способ, является значительное усложнение его схемы, приводящее к усложнению конструкции и к снижению быстродействия.

Наиболее близким к предлагаемому является устройство для умножения, основанное на частичном использовании табличного способа в схемах матричного типа и содержащее четыре блока памяти и пять сумматоров, причем вход младших разрядов первого сомножителя соединен с первыми входами первого и второго блока памяти,вход старших разрядов первого сомножителя соединен с первыми входами третьего и четвертого блока памяти, вход младших разрядов второго сомножителя соединен с вторы ми входами первого и третьего блока памяти, вход старших, разрядов второго

2j

сомножителя соединен с вторыми входами второго и четвертого блоков памяти, первый выход первого блока памяти соединен с первым входом первого сум- . матора, первый выход которого соединен с первым входом второго сумматора, первый выход третьего блока памяти соединен с первым входом третьего сумматора, второй вход которого соединен с первым выходом второго бло0ка памяти, первый выход четвертого блоблока памяти соединен с первым вхрдбм четвертого сумматора, второй вход которого соединен с первым выходом третьего сумматора, второй выкод четвертого блока памяти соединен с первым входом пятого сумматора, первый выход четвертого сумматора соединен с вторым входом пятого сумматора, второй выход второго блока памяти соединен с вто0рым входом второго сумматора, второй выход третьего блока памяти соединен с вторым входом первого сумма тора, вто- рой выход первого блока памяти является первым выходом устройства умноже5 ния| первый выход второго сумматора является вторым выходом устройства умножения 3}.

Достоинством этого устройства в сравнении с матричными устройствами

0 умножения является простота конструкции и большее быстродействие, так как это устройство частично реализовано на основе табличного способа.

Недостатком этого устройства является отсутствие возможности выполнения операции умножения в дополнительном коде, так как для выполнения операции умножения двух чисел в дополнительном коде необходимо преобразовао ние дополнительного кода в прямой, а после осуществления операции умножения необходимо обратное преобразование. Преобразование дополнительного кода в прямой и из npjBMoro в дополнительный потребует последовательного включения на входе и выходе устройства корректирующих схем, что приведет к .увеличению аппаратурных затрат и к значительному снижению быстродействия.

0

Цель изобретения - расширение области применения устройства путем вычисления произведения в дополнительном коде.

Поставленная цель достигается тем,

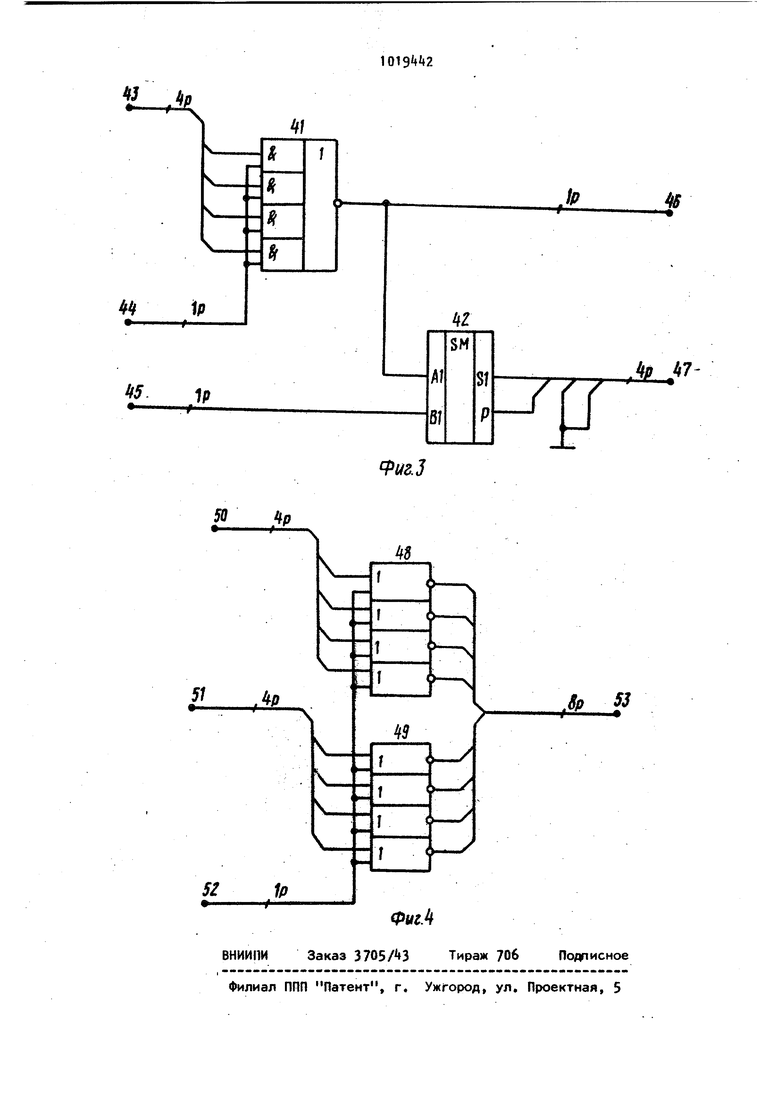

5 что в устройство для умножения, содержащее четыре блока памяти и пять сумматоров, причем вход младших разрядов первого сомножителя устройства соединен с первыми информационными входами первого и второго блоков памяти, вход стар1иих разрядов первого сомножителя устройства соединен с пе выми информационными входами третьего и четвертого блоков памяти, вход младших разрядов второго сомножителя устройства соединен с вторыми информационными входами первого и третьего блоков памяти, вход старших разрядов второго сомножителя устройства соединен с вторыми информационными входами второго и четвертого блоков памяти, первый выход первого блока памяти соединен с первым входом первого сумматора, .первый выход которого соединен с первым входом второго сумматора, первый выход третьего блока памяти соединен с первым входом третьего су| матора, второй вход которого соединен с первым выходом второго блока памяти, первый выход четвертого блока памяти соединен с первым входом четвертого сумматора, второй вход которого соединен с первым выходом третьего сумматора, второй выход четвертого блока памяти соединен с первым входом пятого сумматора, первый выход четвертого сумматора соединен с вторым вхо дом пятого сумматора, второй выход второго блока памяти соединен с вторым входом второго сумматора, второй выход третьего блока соединен с вторым входом первого сумматора, второй выход первого блока памяти является первым выходом устройства, первый выход второго сумматора является вторым выходом устройства, введены блок инверсии, шестой и седь мой сумматоры, пятый и шестой блоки памяти, блок коррекции, блок формирования знака, первый и второй элементы НЕ, при этом первый вход блока инверсии соединен с входом старших разрядов первого сомножителя уст ройства, а второй вход соединен с входом младших разрядов первого сомножителя устройства, первые входы шестого и седьмого сумматоров соединены с выхсз ом блока инверсии, первые информационные входы пятого и шестого блоков памяти соединены с входом старших разрядов первого сомножителя устройства, первый выход блока коррекции соединен с третьим входом пятого су 4матора, -первый вход блока формирования знака соединен с вторым выходом блока коррекции, а второй вход - с выходом блока инверli. СИИ, вход первого элемента ВЕ соединен со знакбвым входом первого сомножителя устройства, а выход соединен с вторыми управляющими входами пятого и шестого блоков памяти, вход второго элемента НЕ соединен со знаковым входом второ/о сомножителя устройства, а выход соединен с управляющим входом блока инверсии, третьи управляющие входы третьего и четвертого блоков памяти соединены со знаковьм входом первого сомножителя устройства, третий информационный вход пятого блока памяти соединен с входом младших разрядов второго сомножителя устройства, выход пятого блока памяти соединен с первым входом третьего сумматора, третий информационный вход шестого блока памяти соединен с входом старших разрядов второго сомножителя устройства, выход шестого блока памяти соединен с первым входом пятого сумматора, первый вход блока коррекции соединен с вторым выходом третьего сумматора, второй вход блока коррекции соединен со знаковым входомпервого сомножителя устройства, третий вход блока коррекции соединен с входом младших разрядов второго сомножителя устройства, первый выход шестого сумматора является третьим выходом устройства, второй вход шестого сумматора соединен с вторым выходом четвертого сумматора, второй выход седьмого сумматора является четвертым выходом устройства, второй вход седьмого сумматора соединен с вторым выходом шестого сумматора, третий вход которого соединен с вторым выходом второго сумматора, второй выход первого сумматора соединен с третьим входом четвертого сумматора, Третий вход третьего сумматора соединен со знаковым входом второго сомножителя устройства, выход пятого сумматора соединен с третьим входом седьмого сумматора, третий, четвертый и пятый выходы блока формирования знака являются пятым выходом устройства, шестой и седьмой входы блока формирования знака соединены с входом старших разрядов второго сомножителя устройства, знаковь|м входом второго сомножителя устройства, знаковым входом первого сомножителя устройства, выходом второго элемента НЕ и выходом первого элемента НЕ соответственно. йлок формирования знака содержит два элемента И-ИЛИ-НЕ и расширитель. при этом первый вход первой группы второго элемента И-ИЛИ-HF. является шестым входом блока, второй вход пер вой группы второго элемента И-ИЛИ-НЕ является седьмым входом блока, первы вход второй группы второго элемента И-ИПИ-НЕ является четвертым входо блока, второй вход второй группы и первый вход третьей группы аторого элемента И-ИЛИ-НЕ являются пятым вхо дом блока, второй вход третьей группы второго элемента И-ИЛИ-НЕ подключен к выходу первого элемента И-ИЛИ-НЕ, третий вход третьей группы второго элемента И-ИЛИ-НЕ является первым входом блока, первый и второй входы четвертой группы второго элемента И-ИЛИ-НЕ подключены к первому и второму выходам расширителя соответственно, третий вход блока подключей к первым входам групп с первой по четвертую первого элемента И-ИЛИ-НЕ, к вторым входам групп с первой по четвертую первого элемента И-ИЛИ-НЕ подключен первый вход блока, к входам расширителя подключен второй вход блока, выход второго элемента И-ИЛИ-НЕ является выходом блока. Блок коррекции содержит элемент ИгИЛИ-НЕ и сумматор, при этом первые входы групп с первой по четвертую элемента И-ИЛИ-НЕ являются-третьим входом блока, вторые входы групп с первой по четвертую элемента И-ИЛИ-НЕ являются вторым входом блока выход элемента И-ИЛИ-НЕ подключен к второму выходу блока и к первому вхо ду сумматора, к второму входу которого подключен первый вход блока, выходы сумматора подключены к первому выходу блока. На фиг. 1 изображена функциональная электрическая схема предлагаемого устройства; на фиг. 2 - блока фор мирования знака; на фиг. 3 - блока коррекции; на фиг. k - блока инверси Устройство для умножения содержит первый блок 1 памяти, второй 2 памяти, третий блок 3 памяти, четвертый блок k памяти, пятый блок 5 памяти, шестой блок 6 памяти, первый сумматор 7, третий сумматор 8, второй сум матор 9 четвертый сумматор 10, пятый сумматор 11, шестой сумматор 12, сумматор 13, блок I формиро вания знака, блок 15 инверсии, блок 16 коррекции, первый элемент НЕ второй элемент НЕ 18. Вход 19 является входом младшей половины кода первого сомножителя, вход 20 - вход старшей половины кади первого сомножителя,вход 21 - знаковый разряд первого сомножителя.Вход 22 является входом младшей половины кода второго сомножителя, вход 23 - вход старшей половины кода второго сомножителя, вход 2 - знаковый разряд второго сомножителя. На выходах 25-29 получается дополнительный код произведения первого сомножителя на второй сомножитель, представленных в дополнительном коде. Блок 1 формирования знака, входами которого являются вход 30 - седьмой вход блока 1, вход 31 - четвертый вход блока I, вход 32 - пятый вход блока 1k, вход 33 - третий вход блока Ц, вход 3 - первый вход блока 1, вход 35 - второй вход блока Н а выходом блока является выход 36, содержит первый элемент И-ИЛИ-НЕ 37, второй элемент И-ИЛИ-НЕ 38, расширитель 39- Вход 0 является шестым входом блока 1., Блок 16 коррекции -содержит элемент И-ИЛИ-НЕ 1 и сумматор 2. Вход является третьим входом блока 16, вход - вторым входом блока 16, вход 5 - первым входом блока 16, а выход 6 - вторым выходом блока 16, выход 7 - первым выходом блока 16. Блок 15 инверсии содержит первый элемент ИЛИ-НЕ 8 и второй элемент ИЛИ-НЕ if9. Вход 50 является вторым входом блока 15,вход 51 - первым входом блока 15, вход - третьим входом блока 15, а выход 53 - выходом блока 15. В устройстве для умножения вход 19 младших разрядов первого сомножителя соединен с первыми информационными входами первого 1 и второго 2 блоков памяти, вход 20 старших разрядов первого сомножителя соединен с первыми информационными входами третьего 3 и четвертого k блоков памяти, вход 22 младших разрядов второго сомножителя с вторыми информационными входами первого 1 и третьего 3 блоков памяти , вход 23 старших разрядов второго сомножителя соединен с вторыми информационными входами второго 2 и четвертого 4 блоков памяти, первый выход первого блока 1 памяти соединен с первым входом первого сумматора 7 пер- вый выход которого соединен с первым входом второго сумматора 9, первый выход третьего блока 3 памяти соеди нен с первым входом третьего сумматора 8, второй вход которого соединен с первым выходом второго блока 2 « памяти, первый выход четвертого блока k памяти соединен с первым вхо дом четвертого сумматора 10, второй вход которого соединен с первым выходом третьего сумматора 8, второй выход четвертого блока 4 памяти соеди нен с первым входом пятого сумматора 11, первый выход четвертого сумматора 10 соединен с вторым входом пятого cytwaropa 11, второй выход второго блока 2 памяти соединен с вторым входом второго сумматора 9 второй выход третьего блока 3 памяти соединен с вторым входом первого сумматора 7. Второй выход первого блока I памяти является первым вы-j ходря 25 устройства, первый выход второго сумматора 9 является вторым выходом 26 устройства, первый вход блока 15 инверсии соединен с входом 20 старших разрядов первого сомножители, а второй вход соединен с входом J9 младших разрядов первого сомножителя, первые входы шестого 12 и седьмого 13 сумматоров соединены с выходом блока 15 инверсии. Первые входы пятого 5 и шестого 6 блоков яаияти соединены с входом 20 старших разрядов первого сомножителя. Первый выход блока 16 коррекции/соединен с третьим входом пятого сумматора 11. Первый вход блока 14 формирования зна ка соединен с вторым выходом блока 1б коррекции, а второй вход - с выходом блока 15 инверсии. Вход первого элемента НЕ 17 соединен со знаковым входом 21 первого сомножителя, а выход соединен с вторыми управляющими входа ми пятого 5 и шестого 6 блоков памяти. Вход второго элемента НЕ 18 соеди нен со з аковым входом 24 второго сомножителя, а выход соединен с управ ляющим входом блока 15 инверсии. Третъи управляющие входы третьего 3 и не четвертого 4 блоков памяти соединены со знаковым входом 21 первого сомножителя, выход пятого блока 5 памяти, третий информационный вход которого соединен с входом 22 младших разрядов вто|эого сомножителя, соединен с первы входом третьего сумматора 8. Выход шестого блока 6 памяти, третий информационный вход которого соединен с входом 23 старших разрядов второго сомножителя, соединен с первым входом пятого сумматора 11. Первый вход бло12 ка 16 коррекции соединен с вторым выходом третьего сумматора 8, второй вход блока 16 коррекции соединен со знаковым входом 21 первого сомножителя. Третий вход блока 16 коррекции соединен с входом 22 младших разрядов второго сомножителя. Второй вход шестого сумматора 12, первый выход которого является третьим выходом 27 устройства, соединен с вторым выходом четвертого сумматора 10. Второй вход седьмого сумматора 13, выход которого является четвертым выходом 28 устройства, соединен с вторым выходом шестого сумматора 12, третий вход которого соединен с вторым выходом второго сумматора 9. Второй выход первого сумматора 7 соединен с третьим вхо дом четвертого сумматора 10. Третий вход третьего сумматора 8 соединен со знаковым входом 2 второго сомно жителя. Выход пятого сумматора 11 свединен с третьим входе седьмого сумматора 13. Третий, четвертый, пятый, шестой и седьмой входы блока 14 формирования знака, выход которого является пятым знаковым выходом 29 устройства, соединены с входом 23 старших разрядов второго сомножителя, знаковым входом 2k второго сомножителя, знаковым входом 21 первого Сомножителя, выходом второго элемента НЕ 18 и выходом первого элемента НЕ 17 соответственно. Рассмотрим работу устройства на примере умножения двух 9 разрядных сомножителей с получением 17 разрядного произведения. На входы устройства подаются следующие коды: дополнительный кед сомножителя ( множимого К который состоит из младших четырех разрядов вход J 9 , старших четырех разря дов (вход 20), знакового разряда (вход 21 и дополнительный код второго сомножителя (множителя), который также состоит из младших четырех разрядов (вход 22, старших четырех разрядов 23), знакового разряда (вход 24). На втором выходе первого блока 1 памяти. первом выходе второго сумматора 9, первом выходе шестого сумматора 12, выходе седьмого сумматора 13 и выходе блока 14 формирования знака, т.е. на выходах 25-29 получается дополнительный код произведения первого сомножителя на второй сомножитель. Причем, выходы 25-28, результа1ТЫ произведения, имеют 4-разрядный од, а выход 29 содержит один разряд кода знака числа результата произве-. дения. Коды множимого и множителя с разбиением на группы младших и старших разрядов (по четыре.разряда подаются в поочередной комбинации одновременно на адресные входы блоков 1-6 памяти, что приводит к выбору информации из соответствующей ячейки блоков памяти, где записан код частичного произведения (8-разрядный код). Коды частичных произведений с первого 1, второго 2, третьего 3, четвертого k блоков памяти поступают для суммирования на первый 7 второй 9, третий В четвертый 10, пятый II сумм-;торы, на выходе которых получается результат произведения, который требует ком пенсации по старшей половине восьми разрядов числа при умножении на отрицательный множитель, что осуществляет ся на шестом 2 и седьмом 13 сумматорах. Величина, на которую необходимопроводить компенсацию результата произведения, определяется с помощью бло ка 15 инверсии в зависимости от значения множимого и управляется инверсным знаковым разрядом множителя, с выхода второго элемента НЕ 18. Для полояительного множителя величина на выходе блока 15 инверсии тождественно равна нулю, .е. при этом компенсации не происходит. При умножении отрицательного множимого вместо половины старших разрядов кода частичного произведения, выдаваемого с первого выхода третьего 3 и второго выхода четвертого k блоков памяти, подаются коды частичных произведений с выходов пятого 5 и шестого 6 блоков памяти, которые вьбираются по второму управля ющему входу, подкгноченному к выходу первого элемента НЕ 17. Таким образом при отрицательном множимом происходит Суммирование на первом 7, втором 9, третьем 8, четвертом 10 и пятом 11 сумматорах частичных произведений в дополнительном коде. Полученный на выходе второго 9, четвертого 10 и пятого 11 сумматоров результат произведения в дополнительном коде необходимо скорректировать для частного случая при равенстве нулю младших разрядов множители;по старшей одночетвертой группе разрядов с помощью блока 16 коррекции. Блок Ц формирования знака осуществляет , получение знакового разряда результата произведения, представленного в дополнительном гкоде с учетом частных случаев умножения от-1012 рицательного одного из сомножителей на другой сомножитель, авный нулю, Выполнение операции умножения для положительных множимого и множителя осуществляется путем су «4ирования прямых кодов частичных произведений первого 1, второго 2, третьего 3 и четвертого k блоков памяти на первом 7, втором 9, третьем 8, четвертом tO и пятом 11 сумматорах без компенсации на шестом 12 и седьмом 1 сумматорах. При умножении отрицательного множимого на положительный NWOжитель вьаюлняется суммирование на тех же cytwaTopax, но уже по значению дополнительных кодов частичных произведений от прежних первого 1, второго 2, второго выхода третьего 3 и первого выхода четвертого k блоков памяти и дополнительных кодов по старшей половине разрядов от пятого 5 и шестого 6 блоков памяти, результат произведения не требует компенсации « на шестом 12 и седьмом 13 сумматорах, так как множитель положителен, и проходит на выход устройства без измене- , ния. При умножении положительного множимого на отрицательный множитель работа устройства происходит в тсж же порядке, как и для случая положительных сомножителей , за исключением введения в работу в этом случае компенсации результата прюизведения, которая осуществляется на шестом 12 и ; седьмом 13 сумматорах. При умножении отрицательных и множимого и множ :Теля устройство работает как и в случае отрицательного множимого и положительного множителя, за искгвочением введения в работу для этого случая компенсации результата произведения, которая осуществляется на шестом 12 и седьмом 13 сумматорах. I. - - . Технико-экономическая эффективность изобретения заключается в следующем. В предлагаемом устройстве для ytwoжения из-за того, что дополнительно введеные пятый и шестой блоки памяти, блок коррекции, блок формирования знака- включены параллельно с блоками известного устройства, практически не вносится дополнительная временная задержка во время перемножения сомножителей. Последовательно вклочен, ные с блоками известного устройства шестой и седьмой сумматоры, также не вносят существенной дополнительной. временной задержки, так как из-за изменения взаимных связей между первым.

вторым, третьим и четвертым сумматорами по цепи переноса временная задержка, вносимая во время перемножения от суммирования частичных произведений на первом, втором, третьем, четвертом, пятом, шестом и седьмом сумматорах, меняется незначительно. Дополнительные аппаратурные затраты двух разрядных кодов, сомножителей при реализации устройства для умножения для блока коррекции (фиг. 3)t блока формирования знака (фиг. 2), блока инверсии (фиг. А) составляют: одна микросхема 133ЛЕЗ,одна микросхема 133ИМ2, одна микросхема 133ЛДЗ, две микросхемы 133ЛЕ1, одна микросхема 133ЛРЗ, кроме этого, для реализации шестого и седьмого сумматоров необходимо две микросхемы 133ИМЗ, для реализации пятого и шестого блоков памяти - две микросхемы K556PTt, и одна Микросхема 133ЛН1 - для первого и второго элементов НЕ. Всего требуется дополнительно 11 корпусов микросхем.

Оценивая полную реализацию устройства для расс атриваемого примера, когда его функциональные блоки выполнены на микросхемах 133 сег рии, а блоки памяти - на микросхемах ПЗУК55бРТ4, можно привести следующие его характеристики: общее необходимое число корпусов микросхем 2k, размеры монтажной платы 13 X 13 см, достижимое быстродействие 282 НС, потребляемая мощность не более 7,5 Вт.

Предлагаемое устройство для умножения вычисляет произведения чисел не только в прямых кодах, но и в дополнительных, имеет соизмеримое с из вестным устройством быстродействие и незначительное увеличение объекта аппаратуры, необходимое для реализации новых функций.

Фиг.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Устройство для умножения | 1982 |

|

SU1059569A1 |

| Устройство для умножения | 1985 |

|

SU1315970A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Последовательное множительное устройство | 1985 |

|

SU1307455A1 |

| Устройство для умножения | 1985 |

|

SU1309019A1 |

| Устройство для умножения | 1985 |

|

SU1290301A1 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

IP

Авторы

Даты

1983-05-23—Публикация

1981-12-24—Подача