Изобретение относится к вычислительной технике, -может быть использовано в устройствах контроля при передаче цифровой информации из ЭВМ в периферийные устройства и является усовершенствованием устройства по авт.св. № 1051541.

. Цель изобретения - повьппение достоверности передачи информации.

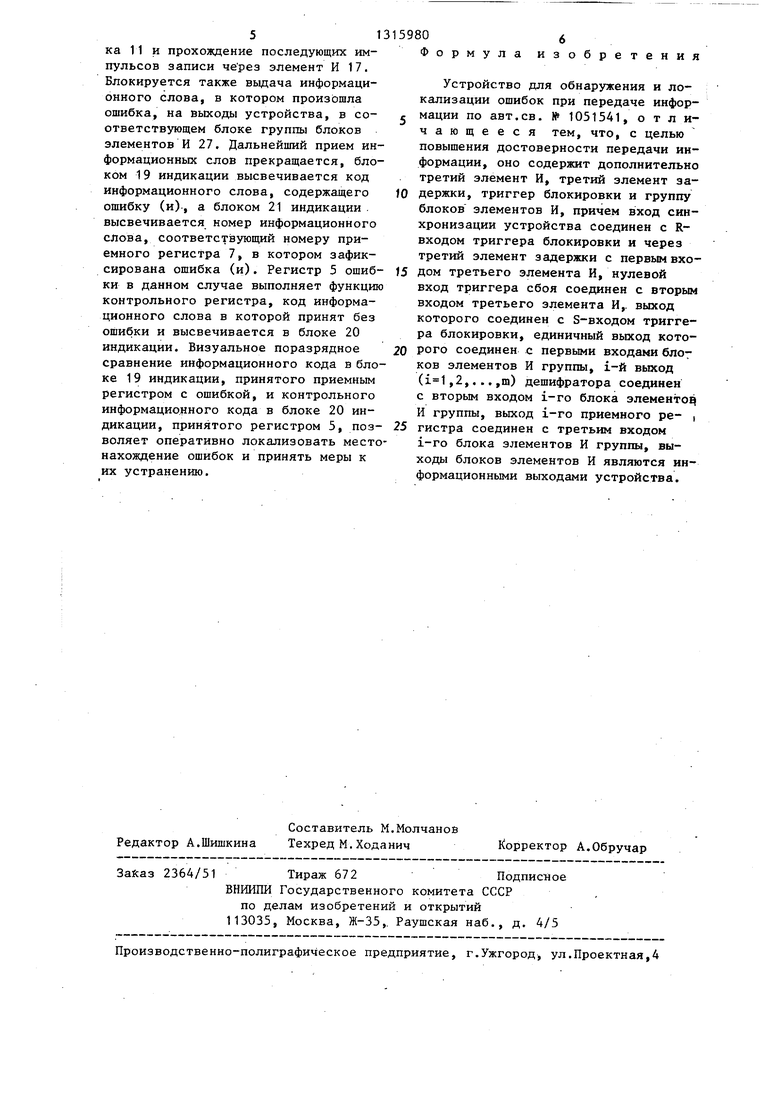

На чертеже приведена схема устройства для обнаружения и локализации ошибок при передаче информации.

Устройство содержит входной регистр 1, блоки 2 и 3 сверток по модулю два, схему 4 сравнения контроль ных разрядов, регистр 5 ошибки, дешифратор 6, группу из m приемных регистров 7, регистр 8 контрольных разрядов, схему 9 сравнения информационных разрядов, коммутатор 10, сче чик 11, триггер 12 сбоя, элементы 13 и 14 задержки, элемент ИЛИ 15, элемент И-НЕ 16, элементы И 17 и 18, блоки 19-21 индикации, вход 22 синхронизации, вход 23 сброса, элемент 24 задержки, элемент И 25, триггер 26 блокировки, группу из га блоков 27 элементов И.

Введение дополнительного элемента задержки, элемента И, триггера блокировки и блока элементов И исключает передачу на выход устройства информационного слова, в котором имеются одиночные или многократные ошибки. Искаженная информация не будет передана периферийному устройству от ЭВМ, тем самым исключается его неправильное функционирование. Такая блокировка выдачи информационного слова с приемных регистров повьшает достоверность передачи информации от ЭВМ в периферийные устройства.

Устройство работает следующим образом.

Импульс сброса, поступающий на вход 23 устройства, устанавливает в исходное состояние группу из ш приемных регистров 7, регистр 5 ошибки, двоичный счетчик 11, триггер 12 сбоя и регистр 8, при этом на инверсном выходе триггера 12 сбоя устанавливается единичный логический уровень, сигнализирующий об отсутствии сигнала сбоя и разрешающий прохождение импульсов записи, поступающих по входу 22 синхронизации через элемент И 17. С первого выхода дешифратора 6 поступает единичный логический уровень на управляющий вход приемно

1315980

5 0

0

0

го регистра 7.1, подготавливая его к приему информации с входного регистра 1, при этом на управляющие входы остальных приемных регистров 7 с выходов дешифратора 6 подаются нулевые логические уровни, запрещающие прием информации. Коммутатор 10 подключает информационные выходы приемного регистра 7.1 к первым входам схемы 9 сравнения и к входам блока 19 индикации, при этом транспо- ранты блоков 19 - 21 индикации высвечивают нулевой код.

В общем случае запись информации с регистра 1 в приемные регистры 7.1 - 7.ш производится поочередно в виде информационных слов, сопровождаемых импульсами записи по входу 22 синхронизации устройства.

Управление поочередной записью . информационных слов в приемные регистры 7.1 - 7.га производится двоичным счетчиком 11 через дешифратор 6 следующим образом. По заднему фронту 5 первого импульса записи информационное слово с выхода регистра 1 заносится в приемный регистр 7.1 и регистр 5 ошибки. Этот же импульс записи, задержанный элемент;ом 13 задер-. жки на время срабатывания приемного регистра 7„1, коммутатора 10 и схемы 9 сравнения, поступает на вход счетчика 11 через элемент 14 задержки и элемент И 18. Информационное 1,

слово с выхода приемного регистра 7.1 поступает через коммутатор 10 на схему 9 сравнения, где поразрядно сравнивается с информационньм словом, поступающий на информационные входы приемного регистра 7.1. По заднему фронту первого импульса записи триггер 26 блокировки устанавливается по R-входу в нулевое состояние, тем самым блокируя на время поразрядного

5 сравнения выдачу информационного слова через соответствующий блок элементов И 27, I на выходы устройства.

При положительном результате контроля на выходе схемы 9 поразрядного

Q сравнения так же, как и на выходе

схемы 4 сравнения контрольных разря- - дов, сохраняется нулевой логический уровень, который поступает через элемент ИЛИ 15 на элемент И-НЕ 16,

5 на выходе которого сохраняется единичный логический уровень, при этом триггер 12 сбоя остается в исходном состоянии. При положительном результате поразрядного контроля первый i

5

импульс записи, задержанный элементом 24 задержки на вермя контроля, через открытый элемент И 25 переводят триггер 26 блокировки в единично состояние. Информационное слово с первого приемного регистра 7.1 через открытые элементы И 27.1 первой группы блока передается на выход устройства.

По заднему фронту первого импульса записи, задержанного элементами 13 и 14 задержки, в двоичный счетчик 11 добавляется единица и счетчик 11 переводится в следующее (второе) состояние, при этом к схеме 9 сравнения через коммутатор 10 подключаются выходы следующего приемного регистра (7.2), на управляющий вход которого с второго выхода дешифратора 6 поступает единичный логический уровень, разрешающий прием (запись) информации. На управляющие входы остальных приемных регистров поступает нулевой логический уровень, блокирующий прием информации.

По заднему фронту второго импульса записи следующее информационное слово с выхода передающего регистра 1 заносится в приемный регистр 7.2 и в регистр 5 ошибки. В дальнейшем аналогично описанному производится поразрядное сравнение информационного слова, записанного в приемный регистр 7.2,с инфомационным словом, поступающим на его вход, и выдача его при положительном сравнении на выход устройства.

Обнаружение и локализация ошибок в устройстве производится по двум направлениям: непосредственно при передаче информационного слова и при приеме (записи) его в приемные регистры 7.1 - 7.т.

В первом случае производится кон- троль с целью обнаружения однократных ошибок, возникающих при передаче информационного слова с выхода передающего регистра 1. Контроль осуществляется блоками 2 и 3 сверток по модулю два и схемой 4 поразрядного сравнения контрольных разрядов. При наличии однократной ошибки в информационном слове на выходе схемы 4 сравнения контрольных разрядов формируется единичный логический уровень, который поступает через элемент ИЛИ 15 на вход элемента И-НЕ 16, где стробируется по его другому

O

0

5

входу задержанным импульсом записи единичного уровня с выхода элемента 13 задержки. При совпадении единичных логических уровней на входах элемента И-НЕ 16 на его выходе формируется нулевой логический уровень, под действием которого срабатывает триггер 12 сбоя, в результате чего блокируется прохождение данного импульса записи с выхода элемента 14 задержки через элемент И 18 на счетный вход двоичного счетчика и блокируется прохождение последующих импульсов записи через элемент И 17.

5 В этом случае данный импульс записи, задержанньш элементом 24 задержки на время контроля, не проходит через элемент И 25 и триггер 26 блокировки остается в нулевом состоянии, тем самым блокируется прохождение информационного слова, в котором обнаружена ошибка, на выход устройства. Дальнейший прием информационных слов в регистре (7.1 - 7.т) прекращается. В регистре 5 ошибки фиксируется информационное слово, содержащее однократную ошибку, код которого высвечивается блоком 20 индикации, а блоком 21 индикации высвечивается номер

0 информационного слова, в котором обнаружена ошибка. Блоком 19 индикации при этом высвечивается код этого же информационного слова, но записанный приемным регистром 7 на момент

г обнаружения однократной ошибки. Идентичность кодов в блоках 19 и 20 индикации -указывает на достоверность приема регистром 5 ошибки информационного слова, содержащего однократную ошибку,

0

0

5

Во втором случае производится контроль с целью обнаружения многократных ошибок, возникающих при записи (выдаче) приемным регистром 7. Контроль произв-одится схемой 9 сравнения, с выхода которой при отрицательном результате сравнения формируется единичный логический уровень, поступающий через элемент ИЛИ 15 на вход элемента И-НЕ 16, где также стробируется по его другому входу задержанным импульсом записи. На выходе элемента И-НЕ 16 появляется нулевой логический уровень, под действием которого срабатывает триггер 1 2 сбоя, формирует сигнал Сбой, блокирующий прохождение импульса записи на счетный вход двоичного счетчика 11 и прохождение последующих импульсов записи че рез элемент И 17. Блокируется также выдача информационного слова, в котором произошла ошибка, на выходы устройства, в соответствующем блоке группы блоков элементов И 27. Дальнейший прием информационных слов прекращается, блоком 19 индикации высвечивается код информационного слова, содержащего ошибку (и), а блоком 21 индикации . высвечивается номер информационного слова, соответствующий номеру приемного регистра 7, в котором зафикФормула и

3 о б р

е т е н

0

Устройство для обнаружения и л кализации ошибок при передаче инф мации по авт.св. № 1051541, о т л чающееся тем, что, с цель повышения достоверности передачи формации, оно содержит дополнител третий элемент И, третий элемент держки, триггер блокировки и груп блоков элементов И, причем вход с хронизации устройства соединен с входом триггера блокировки и чере третий элемент задержки с первым в

сирована ошибка (и). Регистр 5 ошиб- )5 дом третьего элемента И, нулевой

ки в данном случае выполняет функцию контрольного регистра, код информационного слова в которой принят без ошибки и высвечивается в блоке 20 индикации. Визуальное поразрядное сравнение информационного кода в блоке 19 индикации, принятого приемным регистром с ошибкой, и контрольного информационного кода в блоке 20 индикации, принятого регистром 5, позволяет оперативно локализовать местонахождение ошибок и принять меры к их устранению.

Редактор А.Шишкина Заказ 2364/51

Составитель М.Молчанов Техред М. Ходанич

Корректор

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35,. Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Формула и

6

3 о б р

е т е н и я

Устройство для обнаружения и локализации ошибок при передаче информации по авт.св. № 1051541, о т л и- чающееся тем, что, с целью повышения достоверности передачи информации, оно содержит дополнительно третий элемент И, третий элемент задержки, триггер блокировки и группу блоков элементов И, причем вход синхронизации устройства соединен с R- входом триггера блокировки и через третий элемент задержки с первым вховход триггера сбоя соединен с вторым входом третьего элемента И,, выход которого соединен с S-входом триггера блокировки, единичный выход которого соединен с первыми входами блоков элементов И группы, i-й выход (,2,...,т) дешифратора соединен с вторьм входом i-ro блока элементов И группы, выход i-ro приемного ре- i

гистра соединен с третьим входом i-ro блока элементов И группы, выходы блоков элементов И являются информационными выходами устройства.

Корректор А.Обручар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Устройство для обнаружения ошибок при передаче информации | 1988 |

|

SU1547078A1 |

| Устройство для фиксации сбоев электронно-вычислительной машины | 1981 |

|

SU962913A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ИЗМЕРЕНИЯ ХАРАКТЕРИСТИК ДИСКРЕТНОГО КАНАЛА СВЯЗИ | 1995 |

|

RU2138910C1 |

| Устройство для автоматического контроля больших интегральных схем | 1985 |

|

SU1249518A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1234841A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И КОРРЕКЦИИ ОШИБОК В ПАРАЛЛЕЛЬНОЙ МАГИСТРАЛИ | 2013 |

|

RU2524854C1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

Изобретение относится к вычислительной технике, может быть использовано в устройс твах контроля при передаче цифровой информации из ЭВМ в периферийные устройства и является усовершенствованием изобретения по а.с. № 1051541. Цель изобретения- повышение достоверности передачи информации. Достижение цели обеспечивается введением в состав устройства элемента 24 задержки, элемента И 25, триггера 26 блокировки,группы блоков 27.1 - 27т элементов И, которые исключают передачу на выход устройства информационного слова, в котором имеются одиночные или многократные ошибки. Искаженная информация не передается периферийному устройству от ЭВМ, тем самым исключается неправильное его функционирование. 1 ил. (Л со ел со оо N

| Устройство для обнаружения и локализации ошибок при передаче информации | 1982 |

|

SU1051541A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-25—Подача