113

Изобретение относится к вычислительной технике и- может быть использовано для контроля обмена информацией между управляющим и операционным автоматами, между источником информации и устройствами, обработки.

Целью изобретения является повышение достоверности контроля и расширение функциональных возможностей устройства для контроля.

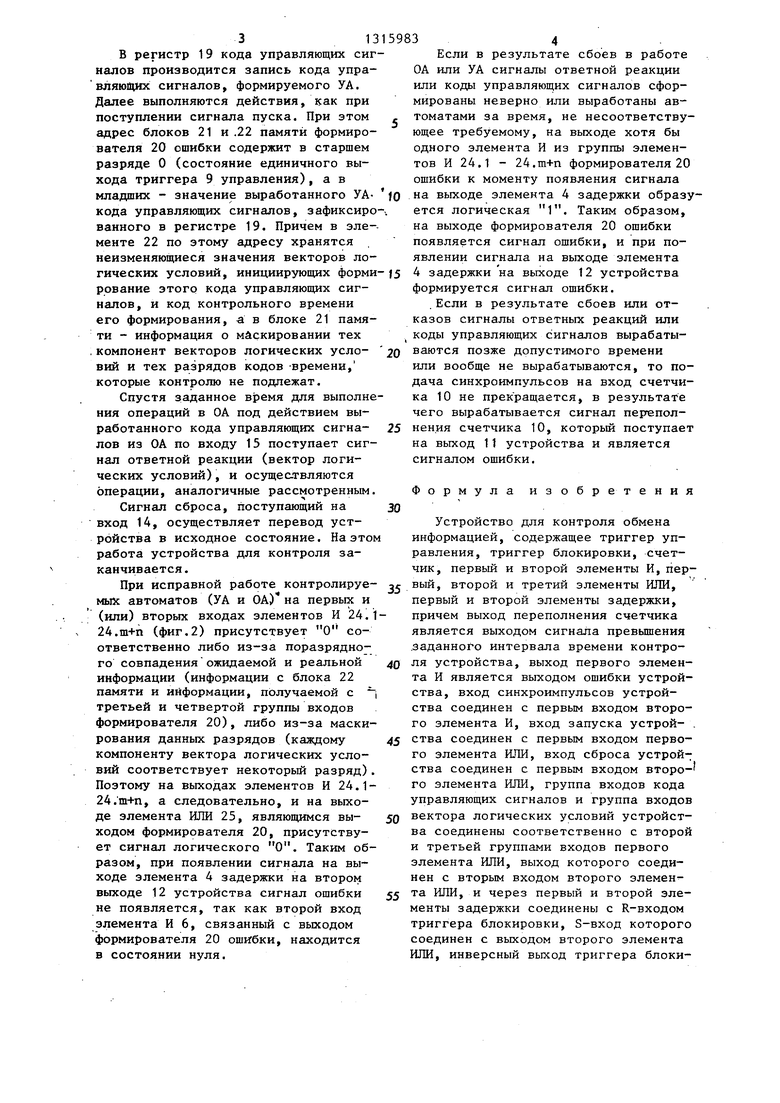

На фиг.1 приведена схема устройства-, на фиг.2 - схема формирователя ошибки.

Устройство для контроля содержит первый 1, второй 2 и третий 3 эл гмен- ты ИЛИ, первый 4 и второй 5 элементы задержки, первый 6 и второй 7 элементы. И, триггер 8 блокировки, триггер 9 управления, счетчик 10, выход 11 сигнала превьшения заданного интервала времени контроля, выход 12 ошибки устройства, вход 13 синхронизации устройства, вход 14 сброса устройства, группу входов 15 вектора логических условий, группу входов 16 задания времени контроля, вход 17 пуска, регистры 18 и 19, формирователь 20 ошибки.

Формирователь 20 ошибки содержит первый 21 И второй 22 блоки памяти, m+n элементов ИСКЛЮЧАЩЕЕ ИЛИ 23.1 -f 23.m+n, m+n элементов И 24. 1-24.m+n элемент ИЛИ 25.

Устройство для контроля работает следующим образом.

В исходном состоянии сигналом Конец работы с входа 14 устройства триггер 8 блокировки и триггер 9 управления устанавливаются в единичное состояние, счетчик 10 и регистры 18 и 19 обнуляются. Элемент И 7 закрыт сигналом с нулевого выхода триггера 8 блокировки для прохождения через него синхроимпульсов с входа 13 устройства на суммирующий вход счетчика 10.

Из УА по входу 17 устройства сигнал пуска через первый элемент ИЛИ 1 поступает на синхронизирующий вход триггера 9 управления, переводя его в нулевое состояние, при этом по сигналу с нулевого выхода триггера 9 управления осуществляется запись в регистр 19 кода управляющих сигналов (КУС), формуемого УА. В случае выработки УА сигнала пуска на входы кода управляющих сигналов устройства поступает нулевой код.

32

Кроме того, сигнал пуска через первый 1 и второй 2 элементы ИЛИ поступает на единичный вход триггера 8 блокировки и устанавливает его в

единичное состояние, в результате чего закрывается элемент И 7 для прохождения синхроимпульсов на суммирующий вход счетчика 10.

Через элемент ИЛИ 1, элемент 4

задержки, элемент ИЛИ 3 сигнал пуска поступает на вход сброса счетчика 10 и обнуляет его. Через время, равное времени формирования сигнала ошибки формирователем 20 ошибки, сигнал с

выхода элемента 4 задержки через элемент 5 задержки поступает на нулевой вход триггера 8 и устанавливает его в нулевое состояние. При этом открывается элемент И 7, и синхроимпульсы через элемент И 7 поступают на суммирующий вход счетчика 10.

Спустя заданное время для выполнения операций в ОА по сигналу пуска УА из ОА по входу 15 поступает сигнал ответной реакции ОА (вектор логических условий), который через первый элемент ИЛИ 1 поступает на синхронизирующий вход триггера 9 управления, переводя его- в единичное

состояние. При этом по сигналу с единичного выхода триггера 9 управления осуществляется запись в регистр 18 значения вектора логических условий, выдаваемого ОА. Адрес блоков 21 и 22

ламяти формирователя 20 ошибки с одер- жит в старшем разряде 1 (состояние j единичного выхода триггера 9 управ- ), а в младших - значение текущего кода управляющих сигналов, зафиксированного в регистре 19, причем в блоке 22 по этому адресу хранятся неизменяющиеся значения векторов логических условий и код контрольного времени выполнения операций для

данного кода управляющих сигналов, а в элементе 21 - информация о маскировании тех компонентов векторов логических условий и тех разрядов кодов времени, которые контролю не подлежат. Далее выполняются действия аналогичные действиям при поступлении сигнала пуска.

Спустя заданное время для выработки УА нового кода управляющих сигналов, соответствующего поступившему на него вектору логических условий, УА выдает по входу 16 код управляю- щтл-к. сигналов, по которому осуществляется следующее.

В регистр 19 кода управляющих сигналов производится запись кода упра- вляюЩИх сигналов, формируемого УА. Далее выполняются действия, как при поступлении сигнала пуска. При этом адрес блоков 21 и .22 памяти формирователя 20 ошибки содержит в старшем разряде О (состояние единичного выхода триггера 9 управления), а в младших - значение выработанного УА- кода управляющих сигналов, зафиксиро ванного в регистре 19. Причем в элементе 22 по этому адресу хранятся неизменяющиеся значения векторов логических условий, инициирующих форми ррвание этого кода управляющих сигналов, и код контрольного времени его формирования, а в блоке 21 памяти - информация о маскировании тех .компонент векторов логических уело- ВИЙ и тех разрядов кодов -времени, которые контролю не подлежат.

Спустя заданное время для выполнения операций в ОА под действием выработанного кода управляющих сигна- лов из ОА по входу 15 поступает сигнал ответной реакции (вектор логических условий), и осуществляются операции, аналогичные рассмотренным

Сигнал сброса, поступающий на вход 14, осуществляет перевод устройства в исходное состояние. На это работа устройства для контроля заканчивается.

При исправной работе контролируе- мых автоматов (УА и ОА) на первых и (или) вторых входах элементов И 24. 24.m+n (фиг.2) присутствует О соответственно либо из-за поразрядного совпадения ожидаемой и реальной информации (информации с блока 22 памяти и информации, получаемой с третьей и четвертой группы входов формирователя 20), либо из-за маскирования данных разрядов (каждому компоненту вектора логических условий соответствует некоторый разряд). Поэтому на выходах элементов И 24.1- 24. m+n, а следовательно, и на выходе элемента ИЛИ 25, являющимся вы- ходом формирователя 20, присутствует сигнал логического О. Таким образом, при появлении сигнала на выходе элемента 4 задержки на втором выходе 12 устройства сигнал ошибки не появляется, так как второй вход элемента И 6, связанный с выходом формирователя 20 ошибки, находится в состоянии нуля.

Если в результате сбоев в работе ОА или УА сигналы ответной реакции или коды управляющих сигналов сформированы неверно или выработаны автоматами за время, не несоответствующее требуемому, на выходе хотя бы одного элемента И из группы элементов И 24.1 - 24.m+n формирователя 20 ошибки к моменту появления сигнала на выходе элемента 4 задержки образуется логическая 1. Таким образом, на выходе формирователя 20 ошибки появляется сигнал ошибки, и при появлении сигнала на выходе элемента 4 задержки на выходе 12 устройства формируется сигнал ошибки.

.Если в результате сбоев или отказов сигналы ответных реакций или коды управляющих сигналов вырабатываются позже допустимого времени или вообще не вырабатываются, то подача синхроимпульсов на вход счетчика 10 не прекращается, в результате чего вырабатывается сигнал переполнения счетчика 10, который поступает на выход 11 устройства и является сигналом ошибки.

Формула изобретения

Устройство для контроля обмена информацией, содержащее триггер управления, триггер блокировки, счетчик, первый и второй элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы задержки, причем выход переполнения счетчика является выходом сигнала превышения .заданного интервала времени контроля устройства, выход первого элемента И является выходом ошибки устройства, вход синхроимпульсов устройства соединен с первым входом второго элемента И, вход запуска устрой- ства соединен с первьм входом первого элемента ИЛИ, вход сброса устройства соединен с первым входом второ- го элемента ИЛИ, группа входов кода управляющих сигналов и группа входов вектора логических условий устройства соединены соответственно с второй и третьей группами входов первого элемента ИЛИ, выход которого соединен с вторым входом второго элемента ИЛИ, и через первый и второй элементы задержки соединены с R-входом триггера блокировки, S-вход которого соединен с выходом второго элемента ИЛИ, инверсный выход триггера блоки5,

ровки соединен с вторым входом второго элемента И, выход первого,элемента задержки соединен с первым входом первого элемента И, о т л и- ч а ю щ- е е с я тем, что, с целью повышения достоверности контроля, оно содержит первый и второй регистры и формирователь ошибки, причем прямой , выход триггера управления соединен с входом синхронизации первого регистра и входом выбора режима формирователя ошибки, инверсный выход триггера управления соединен с информационным входом триггера управления, с входом синхронизации второго регистра, вход синхронизации триггера управления соединен с выходом первого элемента ИЛИ, S-вход триггера управления соединен с первым входом второго элемента ИЛИ, с первьи входом третьего элемента ИЛИ и с входами установки в О первого и второго регистров, выход второго элемента И соединен со счетным входом счетчика, вход установки в О которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемен та задержки, группа информационных входов первого регистра подключена к группе входов вектора логических условий устройства, группа информаци онных входов второго регистра подключена к группе входов кода управляющих сигналов устройства, группа разрядных выходов второго регистра соединена с первой группой входов формирователя ошибки, вторая группа

159836

входов которого соединена с группой разрядных выходов первого регистра, третья группа входов формирователя ошибки соединена с группой выходов счетчика, выход формирователя ошибки соединен с вторым входом первого элемента И, формирователь ошибки содержит два блока памяти, группу из (m+n) элементов И (п - число разря(0 дов счетчика, m - разрядность), элемент ИЛИ, группу из (m+n) элементов ИСКЛЮЧАЩЕЕ ИЛИ, причем старший разряд адресных входов блоков памяти подключен к входу выбора режима фор-

J5 мирователя, младшие разряды адресных входов блоков памяти объединены и образуют первую группу информационных входов формирователя ошибки, первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

20 группы с первого по ш-й образуют вторую группу информационных входов формирователя, первые входы элементов ИСКЛЮЧАЩЕЕ ИЛИ группы с (т4-1)-го по (m+n)-и образуют третью группу

25 информационных входов формирователя, вторые входы элементов ИСКЛЮЧАЩЕЕ ИЖ группы с первого по (m+n)-и подключены к группе выходов второго блока памяти, выходы всех элементов

30 ИСКЛЮЧАЩЕЕ ИЛИ группы подключены к первым входам соответствующих элементов И группы, вторые входы которых подключены к группе выходов первого блока памяти, выходы элементов И группы подключены к соответствующим

35

входам элементов ИЛИ, выход которого является вьпсодом формирователя.

Редактор Л.Лангазо Заказ 2364/51

Составитель М.Молчанов

Техред М.Ходанич Корректор с.Черни

Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственнл-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

atZ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ | 1991 |

|

RU2029986C1 |

| Устройство для контроля | 1986 |

|

SU1396145A2 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Устройство для тестового контроля цифровых блоков | 1985 |

|

SU1312577A1 |

| Устройство для регистрации информации | 1989 |

|

SU1603412A1 |

| Устройство для контроля обмена информацией | 1989 |

|

SU1683018A1 |

| Устройство для контроля цифровых блоков | 1988 |

|

SU1661768A1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Микропрограммное устройство управления модуля вычислительной системы | 1982 |

|

SU1034037A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

Изобретение относится к вычислительной технике и может быть исполь/J зовано для обмена информацией между источником (получателем) информации и устройствами обработки. Цель изобретения заключается в повышении достоверности контроля. Устройство содержит первый, второй и третий элементы ИЛИ 1, 2, 3, первый и второй элементы задержки 4, 5, первый и второй элементы И 6, 7, триггер 8 блокировки, триггер 9 управления, счетчик 10, первый и второй регистры 18, 19 и формирователь 20 ошибки. Сущность изобретения состоит в том, что контроль информации осуществляется по временному и информационному параметрам. 2 ил. а S (Л 7/ 00 О1 со 00 со

| Устройство для контроля цифровых блоков | 1980 |

|

SU960826A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля микропрограммного автомата | 1979 |

|

SU883911A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-07—Публикация

1985-12-24—Подача