Изобрет.ение относится к области вычислительной техники и может быть использовано при создании интегральных полупроводниковых схем памяти.

Цель изобретения - повышение быстродействия усилителя считывания.

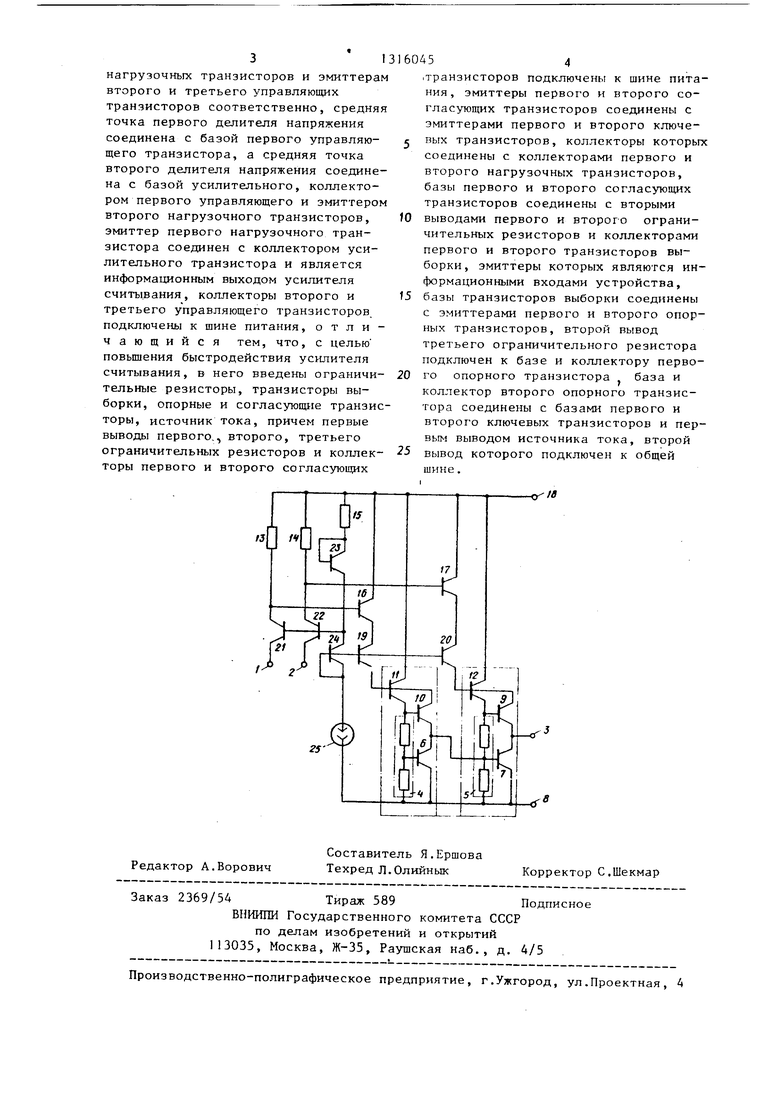

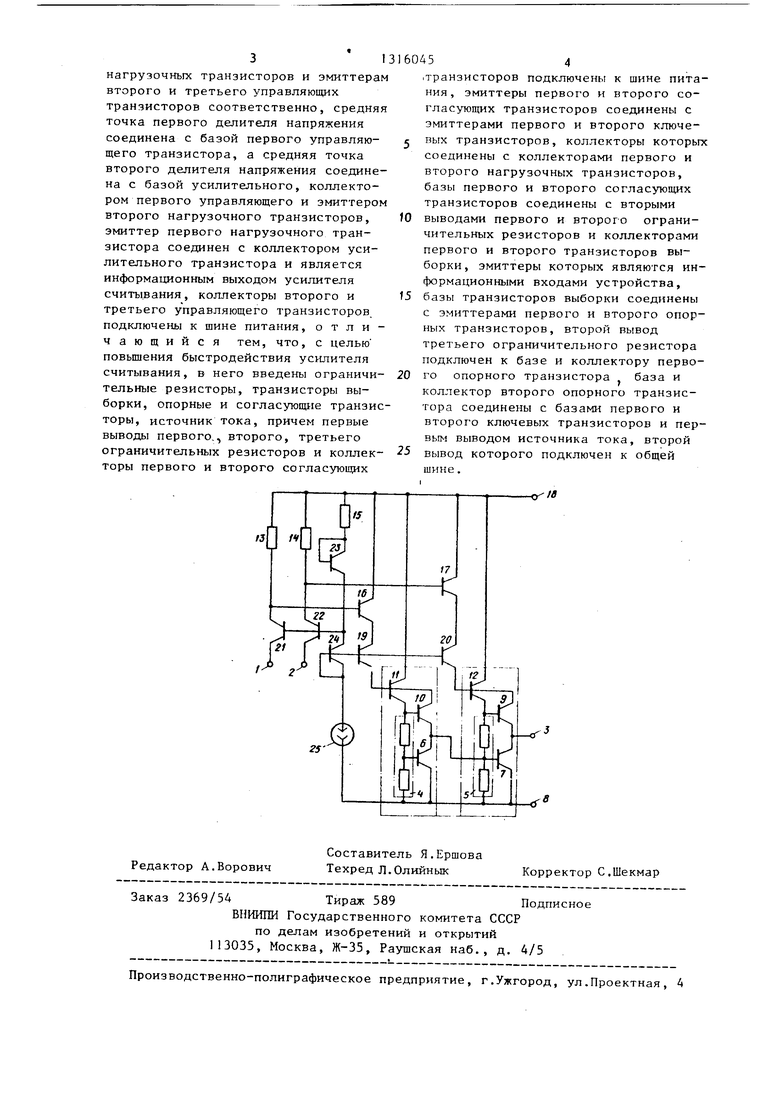

На чертеже представлена принципиальная схема усилителя считычания.

Усилитель считывания содержит информационные входь1 1 и 2, информационный выход 3 усилителя считывания, делители Д и 5 напряжения, каждый из которых состоит из двух резисторов, первые выводы делителей напряжения и эмиттеры первого управляющего 6 и ус лительного 7 транзисторов подключены к общей шине 8, вторые выводы делителей 4 и 5 напряжения подключены к базам первого 9 и второго 10 нагрузочных транзисторов и эмиттерам второго 11 и третьего 12 управляющих транзисторов, средняя точка первого 4 делителя напряжения соединена с базой первого 6 управляющего транзистора, а средняя точка второго 5 делителя напряжения соединена с баЗОЙ усилительного 7, коллектором первого 6 управляющего и эмиттером второго 11 нагрузочного транзисторов, эмиттер первого 9 нагрузочного транзистора соединен с коллектором 7 усилительного транзистора и является информационны выходом усилителя счигывания, коллекторы второго 11 и третьего 12 управляющих транзисторов, первые выводы первого 13, второго 14 и третьего 15 резисторов и коллекторы первого 16 н второго 17 согласующих транзисторов подключены к шине 18 питания, эмиттеры первого 16 и второго 17 согласующих транзисторов соединены с эмиттерами первого 19 и второго 20 ключевых транзисторов, коллекторы которых соединены с коллекторами первого 9 и второго 10 нагрузочных транзисторов, базы первого 16 и второго 17 согласующих транзисторов соединены с вторыми выводами первого 1 3 и второго 14 резисторов и коллекторами первого 21 и второго 22 транзисторов выборки, эмиттеры которых являются информационными входами 1 и 2 устройства, базы транзисторов 21 и 22 выборки соединены с эмиттерами первого 23 и второго 24 опорных транзисторов, второй вывод третьего 15 резистора подключен к

o

5

0

5

0

35

0

45

0

55

базе и коллектору первого опорного транзистора, бауа и коллектор второго 24 опорного транзистора соединены с базой первого 19 и второго 20 ключевых транзисторов и источником 25 тока, вь1вод которого подключен к общей шине 8.

Предлагаемый усилитель считывания работает следующим образом.

При включении источника питания между шиной 18 питания и общей шИ11ой 8 протекание тока по цепи входа 1 и отсутствие тока по входу 2 образуют разность напряжений на резисторах 13 и 14 за счет того, что ток входа I передается транзистором 21 и создает падение напряжения на резисторе I З. Эмиттерные повторители на транзисторах 16 и 17 передают напряжения на эмиттеры транзисторов 19 и 20. На резисторе 5, транзисторах 23 и 24 и источнике тока 25 выполнен источник опорных напряжений Хщя баз транзисторов 19, 20 и 21, 22.

За счет того, что базы транзисторов 19 и 20 подключены к одному источнику опорного напряжения, а на их эмиттеры подаются разные напряжения, транзистор 20 открывается, а транзистор 10 закрывается, при этом открываются транзисторы 12 и 7 и сигнал попадает на выход 3 усилителя считывания. При понижении напряжения на коллекторе транзистора 7 до заданной величины включается транзистор 9 и забирает часть тока базовой цепи транзистора 12, ограничивает тем самым ток базы транзистора 7 и степень его насыщения. Величина напряжения на коллекторе транзистора 7 задается соотношением резисторов делителя 5.

При отсутствии тока по входу 1, протекании тока по цепи входа 2 соответственно открывается транзистор 19 и транзисторы 11, 10 и 6. При этом транзистор 6 шунтирует базовую цепь транзистора 7 и ускоряет его выключение. Формула изобретения

Усилитель считывания, содержащий усилительный, управляюп ие, нагрузочные, переключающие транзисторы, делители напряжения, первые выводы каждого из которых и эмиттеры первого управляюгцего и усилительного транзисторов подключены к общей шине, вторые Рыводы делителей напряжения подключены к базам первого и второго

31

нагрузочных транзисторов и эмиттерам второго и третьего управляющих транзисторов соответственно, средняя точка первого делителя напряжения соединена с базой первого управляющего транзистора, а средняя точка второго делителя напряжения соединена с базой усилительного, коллектором первого управляющего и эмиттером второго нагрузочного транзисторов, эмиттер первого нагрузочного транзистора соединен с коллектором усилительного транзистора и является информационным выходом усилителя считывания, коллекторы второго и третьего управляющего транзисторов, подключены к шине питания, отличающийся тем, что, с целью повьш1ения быстродействия усилителя считывания, в него введены ограничительные резисторы, транзисторы выборки, опорные и согласующие транзисторы, источник тока, причем первые выводы первого,, второго, третьего ограничительнь1х резисторов и коллекторы первого и второго согласующих

54

,транзисторов подключены к шине питания, эмиттеры первого и второго согласующих транзисторов соединены с эмиттерами первого и второго ключевых транзисторов, коллекторы которых соединены с коллекторами первого и второго нагрузочных транзисторов, базы первого и второго согласующих транзисторов соединены с вторыми

выводами первого и второго ограничительных резисторов и коллекторами первого и второго транзисторов выборки, эмиттеры которых являются информационными входами устройства,

базы транзисторов выборки соединены с эмиттерами первого и второго опорных транзисторов, второй вывод третьего ограничительного резистора подключен к базе и коллектору первого опорного транзистора база и коллектор второго опорного транзистора соединены с базами первого и второго ключевых транзисторов и первым выводом источника тока, второй

вывод которого подключен к общей шине.

Редактор А.Ворович

Составитель Я.Ершова Техред Л.Олийнык

Заказ 2369/54Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь сигналов для усилителя считывания | 1986 |

|

SU1334177A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1508280A1 |

| Преобразователь сигналов для усилителя считывания | 1984 |

|

SU1244716A1 |

| Преобразователь уровня сигнала для усилителя считывания | 1983 |

|

SU1134966A1 |

| Формирователь сигналов считывания | 1984 |

|

SU1238152A1 |

| Преобразователь уровня для усилителя считывания | 1987 |

|

SU1492381A1 |

| Усилитель считывания | 1989 |

|

SU1658209A1 |

| Усилитель считывания | 1983 |

|

SU1104581A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Усилитель считывания | 1983 |

|

SU1132364A1 |

Изобретение относится к области вычислительной техники и может быть использовано при создании интегральных полупроводниковых схем памяти. Цель изобретения -повышение быстродействия усилителя считывания .Цель достигается тем,что в него введены транзисторы выборки, - ключевые и опорный управляющие транзисторы, включенные по схеме с общей базой, имеющей большее быстродействие, чем схема с общим эмиттером. 1 ил. 00 а сл

| Усилитель считывания | 1978 |

|

SU664221A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Усилитель считывания | 1983 |

|

SU1104581A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-07—Публикация

1986-01-27—Подача