роденствия устройства. Устройство содержит накопитель 1, регистры 2, счетчик 3 адреса записи, счетчики 4.-4 . считывания, блок 5 задания

1 m Приоритетов обращений, счетчики рп СЛОВ. Элементы И 7, триггеры , управления сигналом обращения, .дешифраторы ,, триггеры управления формированием гщ- tpeca считывания, дополнительные элементы И 1Ц-11, блоки 12 - элементов И, эл.ементы задержки, блоки элементов НЕ,

1

Изобретение относится к вычислительной технике, а именно к запоми- наю1(им устройствам, и может быть использовано в системах сбора, пере- дачи и обработки информации.

Цель изобретения - повышение быстродействия устройства.

Сущность изобретения заключается в следующем. Заполнение накопителя ю осуществляется словами, записьшаемы- ми ;- последовательно формируемым адресам При появлении первого слова для какого-то из направлений его адрес фиксируется в соответствующем 15 счетчике адреса считывания, а в счетчике слов фиксируется величина сво- одного массива накопителя (в словах), пределах которого будет записываться информация данного направления Та- 20 КИМ образом, при считьшании информации по одному из запросов (направлений) нет необходимости перебирать все адреса, начиная с нулевого, Достаточно осуществить поиск, начиная 25 с адреса первого слова данного на--, правления.

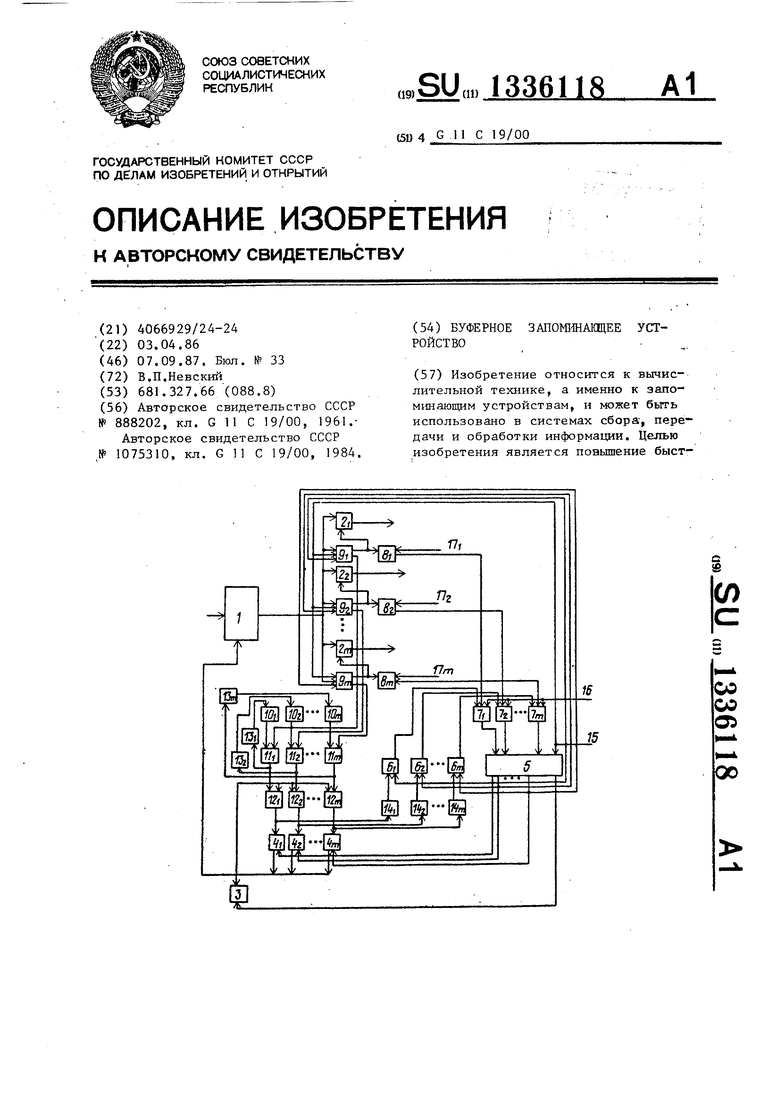

На чертеже изображена функциональная схема устройства.

Устройство содержит накопитель 1, 30 регистры 2,1-2п, счетчик 3 адреса записи, счетчики 4,1-4т адресов считывания, блок 5 задания приоритетов обращений, счетчики 6,1-6т слов, элементы И 7,1-7т, триггеры 8,1-8т в управления сигналом обращений, дешифраторы 9,1-9т, триггеры lO.l-IOm управления формированием адреса счипервый 15 и второй 16 управляющие - входы устройства, входы обращений. Устройство может осуществлять вьщачу любых наборов информационных слов на каждое из направлений по мере поступления от них запросов за информацией. При этом для обслуживания одного из направлений нет необходимости в просмотре всего объема накопителя - поиск нужной информации осуществляется, начиная с адреса первого слова соответствующего направления. 1 ил.

тывания, дополнительные элементы И 11,1-11т, блоки И 12,1-12т элементо элементы 13,1-13т задержки, блоки 14,1-14т элементов НЕ, первый 15 и второй 16 управляющие входы устройства, входы I7,I-17m запросов.

Число регистров 2, счетчиков 4 адресов считьшания, счетчиков 6 слов элементов И 7, триггеров 8 управления сигналом обращения, дешифраторов 9, триггеров 10 управления формированием адреса считывания, дополни- тельньпс элементов И II, блоков 12 элементов И, элементов 13 задержки, блоков 14 элементов НЕ, входов 17 запросов соответствует числу направлений т, по которым вьщается информация из буферного запоминающего устройства.

Число элементов в блоках 12 и 14 составляет , где п - число слов которое может быть записано в накопитель ,

Устройство работает следующим образом,

В исходном состоянии (в начале очередного сеанса обмена) триггеры 10 управления формированием адреса считывания установлены в единичное состояние, а все счетчики обнулены (цепи установа не показаны), Принадлежность слова к соответствующему выходному информационному направлению определяется по коду нескольких разрядов слова, которые поступают на дешифраторы 9 с накопителя 1,

313

При записи информации в накопитель 1 слово сопровождается управляющим сигналом на первом 15 управляюще входе устройства.

Например, поступившее слово предназначено для i-ro направления выдачи информации. В соответ ствии с кодом и управляющим сигналом на первом выходе дешифратора 91 формируется сигнал высокого уровня, который поступает на второй вход дополнительного элемента И lli,Ha первом входе которого присутствует сигнал высокого уровня с выхода триггера lOi управ ления формированием адреса считывания. Сигнал высокого уровня с выхода дополнительного элемента И 111 пог- ступает на вход элемента 131 задёрж ки и управляющие входы блока 121 элементов И, где разрешает прием информации с выхода счетчика 3 адреса записи. При поступлении сигнала на первый управляющий вход 15 уст- ройства на первом выходе блока 5 за- Дания приоритетов формируется сигнал высокого уровня, который поступает на вход счетчика 3 адреса записи и разрешает передачу его содержимого на адресньп вход накопителя 1 и информационные входа блоков 12 элементов И. Первое слово записывается по нулевому адресу , Код адреса записи первого слова 1-го направления с выходов блока 121 элементов И поступает на вторые входы счетчика 41 адреса считывания и входы блока 141 элементов НЕ. С выходов блока 141 элементов НЕ обратный код адреса записи поступает на вторые входы счетчика 61 слов.

Таким образом, в счетчике 41 адреса считывания будет зафиксирован адрес первого слова, предназначенного дпя 1-го направления (в данном случае 00...0), а в счетчике 61 слов количество слов, среди которых может оказаться информация 1-направления (в данном случае 11,..1).

Сигнал с выхода элемента 131 задержки (время задержки выбирается достаточным для занесения информации в счетчики адреса записи и счетчики слов, но меньшим времени действия сигнала на входе счетчика адреса записи) поступает на вход триггера 101 управления формированием адреса считывания и переводит его в нулевое состояние. Сигнал низкого уровня с

5 0 5

0

5

0

5

0

5

выхода триггера 101 поступает на первый вход дополнительного элемента И 111. Таким образом исключается занесение информации счетчика 3 адреса записи в счетчик адреса записи и счетчик слов при записи очередного (не первого) слова для 1-го направления. По заднему фронту сигнала, поступающего на его вхор, счетчик 3 адреса записи увеличивает свое содержимое на единицу. Очередное слово записывается по новому адресу.

Информация на запись может посту-, пать либо в виде отдельных слов, либо в виде группы слов для различных направлений. Например, для 1-го направления поступает десять слов .-, подряд, а затем следует слово для k-ro направления. В соответствии с кодом и управляющим сигналом на первом выходе дешифратора 9k формируется сигнал высокого уровня, который поступает на второй вход дополнительного элемента И Ilk, на первом входе которого присутствует сигнал высокого уровня с выхода триггера 1 Ok уп- .равления формированием адреса считывания. Сигнал высокого уровня с выхода дополнительного элемента И Ilk поступает на вход элемента 13k задержки и управляющие входы блока I2k элементов И, где разрешает прием информации с выхода счетчика 3 адреса записи. При поступлении сигнала на первый управляющий вход 15 устройства на первом выходе блока 5 задания приоритетов формируется сигнац высокого уровня, который поступает на вход счетчика 3 адреса записи и разрешает передачу его содержимого на адресный вход накопителя 1 и ин формационные входы блоков 12 элементов И, Слово записывается по данному адресу. Код адреса записи первого слова k-ro направления с выходов блока 12k элементов И поступает на вторые вход1 1 счетчика 4k адреса счи-. тывания и входы блока 14 элементов НЕ. С выходов блока 14k элементов НЕ обратный код адреса записи поступает на вторые входы счетчика 6k слов.

Таким образом, в счетчике 4k адреса считывания будет зафиксирован адрес первого слова, предназначенного для k-ro направления (в данном случае 0.,,01010), а в счетчике 6k- слов количество слов, среди которых

51

может оказаться информация k-ro направления (в данном случае 1...10101 Среди ранее.записанных (до появления первого слова k-ro направления) слов информации k-ro направления быть не можетt Сигнал с выхода элемента 13k задержки поступает на вход триггера 10k управления формированием адреса считывания и перево- дит его в нулевое состояние. Сигнал низкого уровня с выхода триггера 10 поступает на первый вход дополнительного элемента И 1 Ik, Таким образом исключается занесение информации счетчика 3.адреса записи в счетчик адреса записи и счетчик слов при записи очередного слова k-ro направления. Дальнейшее функционирование устройства при записи инфорации в накопитель аналогично рассмотренному .

В ходе записи в счетчиках 4,17т4т фиксируются адреса первых слов, а в счетчиках 6.1-6т - количество слов, в пределах кбторьк может находиться информация соответствующих направлений .

Как только значение счетчиков 6 становится не равным нулю, сигналы разрешения с их выходов поступают, на вторые входы соответствующих элементов И 7 - подтверждается наличие в накопителе 1 информации для соот-.. ветствующих направлений. При поступ- лении запросов по входам 17 запросов соответствующие триггеры 8 переводятся в eдиIiичнoe состояние и сигналы высокого уровня с их выходов поступают на третьи входы соответствую щих элементов И 7.

При появлении сигнала на втором управляющем входе 16 устройства (он поступает на первые входы элементов И 7.1-7т) сигналы высокого уровня с выходов элементов И 7, соответствующих направлениям выдачи информации, от которых поступил запрос и дпя KOTOpbix в накопителе есть информация, поступают на соответствующие входы блока 5. задания приоритетов обращений. Блок 5 задания приоритетов выделяет из поступивших сигналов старший по приоритету (наиболее приоритетное направление) и форми- рует сигнал на соответствующем выходе .

Например, наиболее приоритетным является k-e направление. Сигнал с

8

одного из выходов блока 5 задания приоритетов обращений поступает на первые входы счетчиков 6k слов- и счетчиков 4k адреса считывания и вход дешифратора 9k. По данному сигналу осуществляется подключением счетчика 4k к адресным входам накопителя 1 и считывание первого слова информации k-ro направления. Считанное слово с выхода накопителя 1 поступает на первые входы регистров 2.1-2т, а код слова - на входы дешифраторов 9,1-9т. При наличии сигнала с соответствующего выхода блока 5 задания приоритетов обращений дешифратор 9k по коду формирует сигнал на втором выходе. Сигнал с второго выхода дешифратора 9k поступает на вторые входы регистра 2k и триггера 8k, Триггер 8k переводится в нулевое состояние. Разрешается прием слова в регистр 2k (вьщача информации по k-му направлению). По заднему фронту сигнала, поступившего на первые входы, счетчик 4k адреса считывания увеличивает, а счетчик 6k рггпта уменьшает свое содержимое наедрщицу. . Таким Ъбразом осуществляется однократный обмен с наиболее приоритетным направлением, формирование адреса очередного обращения к накопителю и снятие запроса. До поступления очередного запроса k-ro направления име ется возможность организовать одно- кратньш обмен со следующим по приоритету направлением. При поступлении очередного запроса k-ro направления с появлением очередного сигнала на втором 16 управляющем входе устройства начинается поиск очередного слова информации k-направления. Если информация записывается в виде группы слов, то происходит считывание очередного слова аналогично тому, как производится считывание первого.

Если же информация записывается в виде отдельных слов для различных направлений, то может оказаться, что очередное считанное слово не принадлежит k-му направлению. В этом случае в данном такте на втором выходе дешифратора 9k сигнал не формируется считанное, слово в регистр 2k не принимается и триггер 8k в нулевое состояние не переводится. Содержимое счетчика 4k адреса считывания увеличивается, а содержимое счетчика 6k слов уменьшается на единицу. В очередном такте запрос х-г6 направления остается наиболее приоритетным и поиск продолжается - считывается очередное слово информации. Считывание производится до тех пор, пока не будет считано слово для k-ro направления или же содержимое счетчика 6k слов.не станет равным нулю, что означает Отсутствие информации k-ro направления в накопителе 1. При нулевом состоянии счетчика 6 сигнал с его выхода закрывает элемент И 7k и блокирует возможность обслуживания запросов k-ro направления.

Предлагаемое устройство может осуществлять выдачу любых наборов информационных слов на каждое из направлений по мере поступления от них запросов за информацией. При этом для обслуживания одного из направлений нет необходимости в просмотре всего объема накопителя - поиск нужной информации осуществляется начина с адреса первого слова соответствующего направления.

Ф

изобретения

о р м у л а

Буферное запоминающее устройство, содержащее накопитель, информационные выходы которого подключены к информационным входам регистров, а адресные - к выходам счетчика адреса записи и счетчиков адреса считывания, счетчики слов, триггеры управления сигналом обращения,.элементы И и блок задания приоритетов обращения, адресный выход которого соединен с входом счетчика адреса записи, информационные выходы блока

задания приоритетов обращения соединены с информационными входами счетчиков адреса считывания и счетчиков слов, управляющий вход блока задания приоритетов обращений является первым управляющим входом устройства информационные входы блока задания приоритетов обращений подключены к выходам элементов И, первые входы

Составитель В.Фокина Редактор А.Козориз Техред И.Попович

4051/50 Тираж 589

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раущская наб,, д. 4/5

Коррект Подписн

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

10

30

40

45

361188

которых объединены и являются вторым управляющим входом устройства, вторые входы элементов И соединены с выходами соответствующих счетчиков слов, третьи входы - с выходами соответствующих триггеров управления сигналом обращения, установочные входы которых являются входами обраще-- ния устройства, информационными выходами которого являются выходы регистров, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены

15 дешифраторы триггеры управления формированием адреса считывания, дополнительные элементы И, блоки элементов И, элементы задержки, блоки , элементов НЕ, выходы которых соедине20 ны со счетными входами соответствующих счетчиков ,слов, а входы - со счетными входами соответствующих счетчиков адреса считывания и с выходами соответствующих блоков элементов И,

25 первые входы которых объединены и подключены к выходу счетчика адреса записи, а вторые входы - с выходами соответствующих дополнительных элементов И и входами соответствующих элементов задержки, выходы которых подключены к входам соответствующих триггеров управления формированием адреса считывания, выходы которых соединены с первыми входами соответствующих дополнительных элементов,И, вторые входы которых подключены к первым управляющим выходам соответствующих дешифраторов, вторые управляющие выходы которых соединены с входами сброса соответствующих триггеров и управляющими входами регистров, первые информационные входы дешифраторов подключены к информаци-

35

онным выходам нaкoпитeляJ вторые информационные входы - к первому управляющему входу устройства, а третьи информадионные входы - к информацион- ным выходам блока задания приоритетов обращений.

Корректор С.Черни Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Многоканальное оперативное запоминающее устройство | 1987 |

|

SU1432606A1 |

| Устройство для управления обменом информации | 1982 |

|

SU1081638A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| Буферное запоминающее устройство | 1984 |

|

SU1163360A1 |

| Имитатор абонентов | 1983 |

|

SU1291987A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1075310A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1316050A1 |

| Устройство для сопряжения ЭВМ в вычислительную систему | 1986 |

|

SU1357971A1 |

Изобретение относится к вычислительной технике, а именно к запо- М1шающим устройствам, и может быть использовано в системах сбора, пере дачи и обработки информации. Целью изобретения является повышение быстсл с со со ot 00

| Буферное запоминающее устройство | 1980 |

|

SU888202A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-03—Подача