Изобретение относится к вычислительной технике и может использоваться в аппаратуре, работающей с информацией, которая представлена в системе остаточных классов (СОК).

Цель изобретения - повышение быстродействия и упрощение устройства.

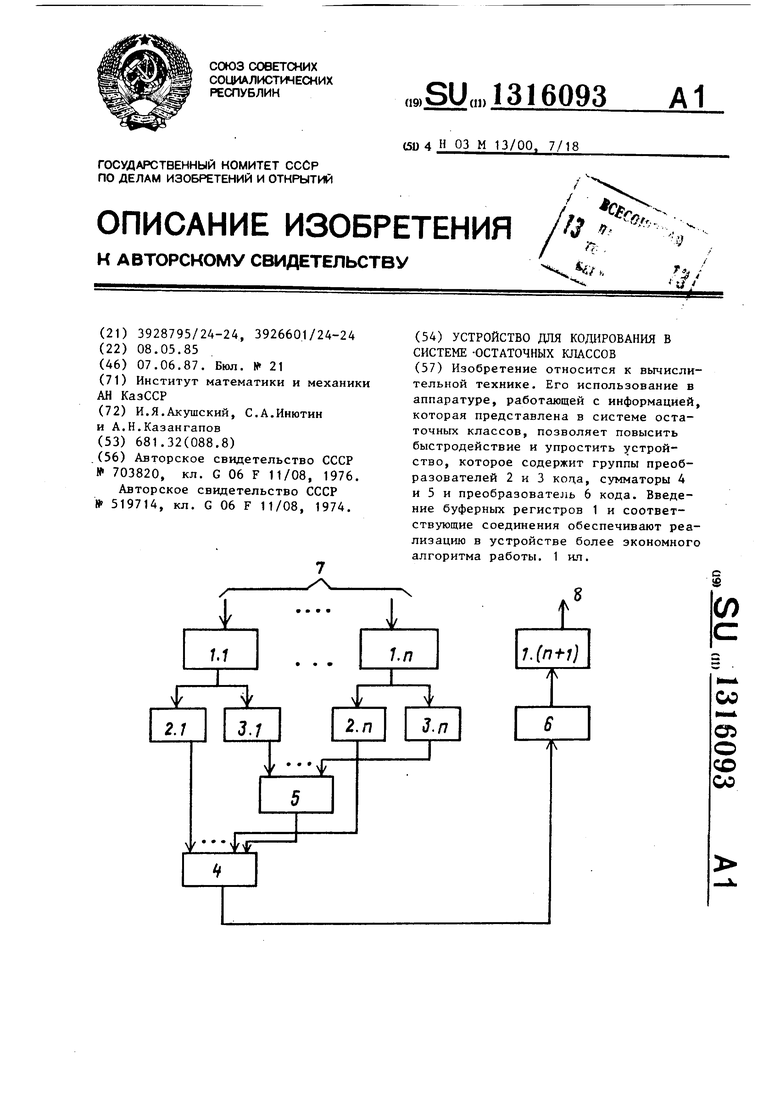

На чертеже представлена функциональная схема устройства.

Устройство для кодирования в СОК содержит п+1 буферных регистров 1 (п - число оснований в СОК), первую группу преобразователей 2 кода, вторую группу преобразователей 3 кода, первый 4 и второй 5 сумматоры и преобразователь 6 кода. На чертеже обозначены входы 7 и выходы 8 устройства.

В основу работы устройства кодирования положен следующий алгоритм.

Пусть первоначально число

П-1

,D п р.) задано в коде сок (n,2D)

i-1

где п - число рабочих оснований СОК; Р„ 2, 2D - рабочий диапазон СОК. Необходимо получить число в избыточном коде СОК (п+1, f 2DPf,,), где Sp - полный диапазон СОК , Р - контрольное основание СОК, т.е. получить вычет от числа А по основанию Р. Такой избыточный код обнаруживает одну модульную ошибку, т.е. любую ошибку в вычете по одному любому основанию СОК.

Для получения вычета по контрольному основанию надо получить промежуточное число А А + D E(D,2D), что достигается добавлением 1 в двоичный вычет по основанию Рр, который может быть равен О или 1 и занимает один бит. Необходимо также получить число А А + 2ND, имеющее представление в СОК (oti, ..., 0), где значения вычетов о,, i е d ,п совпадают со значениями для числаА , Здесь N - некоторое целое число

р

f-i |,

Затем определяется от числа А

функция

f(A)

t- 1 I

т -Рг

где константу Т можно выбрать равной q-Pp, , что приводит к выражению

f(A)

Т,г

,-, 1 1 1 т

или, при использовании модульной арифметики с учетом, что HOД(T,q) q,

.-4,r.(A)||

Pn+JPn-n

Здесь используются следующие обозначения:

/ i2iTll . „. /2DPi,., L Pt J|T P, xiy - знак вычета числа x по модулю Т.

При Т, q-P, 2(п-2)Р„ справедливо

-ЦБ

f(A) .

для всех А, для которых . Это справедливо для всех чисел А, полученных указанным образом, в частности и для числа, у которого о 0.

Для числа А А - D справедливо также соотношение

о(.., P...-«Q q|; /2DUp.

..Jp.., .

что определяет функцию преобразователя 6, т.е. по величине Q с использованием преобразователя 6 за один модульный такт получается величина , являющаяся вычетом по контрольному основанию. Аналогично можно получить величины по другим контрольны основаниям.п

35

Величины 2«,. lev. У, IP,,, , {L

Л+1

oifi не превьшают величину Р , отсюда следуют ограничения на разрядности преобразователей и сумматоров. Устройство работает следующим образом.

Вычеты числа А в коде СОК поступают в соответствующие буферные регист- ры 1. Затем происходят преобразования вычетов с помощью преобразователей 2

и 3 в величины у-1р , ,- Причем J h-ft i м т

вычет d (равный нулю или единице) посредством преобразователей 2.п, З.п преобразуется в величины ((j- |р , зо1 ветствующие инверсному значению , т.е. о/п

.. О, Уп1я (

ОХу,|р,, О, yj 0.

Преобразование выполняется за один модульный такт. Затем выполняется параллельное суммирование п величин

(jt l V сумматоре 5 по модулю q, также n-1 величины (. Х) (.рр, (так

0)

И величины

для всех А, для которых (.А 2о г Это справедливо для всех А , пол ченных указанным образом, в част для числа, у которого d 0. но показать, что для числа А А справедливо

с обратным знаком взятой с выходов сумматора 5, на сумматоре 4. На зто требуется jlog модульных тактов. Затем полученная величина Q поступает на входы преобразователя 6, с выходов которого через один модульный. / I

такт величина ,, поступает в бу- h+i n+i (Pn4-i|pn+i ферный регистр 1.(п+1). В результате получается избыточный помехозащитный код СОК за +3 модульных так- та.

В случае некоторого видоизменения алгоритма устройство может быть упрощено за счет исключения второй группы преобразователей 3 кода и второго сумматора 5, но требует несколько большей разрядности контрольного основания СОК. Для этого случая алгоритм работы устройства приобретает следующий вид.

Пусть первоначальное число

П-1

AeLO,D П р.) задано в коде СОК

ill

(п, 2D), где п - число рабочих осно- ЗО ваний СОК; РП 2, 2D - рабочий диапазон СОК. Необходимо получить число в избыточном коде СОК (п+1, J 2D „+,), где Р - полный диапазон СОК; Р , - контрольное основание С(К, т.е. полу- г

+ (Щр (р

I м (

По величине fCA) с использов нием преобразователя 6 за один мо дульный такт получается величина , являющаяся вычетом по контр ному основанию. Аналоптчио можно лучить величины по другим контрол ным основаниям.

Величины

25

/ 1

1.- l4

менее

о( менее Р„, , отсюда следуют раничения на разрядность преобраз вателей и сумматора, в частности построения кода с одним контрольн основанием в СОК с небольшим числ оснований и при большой их величи аппаратура должна иметь разряднос порядка величины этого основания

Если выбрать (п-2), равную сте

значение

чить вычет от числа А по основанию Р, . Для получения вычета по контрольному основанию надо получить промежуточное число А А + ,2D). Это достигается добавлением 1 в 40 двоичный вычет по основанию Р, который может быть равен О или 1 и занимает один бит. Кроме того, надо получить число А А + N2D, имеющее представление в СОК W,,. .. , , 0), 45 где значения вычетов ci, i е 1 , падают со значениями для числа А , здесь N - некоторое целое число Рп4- двух и т 2(п-2) Р f(A ) выбирается просто из соотве ствующих разрядов сумматора 4, гд

вычисляется величина

И

г,Устройство при этом работает с дующим образом.

Число А в коде СОК поступает в соответствующие буферные регистры

Вычет df, (равный О или 1) средством преобразователя 2.п пре разуется в величину -j- , соответс ющую инверсному значению d , т.е

Л-Т-1

Затем определяется от числа А функция

f(A) .

S M.

где Т 2 (п-1) - константа -/f iEilll . „, -/

- Р, Л,.-

х| - знак вычета числа х дулю Т.

При Т , 2(п-2) .(A-)

справедливо

для всех А, для которых (.А 2о г D. Это справедливо для всех А , полученных указанным образом, в частности для числа, у которого d 0. Можно показать, что для числа А А - D справедливо

. / I

h+i n+i (Pn4-i|pn+i

+ (Щр (р

I м (

По величине fCA) с использованием преобразователя 6 за один модульный такт получается величина , являющаяся вычетом по контрольному основанию. Аналоптчио можно получить величины по другим контрольным основаниям.

Величины

/ 1

1.- l4

менее Т,

о( менее Р„, , отсюда следуют ограничения на разрядность преобразователей и сумматора, в частности для построения кода с одним контрольным основанием в СОК с небольшим числом оснований и при большой их величине аппаратура должна иметь разрядность порядка величины этого основания.

Если выбрать (п-2), равную степени

значение

двух и т 2(п-2) Р f(A ) выбирается просто из соответствующих разрядов сумматора 4, где

вычисляется величина

И

г,Устройство при этом работает следующим образом.

Число А в коде СОК поступает в соответствующие буферные регистры 1.

Вычет df, (равный О или 1) посредством преобразователя 2.п преобразуется в величину -j- , соответствующую инверсному значению d , т.е.

in О -О

Тг

Л-Т-1

2 J

или

ОСп 1 - 1 О - у„ 0. Вычеты d-(i l,n-l) посредством преобразователей 2.-2,(п- ) перекодируются в

величины j за один модульный такт. Затем величины суммируются на сумматоре 4 по модулю Т за J logjO модульных тактов. Затем полученная величина f(A) поступает на входы преобразователя 6, с выходов которого через один

модульный такт величина oi, поступает в буферный регистр 1.(). В итоге получен избыточный код СОК за JlogjH С-«-Z модульных такта.

Таким образом, предлагаемое устройство позволяет получить помехозащитный код в СОК за меньшее время, чем известное, и имеет более простое выполнение.

Формула изобретения

Устройство для кодирования в системе остаточных классов, содержащее преобразователь кода, первую и вторую группы преобразователей кода, выходы первого - п-го преобразователей кода первой и второй группы (п - число оснований в системе остаточных классов) соединены с одноименными входами соответственно первого и второго сумматоров, отличающееся тем,

что, с целью повьппения быстродействия и упрощения устройства, в него введены буферных регистров, выходы первого - п-го буферных регистров подключены к входам одноименных преобразователей кода обеих групп, выходы второго сумматора соединены с (п+1)-ми входами первого сумматора, выходы которого через преобразователь кода подключены к входам (п+О-го буферного регистра, входы первого - п-го буферных регистров являются соответствующими входами устройства, выходы ()-го буферного регистра являются выходами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обнаружения ошибок в системе остаточных классов | 1980 |

|

SU878061A1 |

| Устройство для исправления ошибок в системе остаточных классов | 1980 |

|

SU932499A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММ ПАРНЫХ ПРОИЗВЕДЕНИЙ | 1992 |

|

RU2012041C1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Арифметическое устройство для процессора быстрого преобразования Фурье | 1981 |

|

SU1042028A1 |

| Устройство для вычисления сумм парных произведений в полиномиальной системе классов вычетов | 2016 |

|

RU2622881C1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1986 |

|

SU1410281A1 |

| Устройство для умножения чисел в модулярной системе счисления | 1986 |

|

SU1368878A1 |

| Устройство для умножения чисел в модулярной системе счисления с плавающей запятой | 1986 |

|

SU1411741A1 |

| Устройство для вычисления дискретного преобразования Фурье в модулярной системе счисления | 1988 |

|

SU1633423A1 |

Изобретение относится к вычислительной технике. Его использование в аппаратуре, работающей с информацией, которая представлена в системе остаточных классов, позволяет повысить быстродействие и упростить устройство, которое содержит группы преобразователей 2 и 3 кода, сумматоры 4 и 5 и преобразователь 6 кода. Введение буферных регистров 1 и соответствующие соединения обеспечивают реализацию в устройстве более экономного алгоритма работы. 1 ил. со CD о со со

Авторы

Даты

1987-06-07—Публикация

1985-05-08—Подача