1 131741 Изобретение относится к электротехнике и может быть использовано в качестве источников электропитания электротехнической и радиоэлектронной аппаратуры различного назначения. j

Цель изобретения - упрощение и по- вьппение технико-экономических показателей за счет увеличения КПД и наделено с ти.

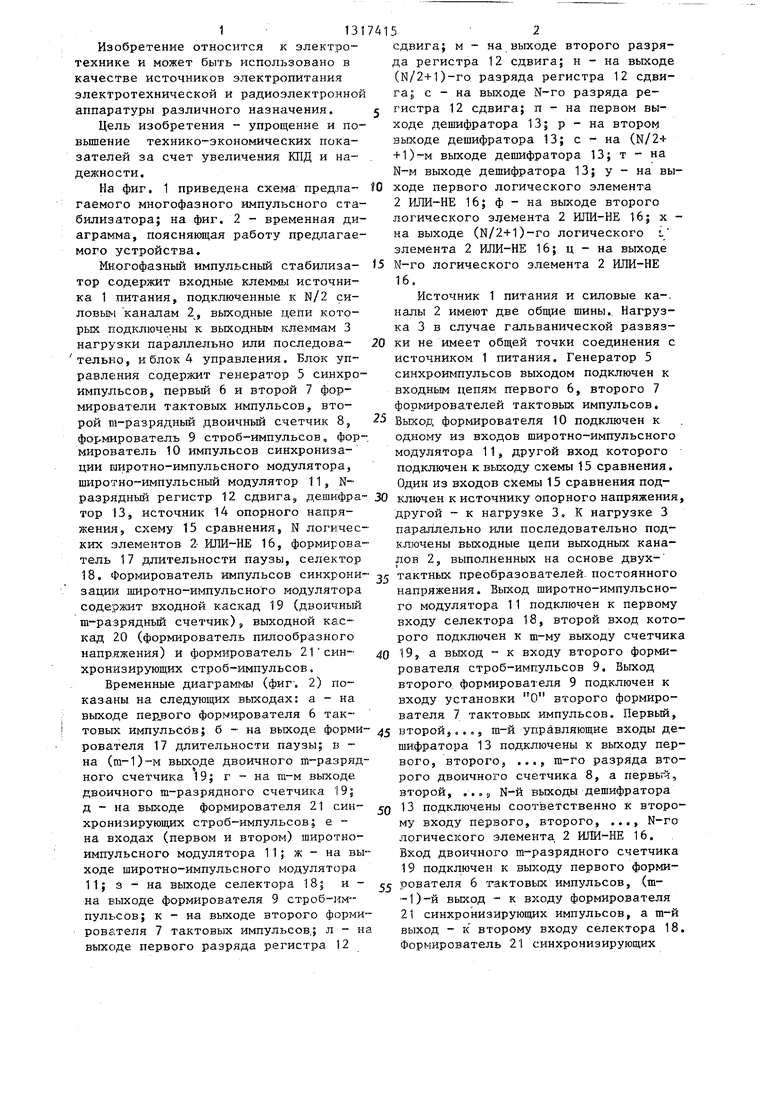

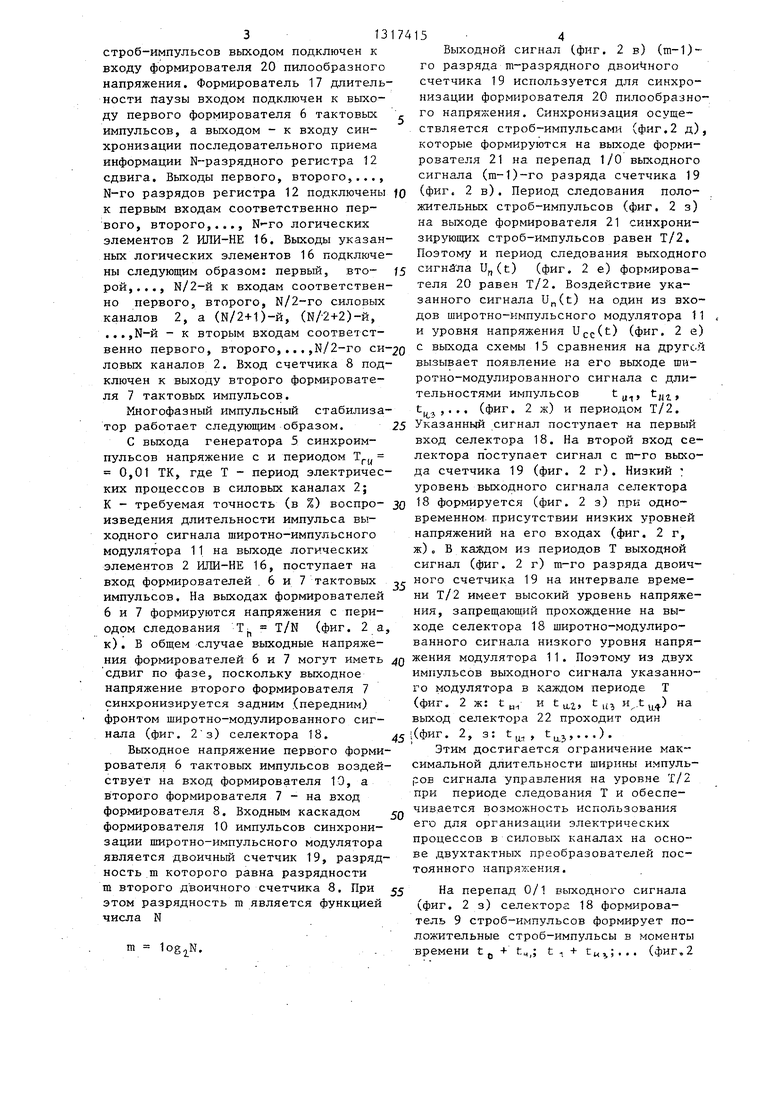

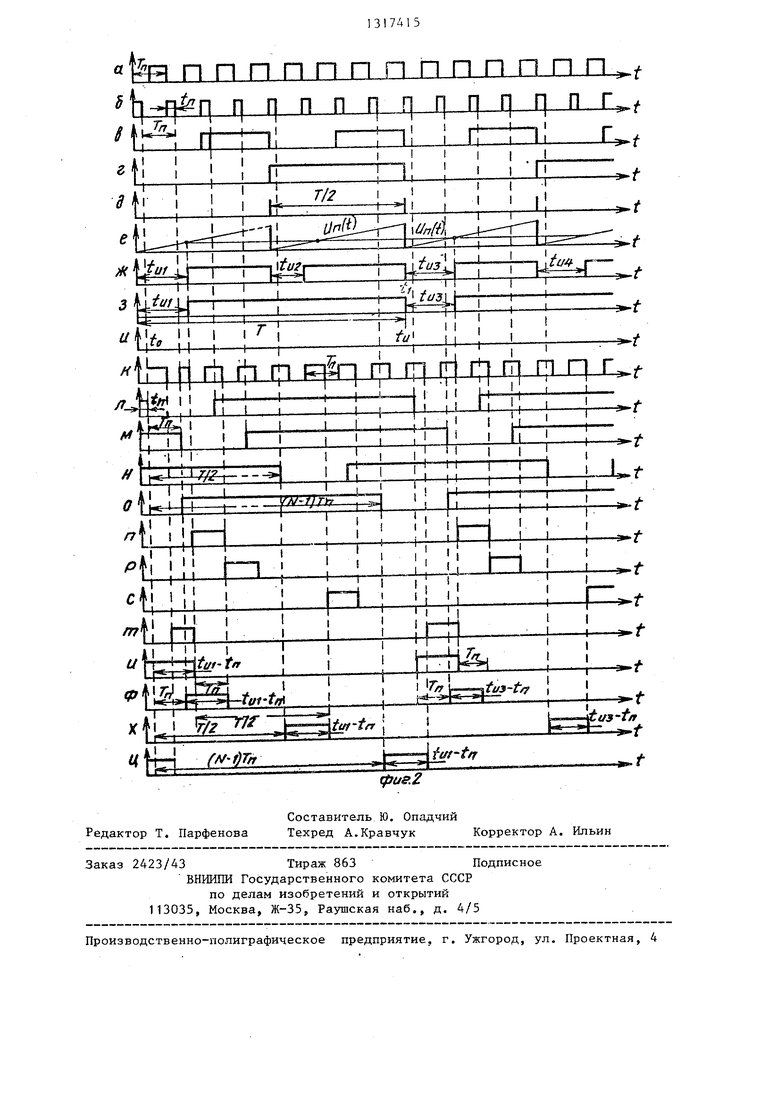

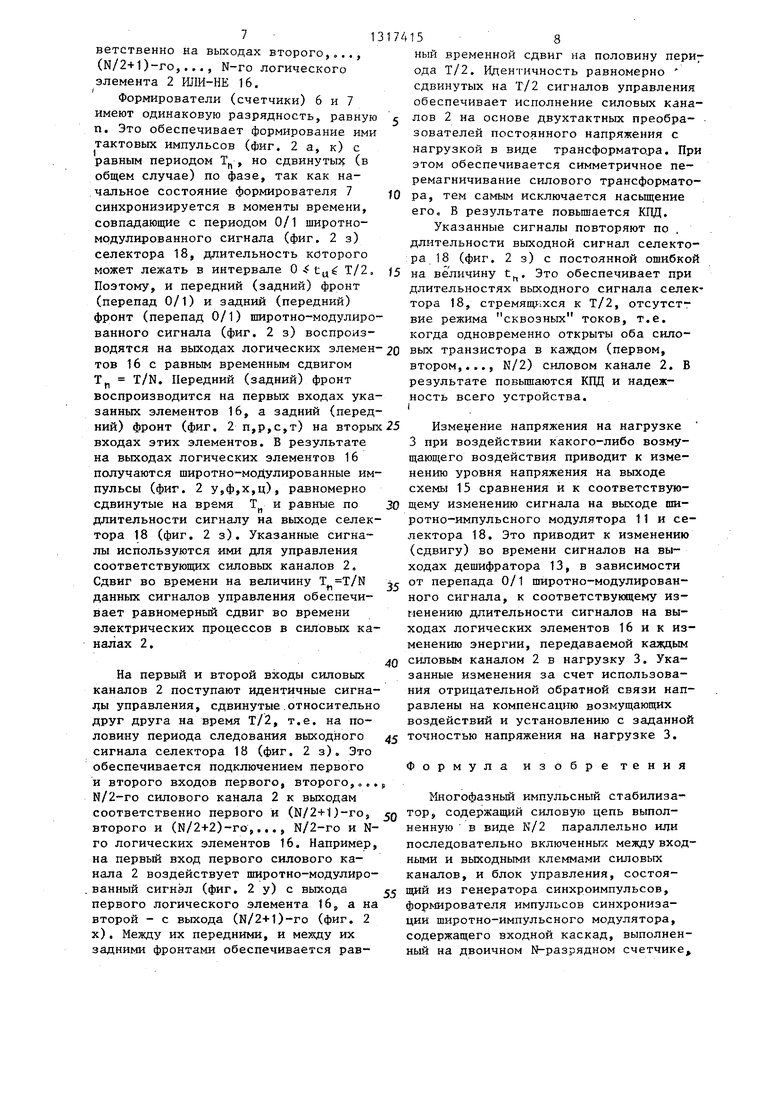

На фиг, 1 приведена схема предла- 0 гаемого многофазного импульсного стабилизатора; на фиг, 2 - временная диаграмма, поясняющая работу предлагаемого устройства.

Мн:огофазный импульсный стабилиза- 15 тор содержит входные клемм л источника 1 питания, подключенные к N/2 силовым каналам 2, выходные цепи которых подключены к выходным клеммам 3 нагрузки параллельно или последова- 20 тельно, и блок 4 управления. Блок управления содержит генератор 5 синхро™ импух ьсов, первый 6 и второй 7 формирователи тактовых импульсов, второй га-разрядный двоичный счетчик 8, 25 формирователь 9 строб-импульсов, формирователь 10 импульсов синхронизации широтно-импульсного модулятора, широтно-импульсный модулятор 11, N- разрядный регистр 12 сдвигаj дешифра- 30 тор 13, источник 14 опорного напряжения, схему 15 сравнения, N логических элементов 2- ИЛИ-НЕ 16, формирователь 17 длительности паузы, селектор 18, Формирователь импульсов синхрони- -зг зации широтно-импульсного модулятора содержит входной каскад 19 (двоичный ш-разрядный счетчик),, выходной каскад 20 (формирователь пилообразного напряжения) и формирователь 21 син- 40 хронизирующих строб-импульсов.

Временные диаграммы (фиг , 2) показаны на следующих выходах: а - на выходе nepj3oro формирователя 6 так- товык импульсов; б - на выходе форми- 5 рователя 17 длительности паузы; в - на (т-1)-м выходе двоичного ш-разряд- ного счетчика 19; г-на т-м выходе двоичного т-разрядного счетчика 19; д - на выходе формирователя 21 сии- Q хронизирующих строб-импульсов; е - на входах (первом и втором) широтно- импульсного модулятора 11; ж - на выходе широтно-импульсного модулятора 11; 3 - на выходе селектора 18; и - на выходе формирователя 9 строб-импульсов; к - на выходе второго формирователя 7 тактовых импульсов,; л - на выходе первого разряда регистра 12

5 2 сдвига; м - на выходе второго разряда регистра 12 сдвига; н - на выходе (N/2+1)-го разряда регистра 12 сдвига; с - на выходе N-ro разряда регистра 12 сдвига; и - на первом выходе дешифратора 13; р - на втором Бькоде дешифратора 13; с - на ( +1)-м выходе дешифратора 13; т - на N-M выходе дешифратора 13; у - на выходе первого логического элемента 2 ИЛИ-НЕ 16; ф - на выходе второго логического элемента 2 ИЛИ-НЕ 16; х на выходе (N/2+1)-ro логического {. элемента 2 ИЛИ-НЕ 16; ц - на выходе N-ro логического элемента 2 ИЛИ-НЕ 16.

Источник 1 питания и силовые ка-, налы 2 имеют две общие шины. Нагрузка 3 в случае гальванической развязки не имеет общей точки соединения с источником 1 питания. Генератор 5 синхроимпульсов выходом подключен к входным цепям первого 6, второго 7 формирователей тактовых импульсов, Выход формирователя 10 подключен к одному из входов широтно-импульсного модулятора 11, другой вход которого подключен к выходу схемы 15 сравнения, Один из входов схемы 15 сравнения подключен к источнику опорного напряжения другой - к нагрузке 3, К нагрузке 3 параллельно или последовательно подключены выходные цепи выходных каналов 2, выполненных на основе двух- тактных преобразователей, постоянного напряжения. Выход широтно-импульсного модулятора 11 подключен к первому входу селектора 18, второй вход которого подключен к т-му выходу счетчик 19, а выход - к входу второго формирователя строб-импульсов 9, Выход второго формирователя 9 подключен к входу установки О второго формирователя 7 тактовых импульсов. Первый, второй,,,,, ш-й управляющие входы дешифратора 13 подключены к выходу первого, второго, ,,,, т-го разряда второго двоичного счетчика 8, а первьй, второй, .,,р N-й выходы дешифратора 13 подключены соответственно к второму входу первого, второго, ,,,, N-ro логического элемента, 2 ИЛИ-НЕ 16, Вход двоичного т-разрядного счетчика 19 подключен к выходу первого формирователя 6 тактовых импульсов, (т- -1)-й выход - к входу формирователя 21 синхронизирующих импульсов, а т-й выход - к второму входу селектора 18 Формирователь 21 синхронизирующих

строб-импульсов выходом подключен к входу формирователя 20 пилообразного напряжения. Формирователь 17 длительности паузы входом подключен к выходу первого формирователя 6 тактовых импульсов, а выходом - к входу синхронизации последовательного приема информации N-разрядного регистра 12 сдвига. Выходы первого, второго,..., N-ro разрядов регистра 12 подключены к первым входам соответственно первого, второго,..., NTO логических элементов 2 ИЛИ-НЕ 16. Выходы указанных логических элементов 16 подключены следующим образом: первый, вто- рой,..., N/2-й к входам соответственно первого, второго, N/2-го силовых каналов 2, а (Н/2+1)-й, (N/2+2)-й, ...,Ы-й - к вторым входам соответственно первого, второго,...,N/2-ro си ловых каналов 2. Вход счетчика 8 подключен к выходу второго формирователя 7 тактовых импульсов.

Многофазный импульсный стабилизатор работает следующим образом.

С выхода генератора 5 синхроимпульсов напряжение с и периодом 0,01 ТК, где Т - период электрических процессов в силовых каналах 2; К - требуемая точность (в %) воспро- изведения длительности импульса выходного сигнала широтно-импульсного модулятора 11 на выходе логических элементов 2 ИЛИ-НЕ 16, поступает на вход формирователей . 6 и 7 тактовых импульсов. На выходах формирователей 6 и 7 формируются напряжения с периодом следования Tj, T/N (фиг. 2 а к). В общем случае выходные напряжения формирователей 6 и 7 могут иметь сдвиг по фазе, поскольку выходное напряжение второго формирователя 7 синхронизируется задним .(передним) фронтом широтно-модулированного сигнала (фиг. 2 з) селектора 18.

Выходное напряжение первого формирователя 6 тактовых импульсов воздействует на вход формирователя 10, а второго формирователя 7 - на вход формирователя 8. Входным каскадом формирователя 10 импульсов синхронизации щиротно-импульсного модулятора является двоичный счетчик 19, разрядность m которого равна разрядности m второго двоичного счетчика 8. При этом разрядность m является функцией числа N

m .

Выходной сигнал (фиг. 2 в) (т-1)- го разряда т-разрядного двои 1ного счетчика 19 используется для синхронизации формирователя 20 пилообразного напряжения. Синхронизация осуществляется строб-импульсами (фиг.2 д) которые формируются на выходе формирователя 21 на перепад 1/0 выходного сигнала (т-1)-го разряда счетчика 19 (фиг. 2 в). Период следования положительных строб-импульсов (фиг. 2 з) на выходе формирователя 21 синхронизирующих строб-импульсов равен Т/2. Поэтому и период следования выходног сигнй ла U(t) (фиг. 2 е) формирователя 20 равен Т/2. Воздействие указанного сигнала U(t) на один из входов широтно-импульсного модулятора 1 и уровня напряжения U(;c(t) (фиг. 2 е с выхода схемы 15 сравнения на другой вызывает появление на его выходе широтно-модулированного сигнала с длительностями импульсов ui Н1 t| ,. .. (фиг. 2 ж) и периодом Т/2. Указанный сигнал поступает на первый вход селектора 18. На второй вход селектора пЪступает сигнал с т-го выхода счетчика 19 (фиг. 2 г). Низкий : уровень выходного сигнала селектора 18 формируется (фиг. 2 з) при одновременном присутствии низких уровней напряжений на его входах (фиг. 2 г, ж)о В каждом из периодов Т выходной сигнал (фиг. 2 г) т-го разряда двоичного счетчика 19 на интервале времени Т/2 имеет высокий уровень напряжения, запрещающий прохождение на выходе селектора 18 широтно-модулированного сигнала низкого уровня напряжения модулятора 11. Поэтому из двух импульсов выходного сигнала указанного модулятора в каждом периоде Т (фиг. 2 ж: t yv и ц, t ц, ) на выход селектора 22 проходр т один ;(фиг. 2, з: t , t,,,,).

Этим достигается ограничение максимальной длительности ширины импуль- ров сигнала управления на уровне Т/2 при периоде следования Т и обеспечивается возможность использования его для организации электрических процессов в силовых каналах на основе двухтактных преобразователей постоянного напряжения.

На перепад 0/1 выходного сигнала (фиг. 2 з) селектора 18 формирователь 9 строб-импульсов формирует положительные строб-импульсы в моменты времени t j, + Г-ч,; t-,, + t,;... (фиг. 2

513

и). Короткие положительные импульсы (строб-импульсы) формирователя 9 обеспечивают установку в О второго формирователя (счетчика) 7 по выхоДУ R,

Таким образом, в каждом периоде Т производится установка в О вто- рого формирователя 7 тактовых импульсов (фиг, 2 к) в моменты времени t ч , t + tj,;... (фиг, 2 и), совпа- с перепадом 0/1 вьосодного сигнала селектора 18 (фиг. 2 з), В интервалах времени между воздействиями строб-импульсов формирователь 7 обеспечивает тактовые импульсы с перио- дом следования Тц (фиг 2 к) на входе двоичного т-разрядного счетчика 8,

Поскольку выходы первого, второго,,,,, т-го разрядов двоичного счетчика 8 подключены к управляю дим входам дешифратора 13,,то на первом, втором,..,, (N/2+1)j,,.j выходах дешифратора 13 появляются положительные импульсы (фиг. 2 п, р,, с, т), длительностью 1 T/N и периодом еледования, равным Т. Например, временная диаграмма, изображенная на фиг.2 п соответствует состоянию счетчика 8 00,0,00, эпюра п ка фиг, 2 соответствует состоянию 00,,о01, а фиг, 2 т соответствует состоянию 11,.. 111 счетчика 8.

Выходной сигнал первого формирователя 6 тактовых импульсов (фиг. 2 а) используется для синхронизации формирователя 10 и для синхронизации формирователя 17 длительности паузы. На выходе формирователя 17 формируется импульсный сигнал (фиг. 2 б) дли- тельностью t на перепад 1/0 выходного сигнала (фиг, 2 а) формирователя бе Длительность t указанных положительных импульсов выбирается, из условия превышения длительности време- ни рассасывания неосновньк носителей 3 области базц силовых коммутирующих транзисторов силовых каналов 2. Выходной сигнал (фиго 2 б) формирователя 17 используется для синхрониза- ции регистра 12 сдвига. Выходной сигнал (фиг. 2 з) селектора 18 возд€;йст- вует на информационный вход после- довательного ввода информации регист- ра 12. Запись его в первый разряд и сдвиг в последующие старшие разряды указанного регистра осуществляется фронтом 1/0 выходного сигнала (фиг,2 б) формирователя 17, В результате на

15 6

выходах первого, второго,...,(N/2+ +1)-го,..,,N-ro разрядов регистра 12 появляются сигналы (фиг. 2 л,м,н,о), равномерно сдвинутые на время Т T/N равное периоду следователя выходного сигнала (фиг.2 б) формирователя 17, Так как перепад 1/0 выходного синхронизирующего сигнала (фиг. 26) формирователя 17 смещен относительно переднего фронта выходного сигнала селектора 18 (фиг о 2 з), то передний фронт выходного сигнала (фиг. 2 л) первого разряда регистра 12 смещен на величину -t, второго разряда - на величину t|,,,,, и т.д.

Поскольку запись в первый разряд регистра 12 выходного сигнала селектора 18 и его сдвиг в старшие разря- ды (со второго по N-й) осуществляется дискретно через интервал времени Т T/N, то в общем случае на выходах первого, второго,,..,(N/2+1)-ro,..., разрядов регистра 12 сигналы (фиг, 2 л,М5Н,о) отличаются от поступающего сигнала (фиг, 2 з) на информационный вход. Максимальная ошибка воспроизведения указанного сигнала достигает величины периода Т|,, T/N следования синхронизирущих им- пульсов формирователя 17.

Однако воздействие выходных сигналов регистра 12 и дешифратора 13 на входы логических элементов 2 ИЛИ-НЕ 16 позволяет получить на их выходах идентичные равномерно сдвинутые сигналы, отличающиеся от выходного сигнала (фиг. 2 з) селектора 18 на величину гарантированной длительности паузы t, Воздействие на первый вход логического элемента 2 ИЛИ-НЕ 16 сигнала (фиг. 2 л) с выхода первого разряда регистра 12 и на второй - в с первого выхода дешифратора 13 (фиг, 2 .п) обеспечивает на выходе указанного логического элемента 16 положительный импульс длительностью t - t у, (фиг« 2 у) и периодом следования Т, совпадаюш 1м по времени с выходным сигналом селектора 18, Результатом воздействия на первые входы второго,о,,9(N/2+1),...jN-ro логического элемента 2 ИЛИ-.НЕ 16 сигналов (фиг, 2 м,Нро) с выходов соответственно второго,,,,, (N/2+1)-ro,..., N-ro разрядов регистра 12 и на вторые входы соответственно с второго,,.., (N/2+1)-ro,.,,,, N-ro выходов дешифратора 13 (фиг. 2 р,с,т) являются выходные сигналы (фиг. 2 ф,х,ц) соответственно на выходах второго,,.., (N/2+1)-ro,..., N-ro логического элемента 2 ШШ-НЕ 16.

Формирователи (счетчики) 6 и 7 имеют одинаковую разрядность, равную п. Это обеспечивает формирование ими тактовых импульсов (фиг. 2 а, к)

с

равным периодом Т, но сдвинутых (в общем случае) по фазе, так как начальное состояние формирователя 7 синхронизируется в моменты времени, совпадающие с периодом О/1 широтно- мрдулированного сигнала (фиг. 2 з) селектора 18, длительность которого может лежать в интервале Т/2, Поэтому, и передний (задний) фронт (перепад 0/1) и задний (передний) фронт (перепад 0/1) широтно-модулиро- ванного сигнала (фиг. 2 з) воспроизводятся на выходах логических элемен- 20 вых транзистора в каждом (первом, тов 16 с равным временным сдвигом

втором N/2) силовом канале 2.

Тр T/N. Передний (задний) фронт воспроизводится на первых входах указанных элементов 16, а задний (передний) фронт (фиг. 2 п,р,с,т) на вторых входах этих элементов. В результате на выходах логических элементов 16 получаются широтно-модулированные импульсы (фиг. 2 у,ф,х,ц), равномерно сдвинутые на время Т и равные по длительности сигналу на выходе селектора 18 (фиг. 2 з). Указанные сигналы используются ими для управления соответствующих силовых каналов 2,

Сдвиг во времени на величину данных сигналов управления обеспечивает равномерный сдвиг во времени электрических процессов в силовых каналах 2.

На первый и второй входы силовых

каналов 2 поступают идентичные сигна- Jlы управления, сдвинутые.относительно друг друга на время Т/2, т.е. на половину периода следования выходного сигнала селектора 18 (фиг. 2 з). Это обеспечивается подключением первого и второго входов первого, второго,„.. N/2-го силового канала 2 к выходам соответственно первого и (N/2+1)-го, второго и (N/2+2)-ro,.,., N/2-го и N- го логических элементов 16. Например, на первый вход первого силового канала 2 воздействует широтно-модулиро- ванный сигнал (фиг. 2 у) с выхода первого логического элемента 16, а на второй - с выхода (N/2+1)-го (фиг. 2 х). Между их передними, и между юс задними фронтами обеспечивается рав174158

ный временной сдвиг на половину пери;- ода Т/2. Идентичность равномерно сдвинутых на Т/2 сигналов управления обеспечивает исполнение силовых каналов 2 на основе двухтактных преобра- зователей постоянного напряжения с нагрузкой в виде трансформатора. При этом обеспечивается симметричное пе- ремагничивание силового трансформато-

fO pa, тем самым исключается насыщение его, В результате повышается КПД. Указанные сигналы повторяют по длительности выходной сигнал селектора 18 (фиг. 2 з) с постоянной ошибкой на величину t. Это обеспечивает при длительностях выходного сигнала селектора 18, стремящихся к Т/2, отсутст15

вие режима сквозных токов, т.е. когда одновременно открыты оба сило0 вых транзистора в каждом (первом,

5 0

5

0

5 0

втором N/2) силовом канале 2. В

результате повьшаются КПД и надежность всего устройства.

I

напряжения на нагрузке 3 при воздействии какого-либо возмущающего воздействия приводит к изменению уровня напряжения на выходе схемы 15 сравнения и к соответствующему изменению сигнала на выходе ши- ротно-импульсного модулятора 11 и селектора 18. Это приводит к изменению (сдвигу) во времени сигналов на выходах дешифратора 13, в зависимости от перепада О/1 широтно-модулированного сигнала, к соответствукхдему изменению длительности сигналов на выходах логических элементов 16 и к изменению энергии, передаваемой калздым силовым каналом 2 в нагрузку 3. Указанные изменения за счет использования отрицательной обратной связи направлены на компенсацию возмущающих воздействий и установлению с заданной точностью напряжения на нагрузке 3.

Формула изобре тения

Многофазный импульсный стабилизатор, содержащий силовую цепь выполненную в виде N/2 параллельно или последовательно включенных между входными и выходными клеммами СИЛОВЬЕХ каналов, и блок управления, состоящий из генератора синхроимпульсов, формирователя импульсов синхронизации широтно-импульсного модулятора, содержащего входной каскад, выполненный на двоичном N-разрядном счетчике.

913

формирователь синхронизирующих строб- импульсов и выходной каскад формирователя пилообразного напряжения, К- разрядного регистра сдвига, N логических элементов 2 ИЛИ-НЕ, двух фор- мирователей тактовых импульсов, формирователя строб-импульсов, источника опорного напряжения, селектора, широтно-импульсного модулятора, дешифратора, узла сравнения, при этом указанный узел сравнения одним из входов подключен к источнику опорно- то напряжения, другим - к выходным выводам, а выходом к одному из входов широтно-импульсного модулятора, другой вход которого подключен к выходу формирователя импульсов синхронизации широтно-импульсного модулятора J выход генератора синхроимпульсов подключен к входам первого и второ- го формирователей тактовых импульсов первый, второй,...,Н-й выходы дешифратора подключены к вторым входам соответственно первого, второго,..., N-ro логического элемента 2 ИЛИ-НЕ, у двоичного т-разряДного счетчика вход подключен к выходу первого фор- |«1ро6ателя тактовых импульсов, (т- -1)-й выход - к входу формирователя

синхронизирующих строб-импульсов,а

ш-й выход - к выходу широтно-импульсного модулятора, а выход - к входу формирователя строб-импульсов, выход которого подключен к входу установки

в О второго формирователя тактовых импульсов, формирователь синхронизи

5 0 5

Q

5

510

рующих строб-импульсов выходом подключен к входу формирователя пилообразного напряжения, отличающийся тем, что, с целью упрощения и повьш1ения технико-экономических показателей за счет увеличения КДЦ и надежности, введены второй т-разряд- . ный двоичный счетчик и формирователь длительности паузы, при этом вход упомянутого формирователя подключен к выходу первого формирователя тактовых Импульсов, а выход - к входу синхронизации последовательного приема информации N-разрядного регистра сдвига, у которого выход первого, второго,,,.,N-ro разряда подключен к первому входу соответственно, первого, второго,..., N-ro логического элемента 2ИЛИ-НЕ, а информационный вход последовательного приема информации - к -выходу селектора, выход первого, второго,...iN/2-го логического элемента 2 ШШ-НЕ подключен к первому входу соответственно первого, второго,...,N/2-ro силового канала,а вькод (N/2+1)-ro, (N/2+2)-ro, ,.., N-ro логического элемента 2 ИЛИ- НЕ - к второму входу соответственно первого, второго,...,N/2-ro силового канала первый, второй,..., ю-й управляющий вход дешифратора подключен к выходу первого, второго,..., т-го разряда второго т-разрядного двоичного счетчика, вход которого подключен к выходу второго формирователя тактовых импульсов.

fe.

ппппппппппппп,

Ц

I I

tpuff.Z

Составитель Ю. Опадчий

Техред А.Кравчук Корректор А. Ильин

Редактор Т. Парфенова

Заказ 2423/43Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

W-U

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Многофазный импульсный стабилизатор напряжения | 1990 |

|

SU1700545A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Блок управления многофазным импульсным стабилизатором | 1983 |

|

SU1123085A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Многофазный импульсный стабилизатор напряжения | 1983 |

|

SU1156032A1 |

| Многозонный стабилизатор постоянного напряжения | 1990 |

|

SU1700544A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1070528A1 |

| Многофазный импульсный стабилизатор напряжения | 1987 |

|

SU1483438A1 |

Изобретение относится к источникам вторичного электропитания радиоэлектронной аппаратуры. Целью изобретения является упрощение при одновременном увеличении КПД и надежности. Цель достигается тем, что введенный 3 устройство формирователь 17 длительности паузы обеспечивает синхронизацию N-разрядного регистра 12 сдвига с запаздыванием на время гарантированной паузы относительно выходного сигнала формирователя 10 синхроимпульсов широтко-импульсного модулятора 11, чем достигается ограничение максимальной длительности управляющих импульсов, формируемых на входах управления силовых преобразовательных ячеек. 2 ил. 4Т (Л с САд 1 tpuff

| Юрченко А.И | |||

| Шуваев Ю,Н | |||

| Основные структурные схемы управления мн о- гофазных импульсных стабилизаторов и преобразователей | |||

| Вопросы радиоэлектроники | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Сепаратор-центрофуга с периодическим выпуском продуктов | 1922 |

|

SU128A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Многофазный импульсный стабилизатор | 1982 |

|

SU1019413A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-06-15—Публикация

1985-12-11—Подача