Изобретение относится к электросвязи и может использоваться для кодирования и декодирования информации, передаваемой, например, в цифровых вычислительных машинах.

Целью изобретения является повышение достоверности приема.

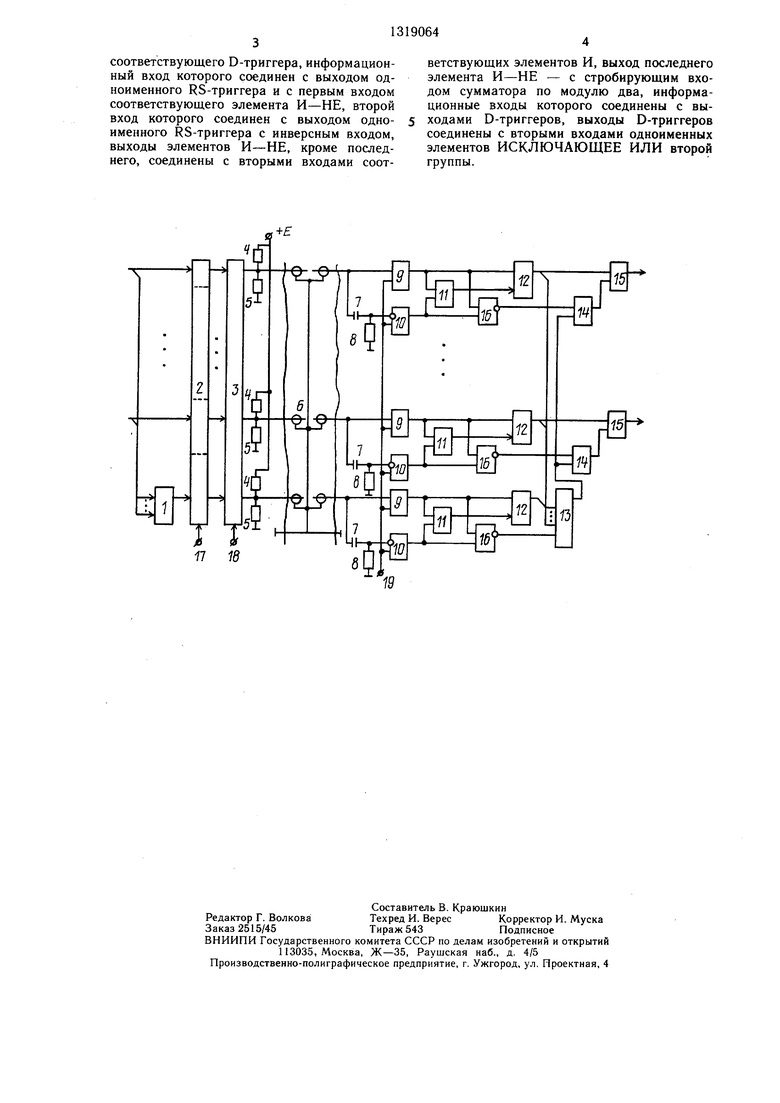

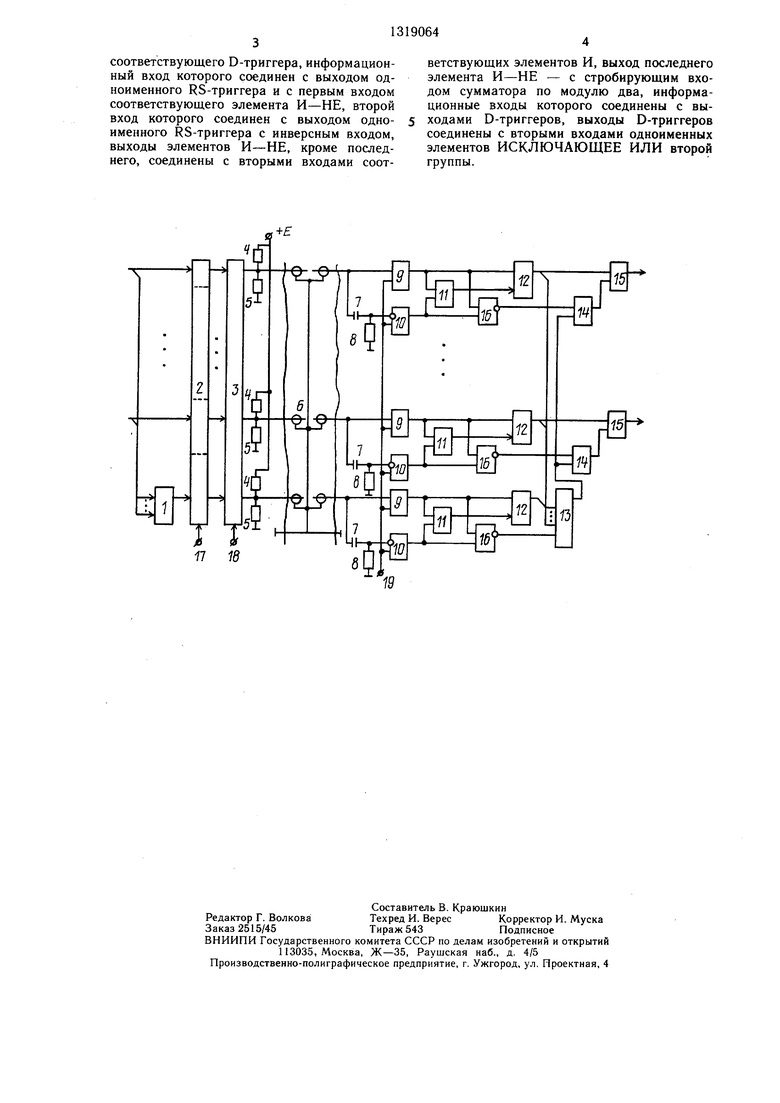

На чертеже изображено предлагаемое устройство.

Устройство содержит на передающем конце сумматор 1 по модулю два, регистр 2, формирователь 3 импульсов, делитель напряжения на первых регистрах 4 и вторых регистрах 5, линии 6 связи, на приемном конце - элементы задержки на конденсаторах 7 и регистрах 8, RS-триггеры 9, RS-триггеры 10 с инверсным входом, первую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 11, D-триггеры 12, сумматор 13 по модулю два, элементы ИЛИ 14, вторую группу элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 15, элементы И-НЕ 16. На входы 17-19 подаются управляющие импульсы установки.

Устройство работает следующим образом.

В исходном состоянии линии 6 связи находятся под потенциалом, равном половине напряжения питания устройства. При передаче информации на выходе формирователей 3, в качестве которых могут быть использованы кабельные усилители, ключевые схемы и т. д., формируются па- рафазные эквиваленты сигналов «О и «1. В приемнике первый RS-триггер 9 и второй RS-триггер 10 с инверсным входом устанавливаются в единичные состояния в очередности поступления парафазных пар импульсов. В D-триггер 12 записывается соответствующая информация по переднему фронту импульса, получающегося на выходе элемента первой группы ИСКЛЮЧАЮЩЕЕ ИЛИ 11. Считается, что передача состоялась, если пришла пара парафазных посылок. В этом случае на выходе элементов И-НЕ устанавливается низкий уровень.

Если в каком-либо разряде происходит нарушение передачи из-за поме)(и в линии 6 связи, периодической потери контактов в соединителях приемника и передатчика и т. д., то на входах RS-триггеров 9 и 10 будет либо однофазная посылка, либо отсутствие сигнала. В любом случае на выходе элемента И-НЕ 16 останется высокий потенциал. При этом возможны следующие варианты. Информация, полученная на выходе D-триггера 12, соответствует передаваемой, что подтверждает результат свертки на выходе сумматора 13 по модулю два, или не соответствует передаваемой. В последнем случае на выходе сумматора 13 по модулю два устанавливается высокий потенциал и на выходе элемента И 14 соответствующего разряда устанавливается высокий потенциал, который проинвертирует значение разряда на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 второй группы.

Если выходит из строя контрольный разряд, то. элемент И-НЕ 16 этого раз- ряда запрещает работу по стробирующему входу сумматора 13 по модулю два.

Анализируя состояние элементов И-НЕ 16 в процессе приема информации, можно регистрировать сбои, а также проверять состояние тракта передачи информации в диагностическом режиме.

5

0

5

0

5

0

5

0

5

Формула изобретения

Устройство для приема и передачи цифровой информации, содержащее на передающей стороне регистр, п входов которого являются входами устройства и соединены с входами сумматора по модулю два, выход которого соединен с входом(п+1)-го разряда регистра, на приемной стороне первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, сумматор по модулю два, группу элементов И, выходы которых подключены к первым входам соответствующих элементов второй группы ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых являются выходами устройства, отличающееся тем, что, с целью повышения достоверности приема, в него введены на передающей стороне формирователь сигналов, делители напряжения на первом и втором резисторах, входы формирователя сигналов соединены с соответствующими выходами регистра, одни выводы первого и второго резисторов каждого делителя напряжения подключены соответственно к клемме нулевого потенциала и к положительной клемме источника питания, другие выводы соединены с выходом формирователя сигналов и одним концом соответствующей линии связи, иа приемной стороне - элементы задержки иа резисторе и конденсаторе, RS-триггеры, RS-трлггеры с инверсным входом, элементы И-НЕ, D-триггеры, первые входы элементов И соединены с выходами сумматора по модулю два, другой конец соответствующей линии связи соединен с первым входом одноименного RS-триггера и через конденсатор одноименного элемента задержки - с первым выводом резистора одноименного элемента задержки и с инверсным входом одноименного RS-триггера с инверсным входом, вторые выводы резисторов элементов задержки соединены с клеммой нулевого потенциала, вторые входы RS-триггеров и RS- триггеров с инверсным входом соединены с щиной установки RS-триггеров в исходное состояние, выходы одноименных RS-триггеров и RS-триггеров с инверсным входом соединены соответственно с первым и вторым входами соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ первой группы, выход которого соединен со стробирующим входом

соответствующего D-триггера, информационный вход которого соединен с выходом одноименного RS-триггера и с первым входом соответствующего элемента И-НЕ, второй вход которого соединен с выходом одноименного RS-трнггера с инверсным входом, выходы элементов И-НЕ, кроме последнего, соединены с вторыми входами соответствующих элементов И, выход последнего элемента И-НЕ - с стробирующим входом сумматора по модулю два, информационные входы которого соединены с вы- ходами D-триггеров, выходы D-триггеров соединены с вторыми входами одноименных элементов ИСКЛЮЧАЮЩЕЕ ИЛИ второй группы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь перемещения в код | 1989 |

|

SU1646055A1 |

| Электронные часы с фиксацией и документированием времени | 1988 |

|

SU1552147A1 |

| Устройство для управления ленточным перфоратором | 1985 |

|

SU1310860A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ M-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1989 |

|

RU2030103C1 |

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство для управления группой N статических преобразователей частоты,включенных параллельно по входу и выходу | 1986 |

|

SU1388973A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ М-ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2112313C1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1439744A1 |

| Устройство для передачи и приема цифровой информации | 1986 |

|

SU1355976A1 |

Изобретение относится к электросвязи и может использоваться для кодирования и декодирования информации, передаваемой, например, в цифровых вычислительных машинах. Цель изобретения - повышение достоверности приема. Устройство содержит на передающем конце сумматор по модулю два, регистр, формирователь импульсов, первые и вторые резисторы, группы делителей напряжения, на приемном конце: конденсаторы и резисторы, группу элементов задержки, группу RS-триггеров, группу RS-триггеров с инверсным входом, первую и вторую группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу D-триггеров, сумматор по модулю два, группу элементов И, группу элементов И-НЕ. Устройство предназначено для построения высоконадежных трактов передачи цифровой информации п-разрядным параллельным кодом с одним контрольным разрядом «нечетность по «од- нопроводным линиям связи, второй провод которых, являюш,ийся экраном, объединяется вне передатчика и приемника и соединяется с шиной низкого потенциала источника питания ограниченным числом связей. За счет введения шинных формирователей, резисторного делителя, конденсаторов, нагрузочных резисторов, RS-триггеров, элементов И-НЕ производится контроль за исправным состоянием устройства и исправлением одиночных ошибок. 1 ил. (Л с 00 со а 4

П 18

| Устройство для передачи и приема цифровой информации | 1985 |

|

SU1252781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-22—Подача