г

42 00

со 4

4

Изобретение относится к вычисли тельной технике и может быть использовано в системах автоматической работки данных.

Цель изобретения - повышение быст родействия устройства.

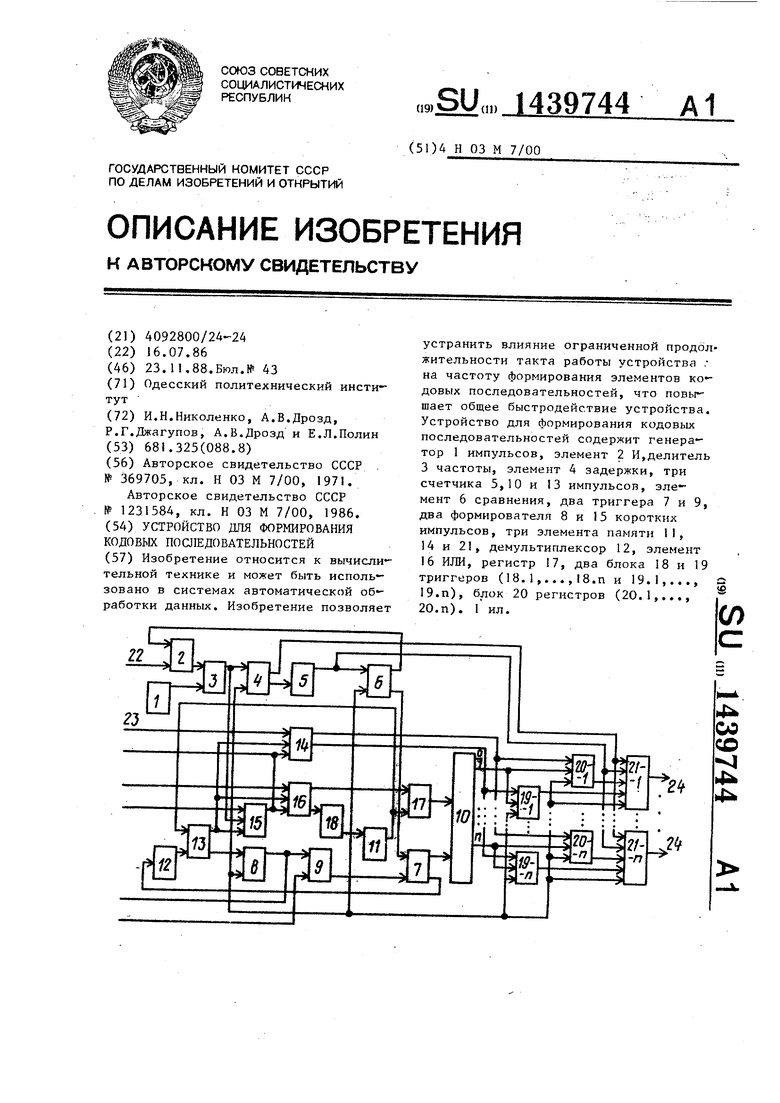

На чертеже приведена функциональная схема устройства.

Устройство содержит генератор 1 импульсов, элемент И 2, делитель 3 частоты, элемент 4 задержки, первый счетчик 5 импульсов, элемент 6 сравнения, первый триггер Т, первый формирователь 8 коротких импульсов, второй триггер 9э второй счетчик 10 импульсов, первый элемент 11 памяти, демультиплексор 12, третий счетчик 1 импульсов, второй элемент 14 памяти, второй формирователь 15 коротких импульсов, элемент ИЛИ 16, регистр 17, первый 18 и второй 19 блоки триг геров (18-1,..,,8-п) и (19-1,..., 19-п), блок 20 регистров (20-1,,.., 20-п) и третий элемент 21 памяти. Кроме того, обозначены входы запуска 22 и начальной установки 23 устройства и выходы 24 устройства.

Устройство работает следующим образом.

Перед пуском устройства сигналом Начальная установка, поступающим на вход 23 начальной установки устройства, сбрасывается в 1юль счетчик

10 адреса,TV-триггеры 18-1,0.,,18-п

35

первого 1 8 и 1 9-1 ,.,., 19-п второго 1 9 блоков триггеров,регистры 20- ,«., 20-п блока 20 регистров, устанавливается в единичное состояние делитель 3 частоты, счетчик 5 и счетчик 13 адреса, Q а через элемент ИЛИ 16 сбрасываются в ноль также регистр 1 7 и RS-триггер 9.

Импульс запуска, поступающий на вход установки D-триггера 7, устанавливает его в единичное состояние, раз- решая прохождение импульсов с выхода генератора 1 через элемент И 2 на счетный вход счетчика 13 адреса и вход делителя 3 частоты. С первого и второго выходов делителя 3 частоты

50

снимаются синхросигналы типа меандр, отмеряющие собственно такты и полутакты работы устройс,тва. Синхро.сиг- налы с первого выхода делителя 3 частоты поступают на вход элемента 4 за-

держки, с выхода которого подаются на счетный йход счетчика 5, Первый импульс с выхода элемента 4 задержки переводит счетчик 5 в следующее, нуле

0

5

Q

0

5

вое состояние. Код с выходов счетчика

5поступает на первый вход элемента

6сравнения.

Нулевой код выхода счетчика 10 адреса поступает на адресный вход первого элемента 1 памяти, хранящего номера тактов, в которых происходит изменение хотя бы одного из выхог дов .4 устройства.

По нулевому адресу элемент 11 памяти считьюает первый код номера такта. Этот код поступает на второй вход элемента 6 сравнения, который уменьшает значение кода на единицу младшего разряда и сравнивает полученный результат с кодом счетчика 5. При совпадении сравю-1ваемых кодов потенциал логического О с инверсного выхода элемента 6 сравнения поступает на вход управления демультиплексора 2з а единичный сигнал с прямого выхода элемента 6 сравнения поступает на первый фс рмирователь 8 коротких импульсов. При этом формируется короткий единичный импульс, устанавливающий по S-входу RS-триггер 9 в единичное состояние. Единичный сигнал с прямого выхода RS-триггера 9 ется на входы выборки второго 14 и третьего 21 элементов памяти, а также на вход разрешения счета счетчика 13 адреса, который под действием синхросигналов, поступающих на его счетный вход, начинает изменять свое состояние, формируя на адресных входах второго 14 и третьего 21 элементов памяти последовательность значений адреса.

Во втором элементе 14 памяти хранится последовательность групп кодов. Каждая группа кодов взаимооднозначно соответствует одному коду (номеру такта) из элемента 11 памяти и содержит коды номеров каналов(номеров выходов 24 устройства), которые изменяют свое состояние в соответствующем такте работы устройства. В группе коды перечисляются в произвольном порядке. Код номера канала содержит дополнительный разряд, принимающий в последнем коде каждой группы единичное эна чение и нулевое значение в других кодах. Этот признак окончания группы кодов считывается с управляющего выхода второго элемента 14 памяти.

В третьем элементе 21 памяти хранятся двухразрядные коды переключений, взаимооднозначно соответствующие

кодам групп второго элемента 4 па мяти. Первые (вторые) разряды кодов переключений указывают единичным значением на изменение выхода устройства на первом (втором) полутакте та та по отношению к соответствующему полутакту предшествующего такта.

Считьюаемые с второго элемента 14 памяти коды номеров каналов группы поступают на информационные входы регистра 17, ас его выходов на адресные входы демультиплексора 12, обеспечивая последовательное форми - рование единичных импульсов на его выходах, соответств пощих номерам каналов группы,

С первого и второго выходов третьего элемента 21 памяти снимаются соответственно первый и второй раз- ряды кода переключений, поступающие на У входы TV-триггеров 8-1,..., 18-п первого блока 18 и TV-триггеров 9-1,. .. 51 9-п второго блока 19 соот - ветственно (единичное значение на V-входе TV-триггера разрешает изменять его состояние на инверсное с приходом единичного импульса (фронта) на Т-вход TV-триггера). На Т-входы i-x TV-триггеров 18-i, 19-i первого 18 и второго 19 блоков (i 1, п) поступают единичные импульсы либо нулевой уровень с i-x выходов демуль- типлексора 12 Единичные импульсы ин вертируют TV-триггеры, выбранные по V-входу. Сигналы с выходов TV-триг- геров первого 18 и второго 19 блоков поступают на первый и второй входы соответствующих регистров 20-1,,..,

0

5

0

5

0

5

окончания группы. Этот сигнал поступает на вход второго, формирователя 15 коротких импульсов, с выхода которого сформирован1 ый короткий импульс с задержкой на величину t. поступает через элемент ИЛИ 16 на вход сброса регистра 17 и на R-вход RS-триггера 9. При этом происходит обнуление регистра 17 и RS-триггера 9. Сигнал с прямого выхода RS-триггера 9 останавливает изменение состояний счетчика 13 адреса и переводит по входам выборки второй 14 и третий 21 элементы памяти в нулевое состояние. Сигнал с инверсного выхода RS-триггера 9 переводит в следующее состояние счетчик 10 адреса. При этом из первого элемента I1 памяти считывается следующий код номера такта.

Импульсы с выхода элемента 4 задержки обеспечивают отсчет счетчиком 5 тактов реального времени и при установке старшего разряда счетчика 5 в единичное значение D-триггер 7 переходит в исходное нулевое состояние, завершая работу устройства.

Формула изобретения

Устройство для формирования кодовых последовательностей, содержащее генератор импульсов, выход которого соединен с первым входом элемента И, выход которого соединен с информационным входом делителя частоты, первый выход которого через элемент задержки соединен со счетным входом первого счетчика импульсов, пер-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1554115A1 |

| Устройство для формирования кодовых последовательностей | 1988 |

|

SU1499438A2 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1345322A1 |

| Устройство для формирования кодовых последовательностей | 1986 |

|

SU1406736A1 |

| Устройство для вычисления полиномов | 1986 |

|

SU1432509A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Устройство для вычисления значений полинома | 1986 |

|

SU1348827A1 |

| Устройство для формирования кодовых последовательностей | 1983 |

|

SU1231584A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах автоматической обработки данных. Изобретение позволяет устранить влияние ограниченной продолжительности такта работы устройства . на частоту формирования элементов кодовых последовательностей, что повышает общее быстродействие устройства. Устройство для формирования кодовых последовательностей содержит генератор 1 импульсов, элемент 2 И,делитель 3 частоты, элемент 4 задержки, три счетчика 5,10 и I3 импульсов, элемент 6 сравнения, два триггера 7 и 9, два формирователя 8 и 15 коротких импульсов, три элемента памяти II, 14 и 21, демультиплексор 12, элемент 16 ИЛИ, регистр I7, два блока 18 и 19 триггеров (18.1,...,18.П и 19.,.«., 9.п), блок 20 регистров (20.1,..., 20.п). 1 ил. S СО

20-п блока 20. На синхровходы регист- 40 второй выходы первого счетчика

ров 20-1,...,20-п поступает синхросигнал с второго выхода делителя 3 частоты, а на управляющие входы поступает сигнал с выхода элемента 4

импульсов соединены соответственно с первым входом элемента сравнения и входом установки первого триггера, выход которого соединен с вторым

задержки, обеспечивая при нулевом зна-дз входом элемента И, первый формирова- чении прием информации, а при единичном значении ее сдвиг на один разряд. В результате приема информации на выходе регистра 20-i блока 20 появляется значение сигнала, принятого с вы-gQ хода TV-триггера 19-i первого блока 1 19, а в результате сдвига - значение сигнала, записанного в регистр 20-i с выхода TV-триггера 19-i второго блока 19.

Одновременно со считьшанием последнего кода группы на управляющем выходе второго элемента 14 памяти счи- тьшается единичный сигнал признака

тель коротких импульсов, выход которого соединен с В-входом второго триггера, инверсный выход которого соединен со счетным входом второго счетчика импульсов, выход которого соединен с адресным входом первого элемента памяти, выход которого соединен с вторым входом элемента срав нения, выход которого соединен с gg входом управления демультиплексора, третий счетчик импульсов, выход кото рого соединен с адресным входом второго элемента памяти, первый выход которого соединен с входом второго

импульсов соединены соответственно с первым входом элемента сравнения и входом установки первого триггера, выход которого соединен с вторым

входом элемента И, первый формирова-

тель коротких импульсов, выход которого соединен с В-входом второго триггера, инверсный выход которого соединен со счетным входом второго счетчика импульсов, выход которого соединен с адресным входом первого элемента памяти, выход которого соединен с вторым входом элемента сравнения, выход которого соединен с входом управления демультиплексора, третий счетчик импульсов, выход кото рого соединен с адресным входом второго элемента памяти, первый выход которого соединен с входом второго

формирователя коротких импульсов, выход которого соединен с первым входом элемента ИЛИ, второй выход второго элемента памяти и выход эле мента ИЛИ соединены соответственно с информационным входом и входом . сброса регистра, выход которого соединен с адресным входом демульти плексора, выходы которого соединены с Т входом одноименных триггеров первого блока триггеров, и второй блок триггеровj вход синхронизации первого триггера являе.тся входом запуска устройства, входы установки триггеров ;Первого и второго блоков триггеров :0бъединены с вторым входом элемента ИЛИ, с входами установки первого. Второго и третьего счетчиков импуль - сов и делителя частоты и являются входом начальной установки устройства отличающееся тем, что, с целью повышения быстродействия ройства, в него введены блок регист - : ров и третий элемент памяти, первый и второй выходы которого соединены с V-входами триггеров, соответственно первого и. второго блоков триггеров,

прямой выход второго триггера соединен с входами выборки второго и третьего элементов памяти и входом разрешения счета третьего счетчика импульсов, счетный вход которого подключен к выходу элемента И, R- вход второго- триггера подключен к выходу элемента ИЛИ, прямой выход элемента сравнения соединен с входом первого формирователя коротких импулсов, адресный вход третьего элемента памяти подключен к выходу третьего счетчика импульсов, выходы триггеров первого и второго блоков триггеров соединены соответственно с первыми и вторыми информационными входами одноименных регистров блока регистров, второй выход делителя частоты соединен с входами синхронизации регистров блока регистров, управляю щие входы которых подключены к выходу элемента задержки, входы установки регистров блока регистров подключены к ВХОДУ начальной установки устройства, выходы блока регистров являются выходами устройства.

| БИЕЛИОТЕКА | 0 |

|

SU369705A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования кодовых последовательностей | 1983 |

|

SU1231584A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-23—Публикация

1986-07-16—Подача