Изобретение относится к импульсной технике, а именно к устройствам с двумя устойчивыми состояниями, и может быть использовано в цифровых интегральных микросхемах с инжекционным питанием.

Цель изобретения - уменьшение потребляемой мощности.

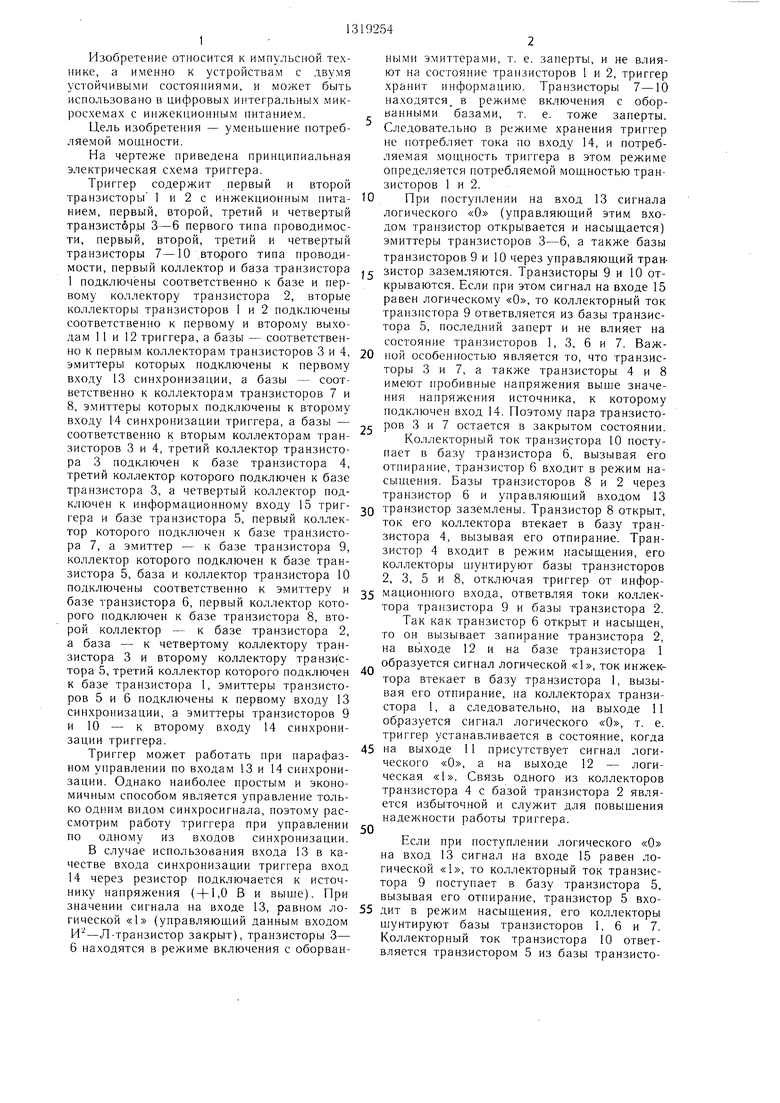

На чертеже приведена принципиальная электрическая схема триггера.

Триггер содержит первый и второй транзисторы 1 и 2 с инжекционным питанием, первый, второй, третий и четвертый транзист6р.ы 3-6 первого типа проводимости, первый, второй, третий и четвертый транзисторы 7-10 .второго типа проводимости, первый коллектор и база транзистора 1 подключены соответственно к базе и первому коллектору транзистора 2, вторые коллекторы транзисторов 1 и 2 подключены соответственно к первому и второму выходам 1 1 и 12 триггера, а базы - соответственно к первым коллекторам транзисторов 3 и 4, эмиттеры которых подключены к первому входу 13 синхронизации, а базы - соответственно к коллекторам транзисторов 7 и 8, эмиттеры которых подключены к второму входу 14 синхронизации триггера, а базы - соответственно к вторым коллекторам транзисторов 3 и 4, третий коллектор транзистора 3 подключен к базе транзистора 4, третий коллектор которого подключен к базе транзистора 3, а четвертый коллектор подключен к информационному входу 15 триггера и базе транзистора 5, первый коллектор которого подключен к базе транзистора 7, а эмиттер - к базе транзистора 9, коллектор которого подключен к базе транзистора 5, база и коллектор транзистора 10 подключены соответственно к эмиттеру и базе транзистора 6, первый коллектор которого подключен к базе транзистора 8, второй коллектор - к базе транзистора 2, а база - к четвертому коллектору транзистора 3 и второму коллектору транзистора 5, третий коллектор которого подключен к базе транзистора 1, эмиттеры транзисторов 5 и 6 подключены к первому входу 13 синхронизации, а эмиттеры транзисторов 9 и 10 - к второму входу 14 синхронизации триггера.

Триггер может работать при парафаз- ном управлении по входам 13 и 14 синхронизации. Однако наиболее простым и экономичным способом является управление только одним видом синхросигнала, поэтому рассмотрим работу триггера при управлении по одному из входов синхронизации. В случае использования входа 13 в качестве входа синхронизации триггера вход 14 через резистор подключается к источнику напряжения ( + 1,0 В и выше). При значении сигнала на входе 13, равном логической «1 (управляющий данным входом И -Л-транзистор закрыт), транзисторы 3- 6 находятся в режиме включения с оборванными эмиттерами, т. е. заперты, и не влияют на состояние транзисторов 1 и 2, триггер хранит информацию. Транзисторы 7-10 находятся, в режиме включения с обор- нанными базами, т. е. тоже заперты. Следовательно в режиме хранения триггер не потребляет тока по входу 14, и потребляемая мощность триггера в этом режиме определяется потребляемой мощностью транзисторов 1 и 2.

0 При поступлении на вход 13 сигнала логического «О (управляющий этим входом транзистор открывается и насыщается) эмиттеры транзисторов 3-6, а также базы транзисторов 9 и 10 через управляющий тран5 зистор заземляются. Транзисторы 9 и 10 открываются. Если при этом сигнал на входе 15 равен логическому «О, то коллекторный ток транзистора 9 ответвляется из базы транзистора 5, последний заперт и не влияет на состояние транзисторов 1, 3, 6 и 7. Важ0 ной особенностью является то, что транзисторы 3 и 7, а также транзисторы 4 и 8 имеют пробивные напряжения выше значения напряжения источника, к которому подключен вход 14. Поэто.му пара транзисто ров 3 и 7 остается в закрытом состоянии. Коллекторный ток транзистора 10 поступает в базу транзистора б, вызывая его отпирание, транзистор 6 входит в режим насыщения. Базы транзисторов 8 и 2 через транзистор 6 и управляющий входом 13

0 транзистор заземлены. Транзистор 8 открыт, ток его коллектора втекает в базу транзистора 4, вызывая его отпирание. Транзистор 4 входит в режим насыщения, его коллекторы шунтируют базы транзисторов 2, 3, 5 и 8, отключая триггер от инфор5 мационного входа, ответвляя токи коллектора транзистора 9 и базы транзистора 2. Так как транзистор 6 открыт и насыщен, то он вызывает запирание транзистора 2, на вь |ходе 12 и на базе транзистора 1 образуется сигнал логической «1, ток инжектора втекает в базу транзистора 1, вызывая его отпирание, на коллекторах транзистора 1, а следовательно, на выходе 11 образуется сигнал логического «О, т. е. триггер устанавливается в состояние, когда

5 на выходе 11 присутствует сигнал логического «О, а на выходе 12 - логическая «1. Связь одного из коллекторов транзистора 4 с базой транзистора 2 является избыточной и служит для повыщения надежности работы триггера.

0

Если при поступлении логического «О на вход 13 сигнал на входе 15 равен логической «, то коллекторный ток транзистора 9 поступает в базу транзистора 5, вызывая его отпирание, транзистор 5 вхо5 дит в режим насыщения, его коллекторы шунтируют базы транзисторов 1, 6 и 7. Коллекторный ток транзистора 10 ответвляется транзистором 5 из базы транзисто0

pa 6, последний заперт и не влияет на состояние транзисторов 2, 4 и 8. Базы транзисторов 6 и 7 через транзистор 5 и управляющий входом 13 тра,нзистор заземлены. Транзистор 7 открыт, ток его коллектора втекает в базу транзистора 3, вызывая его отнирание. Транзистор 3 входит в режим насыщения, его коллекторы HIVHTH- руют базы транзисторов 1, 4, 6 и 7.

Для более надежной работы триггера целесообразно известными нутями (например, перекос токов инжекторов) сделать включение транзистора 5 более быстрым, чем включение транзистора 6. Так как транзистор 5 (в первый момент), а затем и транзистор 3 (на все время действия синхросигнала) открыты и находятся в режиме насыщения, то ток инжектора ответвляется из базы транзистора 1, вызывая его запирание, на выходе 11 и на базе транзистора 2 образуется сигнал логической «1, ток инжектора втекает в базу транзистора 2, вызывая его отпирание, на коллекторах транзистора 2, а следовательно на выходе 12, образуется сигнал логического «О, т. е. триггер устанавливается в состояние, когда на выходе 11 присутствует сигнал логической «1, а на выходе 12 - логический «О. Причем, если теперь сигнал на входе 15 изменяется на логический «О, то, так как транзистор 3 шунтирует базы транзисторов 6 и 7 и базу транзистора 1, состояние транзисторов 7 и 8, а также транзисторов 1, 2, 3, 4 и 6 не изменяется.

При значении синхросигнала, равном логическому «О, триггер хранит информацию.

Таким образом, при управлении по входу

13информационный сигнал передается на выходы 11 и 12 только при поступлении на вход 13 отрицательного перепада напряжения, т. е. григгер при таком управлении выполняет функцию /З-триггера с динамическим синхровходом.

При использовании входа 14 в качестве тактового входа триггера вход 13 подключается к общей пжне (заземляется), а вход

14может быть подключен либо к управляемому, либо к неуправляемому источнику тока. Наиболее простым является второй способ управления.

Рассмотрим вариант, когда вход 14 подключен через источник тока к источнику напряжения, причем источник тока направлен от источника напряжения к входу 14.

При значении тактового сигнала, равном логическому «О, ток источника тока, подключенного к входу 14, ответвляется в управляющий этим входом И Л-транзистор. Транзисторы 7-10 обесточены, а следовательно, заперты, поэтому транзисторы 3-6 также заперты и не влияют на состояние транзисторов 1 и 2. Триггер хранит информацию.

При поступлении на вход 14 сигнала логической «1 (т. е. положительного перепада тактового сигнала) ток источника, подключенного к входу 14. вызывает отпирание транзисторов 9 и 10, одного нз транзисторов 5 или 6 (в зависимости от сигнала на входе 15), затем и одного из транзисторов 7 или 8, а затем одного из транзисторов 3 или 4, т. е. тригг ер работает так же как и при использовании входа 13 в качестве тактового входа триггера, только в случае управления по входу 14 триггера

0 срабатывает по положительному нерепаду напряжения.

С11ижение потребляемой мощности дости- гаетс я за счет того, что в режиме хранения триггер потребляет мощность, равную

5 только потребляемой мощности двух И Л- вентилей, и так как в нредложенной схеме отсутствует резистивный элемент, то для нее возможно снижение напряжения питания до 1,0 В, что дает дополнительно снижение потребления мощности в режиме хранения

0 на 15-20%.

Снижение потребляемой мощности достигается без ухудшения динамических параметров известного триггера.

25

Формула изобретения

Триггер, содержащий два транзистора с инжекционным питанием первого типа проводимости, три транзистора первого типа проводимости и три транзистора второго

0 типа проводимости, первый коллектор и база первого транзистора с инжекционным питанием подключены соответственно к базе и первому коллектору второго транзистора с инжекц ионным питанием, вторые коллекторы первого и второго транзисторов с ин5 жекционным питанием подключены соответственно к первому и второму выходам триггера, а базы - соответственно к первым коллекторам первого и второго транзисторов первого типа проводимости, эмиттеры которых подключены к первому входу синхро0 низации триггера, а базы соответственно подключены к коллекторам первого и второго транзисторов второго типа проводимости, эмиттеры которых подключены к второму входу синхронизации триггера, а базы

соответственно подключены к вторым коллекторам первого и второго транзисторов первого типа проводимости, третий коллектор первого транзистора первого типа проводимости подключен к базе второго транзистора первого типа проводимости, третий коллектор

0 которого подключен к базе нервого транзистора первого типа проводимости, а четвертый коллектор подключен к информационному входу триггера и базе третьего транзистора первого типа проводимости, первый коллектор которого подключен к базе пер5 вого транзистора второго типа проводимости, а эмиттер - к базе третьего транзистора второго типа проводимости, коллектор которого подключен к базе третьего транзистора первого типа проводимости, отличающийся тем, что, с целью уменьшения потреб ляемой МОШ.НОСТИ, в него введены четвертый транзистор первого типа проводимости и четвертый транзистор второго типа проводимости, база и коллектор которого подключены соответственно к эмиттеру и базе четвертого транзист.рйупервого типа проводимости, первы й коллектор которого подключен к базе втор0 г«у т нзястора второго типа проводимости,.вт9.р.ок -1 оллектор - к базе второго транз 1 тора инжекционным питанием, а база подключена к четвертому допол

нительному коллектору первого транзистора первого типа проводимости и второму дополнительному коллектору третьего транзистора первого типа проводимости, третий дополнительный коллектор которого подключен к базе первого транзистора с инжекционным питанием, эмиттеры третьего и четвертого транзисторов первого типа проводимости подключены к первому входу синхронизации триггера, а эмиттеры третьего и четвертого транзисторов второго типа проводимости - к второму входу синхронизации триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггер | 1983 |

|

SU1150734A1 |

| Устройство согласования интегральных инжекционных схем с линиями передачи коллективного пользования | 1983 |

|

SU1092726A1 |

| Устройство согласования | 1984 |

|

SU1173552A1 |

| Устройство согласования | 1986 |

|

SU1383483A1 |

| Триггер | 1986 |

|

SU1319253A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| Логический элемент | 1984 |

|

SU1173551A1 |

| Устройство согласования | 1980 |

|

SU902262A1 |

| Устройство согласования | 1983 |

|

SU1138942A1 |

| Мультиплексор | 1985 |

|

SU1277383A1 |

Изобретение относится к импульсноГ технике, а именно к устройствам с двумя устойчивыми состояниями, может быть использовано в цифровых интегральных микросхемах с инжекционным нитанием. 1Де, изобретения - уменьшение потребляемо мощности. Устройство содержит транзисторы I и 2, с инжекционным питанием первого типа проводимости, транзисторы 35 первого типа проводимости, транзисторы 7 9 второго типа проводимости. Для достижения поставленной цели в устройство введены транзисторы 6 и 10 соответственно первого и второго типов проводимости. 1 ил. (ВЯ , , : WW I |ЗРЭК«1. IQD ГС 01 )4.

| Агаханян Т | |||

| М | |||

| Интегральные микросхемы.- М.: Энергоатомиздат, 1983, с | |||

| СПОСОБ ДЛЯ РАДИОСНОШЕНИЙ С ПОЕЗДАМИ | 1922 |

|

SU397A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-30—Подача