Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах для программного управления и коммутации каналов.

Цель изобретения - упрощение устройства.

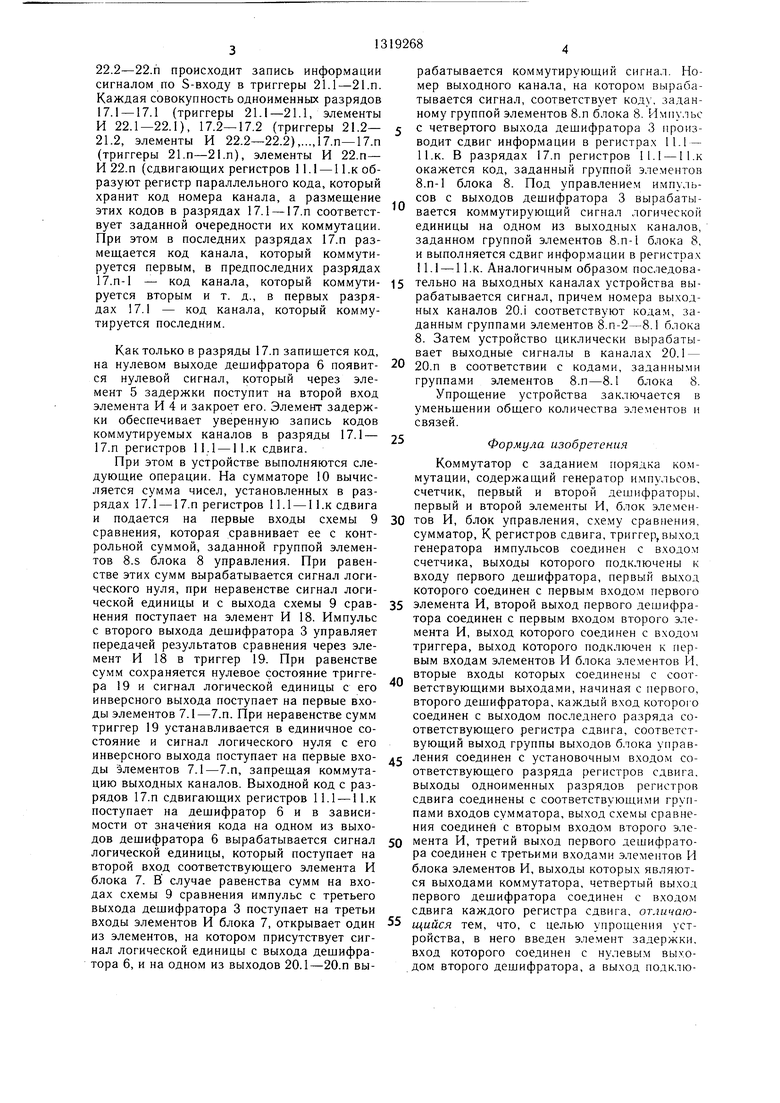

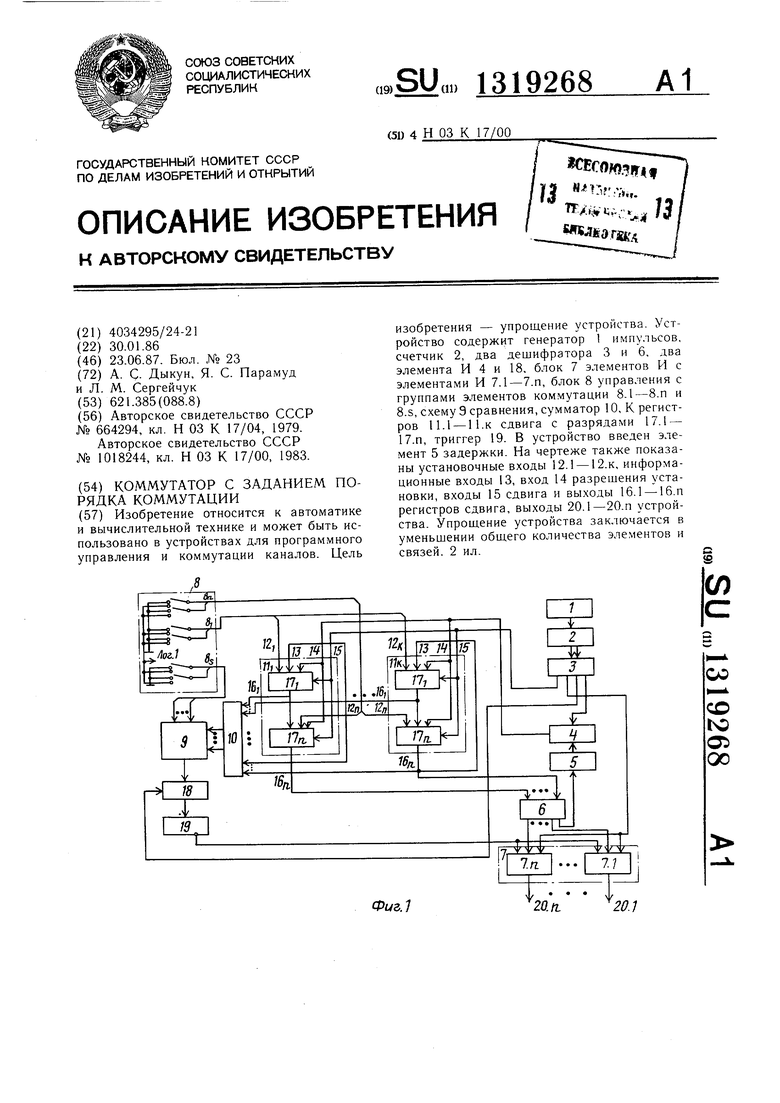

На фиг. 1 приведена схема коммутатора; на фиг. 2 - схема регистра сдвига.

Коммутатор с заданием порядка коммутации содержит генератор 1 импульсов, счетчик 2, дешифратор 3, элемент И 4, элемент 5 задержки, дешифратор 6, блок 7 элементов И с элементами И 7.1-7:п, блок 8 управления с группами элементов 8.1-8.п и 8.S коммутации, схему 9 сравнения, сумматор 10, регистры 11.1 -11.к сдвига, установочные входы 12.1 - 12.П регистра сдвига, информационный вход 13 регистра сдвига, вход 14 разрешения установки регистра сдвига, вход 15 сдвига регистра сдвига, выходы 16.1 - 16.П разрядов 17.1 - 17.П регистра сдви12.2-12.П соединены с первыми входами элементов И-НЕ 22.1, 22.2-22.п соответственно, вход 13 с D-входом триггера 21.1, вход 14 с вторыми входами элементов И-НЕ 22.1,

5 22.2-22.П, вход 15 с С-входом триггеров 21.1, 22.2-22.П, выходы триггеров 21.1, 21.2-21.п с выходами 16.1, 16.2-16.п соответственно, дополнительно выходы триггеров 21.1, 21.2- 21.п соединены с D-входами триггеров 21.2, 21.3-21.П соответственно. Выходы элемен10 тов И-НЕ 22.1, 22.2-22.П соединены с S-BXO- дами триггеров 21.1 21.2-21.п соответственно.

Коммутатор с заданием порядка коммутации работает следующим образом.

5 В исходном состоянии счетчик 2, регистры 11.1 -11.к сдвига и триггер 19 обнулены. Цепи установки в исходное состояние указанных элементов не показаны. Так как регистры 11.1 -11.к сдвига обнулены, то с выходов 16.П указанных регистров на входы де25

30

га, элемент И 18, триггер 19, выходы ком- 20 шифратора 6 поступают сигналы логического мутатора20.1-20.п. Группы элементов 8.1-нуля. Вследствие этого на нулевом выходе

8.П коммутации содержат по К элементов коммутации, например тумблеров.

Выход генератора 1 соединен с входом счетчика 2, выходы которого соединены с входами дешифратора 3, первый выход которого соединен с первым входом элемента И 4, второй выход с первым входом элемента И 18, третий выход с третьими входами элементов И 7.1-7.П, четвертый выход с входами 15 сдвига регистров 11.1.-11.к сдвига, выход элемента И 4 соединен с входами 14 разрешения установки регистров 11.1 -11.к сдвига, выход элемента 5 задержки соединен с вторым входом элемента И 4, нулевой выход дешифратора 6 соединен с входом

элемента 5 задержки, остальные выходы де- 35 тора связаны соотношением -1. Нуле- шифратора 6 соединены с вторыми входамивой код не используется для кодирования

соответствующих элементов И 7.1-7.п, вы-выходных каналов коммутатора. Изменение

ходы которых являются выходами 20.1-20.пкодов с помощью элементов групп 8.1-8.п

коммутатора, выходы групп элементов 8.1 - 8.П коммутации соединены с установочными входами соответствующих одноименных разрядов 17.1 - 17.П регистров 11.1 - 11 .к сдвига, выходы элементов 8.S коммутации соединены с вторыми входами схемы 9 сравнения, выход которой соединен с вторым входом элемента И 18, выходы сумматора 10 соединены с первыми входами схемы 9 сравнения, выходешифратора 6 будет сигнал логической единицы, который через элемент 5 задержки поступает на второй вход элемента И 4 и подготавливает его к открыванию. С блока 8 управления задается очередность коммутации выходных каналов (выходов) 20.1-20.п коммутатора. Каждая группа элементов 8.1-8.П, состоящая из К элементов коммутации, задает код коммутируемого канала, а последовательность группы 8.1-8.п задает последовательность коммутации выходных каналов. Количество элементов коммутации К в группах элементов 8.1-8.п, количество групп элементов п в блоке 8 управления, количество выходных каналов п коммутаобеспечивает возможность ко.ммутации выходных каналов с любой очередностью. С по- мощью группы элементов 8.s задается конт45

ды 16.1 - 16.П разрядов регистров сдвига соединены с соответствующими группами входов сумматора 10, выходы 16.п разрядов регистра сдвига соединены с входами дешифратора 6 и входами 13 регистров 11.1 - 11.к сдвига, выход элемента И 18 соединен с входом триггера 19, выход которого соединен с первыми входами элементов И 7.1-7.п. Регистр ll.i сдвига (фиг. 2) содержит триггеры 21.1-21.п, элементы И-НЕ 22.1, 22.2-

рольная сумма кодов коммутируемых каналов, которая равна сумме кодов, заданных на группах элементов 8.1-8.п.

После снятия сигнала установки в исходное состояние счетчик 2 начинает подсчет импульсов, поступающих от генератора 1 импульсов. Код с выходов счетчика 2 поступает на входы дещифратора 3, на выходах которого начинают вырабатываться импульсы. Импульс с первого выхода дещифра- 50 тора 3 используется только в первом такте для начальной записи выходных кодов номеров каналов блока 8 в сдвигающие регистры 11. Этот импульс поступает через элемент И 4 на входы 14 регистров 11.1 -11.к сдвига, а далее - на вторые входы элемен22.п, установочные входы 12.1, 12.2-12.п, 55 тов И-НЕ 22.1, 22.2-22.п, на первые входы

информационный вход 13, вход 14 разреще- ния установки, вход 15 сдвига, выходы 16.1, 16.2-16.П разрядов. При этом входы 12.1,

которых поступают сигналы с групп элементов 8.1-8.П коммутации через входы 12.1, 12.2-12.П. С выхода элементов И-НЕ 22.1,

12.2-12.П соединены с первыми входами элементов И-НЕ 22.1, 22.2-22.п соответственно, вход 13 с D-входом триггера 21.1, вход 14 с вторыми входами элементов И-НЕ 22.1,

22.2-22.П, вход 15 с С-входом триггеров 21.1, 22.2-22.П, выходы триггеров 21.1, 21.2-21.п с выходами 16.1, 16.2-16.п соответственно, дополнительно выходы триггеров 21.1, 21.2- 21.п соединены с D-входами триггеров 21.2, 21.3-21.П соответственно. Выходы элементов И-НЕ 22.1, 22.2-22.П соединены с S-BXO- дами триггеров 21.1 21.2-21.п соответственно.

Коммутатор с заданием порядка коммутации работает следующим образом.

В исходном состоянии счетчик 2, регистры 11.1 -11.к сдвига и триггер 19 обнулены. Цепи установки в исходное состояние указанных элементов не показаны. Так как регистры 11.1 -11.к сдвига обнулены, то с выходов 16.П указанных регистров на входы дешифратора 6 поступают сигналы логического нуля. Вследствие этого на нулевом выходе

шифратора 6 поступают сигналы логического нуля. Вследствие этого на нулевом выходе

тора связаны соотношением -1. Нуле- вой код не используется для кодирования

дешифратора 6 будет сигнал логической единицы, который через элемент 5 задержки поступает на второй вход элемента И 4 и подготавливает его к открыванию. С блока 8 управления задается очередность коммутации выходных каналов (выходов) 20.1-20.п коммутатора. Каждая группа элементов 8.1-8.П, состоящая из К элементов коммутации, задает код коммутируемого канала, а последовательность группы 8.1-8.п задает последовательность коммутации выходных каналов. Количество элементов коммутации К в группах элементов 8.1-8.п, количество групп элементов п в блоке 8 управления, количество выходных каналов п коммутакодов с помощью элементов групп 8.1-8.п

обеспечивает возможность ко.ммутации выходных каналов с любой очередностью. С по- мощью группы элементов 8.s задается конт

рольная сумма кодов коммутируемых каналов, которая равна сумме кодов, заданных на группах элементов 8.1-8.п.

После снятия сигнала установки в исходное состояние счетчик 2 начинает подсчет импульсов, поступающих от генератора 1 импульсов. Код с выходов счетчика 2 поступает на входы дещифратора 3, на выходах которого начинают вырабатываться импульсы. Импульс с первого выхода дещифра- тора 3 используется только в первом такте для начальной записи выходных кодов номеров каналов блока 8 в сдвигающие регистры 11. Этот импульс поступает через элемент И 4 на входы 14 регистров 11.1 -11.к сдвига, а далее - на вторые входы элементов И-НЕ 22.1, 22.2-22.п, на первые входы

которых поступают сигналы с групп элементов 8.1-8.П коммутации через входы 12.1, 12.2-12.П. С выхода элементов И-НЕ 22.1,

22.2-22.П происходит запись информации сигналом по S-входу в триггеры 21.1-21.п. Каждая совокупность одноименных разрядов 17.1 - 17.1 (триггеры 21.1 -21.1, элементы И 22.1-22.1), 17.2-17.2 (триггеры 21.2- 21.2, элементы И 22.2-22.2),...,17.n-17.n (триггеры 21.п-21.п), элементы И 22.п- И 22.п (сдвигающих регистров 11.1 - 11.к образуют регистр параллельного кода, который хранит код номера канала, а размещение этих кодов в разрядах 17.1 - 17.п соответствует заданной очередности их коммутации. При этом в последних разрядах 17.п размещается код канала, который коммутируется первым, в предпоследних разрядах 17.П-1 - код канала, который коммутируется вторым и т. д., в первых разрядах 17.1 - код канала, который коммутируется последним.

Как только в разряды 17.п запишется код, на нулевом выходе дешифратора 6 появится нулевой сигнал, который через элемент 5 задержки поступит на второй вход элемента И 4 и закроет его. Элемент задержки обеспечивает уверенную запись кодов коммутируемых каналов в разряды 17.1 - 17.п регистров 11.1 -11.к сдвига.

При этом в устройстве выполняются следующие операции. На сумматоре 10 вычисляется сумма чисел, установленных в разрядах 17.1 - 17.П регистров 11.1 - 11.к сдвига и подается на первые входы схемы 9 сравнения, которая сравнивает ее с контрольной суммой, заданной группой элементов 8.S блока 8 управления. При равенстве этих сумм вырабатывается сигнал логического нуля, при неравенстве сигнал логической единицы и с выхода схемы 9 сравнения поступает на элемент И 18. Импульс с второго выхода дешифратора 3 управляет передачей результатов сравнения через элемент И 18 в триггер 19. При равенстве сумм сохраняется нулевое состояние триггера 19 и сигнал логической единицы с его инверсного выхода поступает на первые входы элементов 7.1-7.п. При неравенстве сумм триггер 19 устанавливается в единичное состояние и сигнал логического нуля с его инверсного выхода поступает на первые входы элементов 7.1-7.п, запрещая коммутацию выходных каналов. Выходной код с разрядов 17.П сдвигающих регистров 11.1 -11.к поступает на дешифратор бив зависимости от значения кода на одном из выходов дешифратора 6 вырабатывается сигнал логической единицы, который поступает на второй вход соответствующего элемента И блока 7. В случае равенства сумм на входах схемы 9 сравнения импульс с третьего выхода дешифратора 3 поступает на третьи входы элементов И блока 7, открывает один из элементов, на котором присутствует сигнал логической единицы с выхода дешифратора 6, и на одном из выходов 20.1-20.п вы0

рабатывается коммутирующий сигнал. Номер выходного канала, на котором вырабатывается сигнал, соответствует . заданному группой элементов В.п блока 8. Импульс с четвертого выхода дешифратора 3 производит сдвиг информации в регистрах 11.1 - U.K. В разрядах 17.п регистров 11.1 -11.к окажется код, заданный группой элементов 8.П-1 блока 8. Под управлением импульсов с выходов дешифратора 3 вырабатывается коммутирующий сигнал логической единицы на одном из выходных каналов, заданном группой элементов 8.П-1 блока 8, и выпOv няeтcя сдвиг инфор.мации в регистрах 11.1 - 11.К. Аналогичным образом последовательно на выходных каналах устройства вырабатывается сигнал, причем номера выходных каналов 20.i соответствуют кодам, заданным группами эле.ментов 8.п-2-8.1 блока 8. Затем устройство циклически вырабатывает выходные сигналы в каналах 20.1 - 0 20.п в соответствии с кодами, заданными группами элементов 8.п-8.1 блока 8. Упрощение устройства заключается в уменьшении общего количества элементов и связей.

5

5

0

5

0

5

0

5

Формула изобретения

Коммутатор с задание.м порядка коммутации, содержащий генератор импульсов, счетчик, первый и второй дешифраторы, первый и второй элементы И, блок элементов И, блок управления, схему сравнения, сумматор, К регистров сдвига, триггер,выход генератора импульсов соединен с входом счетчика, выходы которого подключены к входу первого дешифратора, первый выход которого соединен с первы.м входом первого элемента И, второй выход первого дешифратора соединен с первым входом второго элемента И, выход которого соединен с входом триггера, выход которого подключен к первым входам элементов И блока элементов И, вторые входы которых соединены с соответствующими выходами,начиная с первого, второго дешифратора, каждый вход которого соединен с выходом последнего разряда соответствующего регистра сдвига, соответствующий выход группы выходов б,тока управления соединен с установочным входом соответствующего разряда регистров сдвига, выходы одноименных разрядов регистров сдвига соединены с соответствующими группами входов сумматора, выход схемы сравнения соединен с вторым входом второго элемента И, третий выход первого дешифратора соединен с третьими входами элементов И блока элементов И, выходы которых являются выходами коммутатора, четвертый выход первого дешифратора соединен с входом сдвига каждого регистра сдвига, отличающийся тем, что, с целью упрощения устройства, в него введен элемент задержки, вход которого соединен с нулевым выходом второго дешифратора, а выход подключен к второму входу первого элемента И, выход которого соединен с входом разрешения установки каждого регистра сдвига, прямой выход последнего разряда каждого регистра сдвига соединен с информационным входом первого разряда того же регистра сдвига, выходы сумматора соединены с первыми входами схемы сравнения, вторые входы которой соединены с контрольным выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Многоканальная стабилизирующая система электропитания | 1987 |

|

SU1436111A1 |

| Устройство для цифровой обработки сигналов | 1989 |

|

SU1652981A1 |

| Устройство ввода-вывода | 2020 |

|

RU2753980C1 |

| Многоканальный коммутатор | 1989 |

|

SU1661986A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1989 |

|

SU1619299A1 |

| Устройство приоритетных прерываний | 1990 |

|

SU1741134A1 |

| Многоканальная микропрограммная управляющая система | 1985 |

|

SU1280628A1 |

| Коммутатор | 1984 |

|

SU1175023A1 |

| ОБНАРУЖИТЕЛЬ КОМБИНАЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1996 |

|

RU2096822C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах для программного управления и коммутации каналов. Цель изобретения - упрощение устройства. Устройство содержит генератор 1 импульсов, счетчик 2, два дешифратора 3 и 6, два элемента И 4 и 18, блок 7 элементов И с элементами И 7.1-7.п, блок 8 управления с группами элементов коммутации 8.1-8.п и 8.S, схему 9 сравнения, сумматор 10, К регистров 11.1 - И.к сдвига с разрядами 17.1 - 17.П, триггер 19. В устройство введен элемент 5 задержки. На чертеже также показаны установочные входы 12.1 -12.к, информационные входы 13, вход 14 разрешения установки, входы 15 сдвига и выходы 16.1 - 16.п регистров сдвига, выходы 20.1-20.п устройства. Упрощение устройства заключается в уменьшении общего количества элементов и связей. 2 ил. SS (Л со СО 1чЭ 05 00 ФигЛ L 1 20. п.20.1

| Коммутатор каналов с переменным циклом работы | 1977 |

|

SU664294A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Коммутатор | 1981 |

|

SU1018244A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-06-23—Публикация

1986-01-30—Подача