Изобретение относится к телефонной связи и может быть использовано для контроля коммутационных матриц телефонных станций.

Цель изобретения - уменьшение времени контроля.

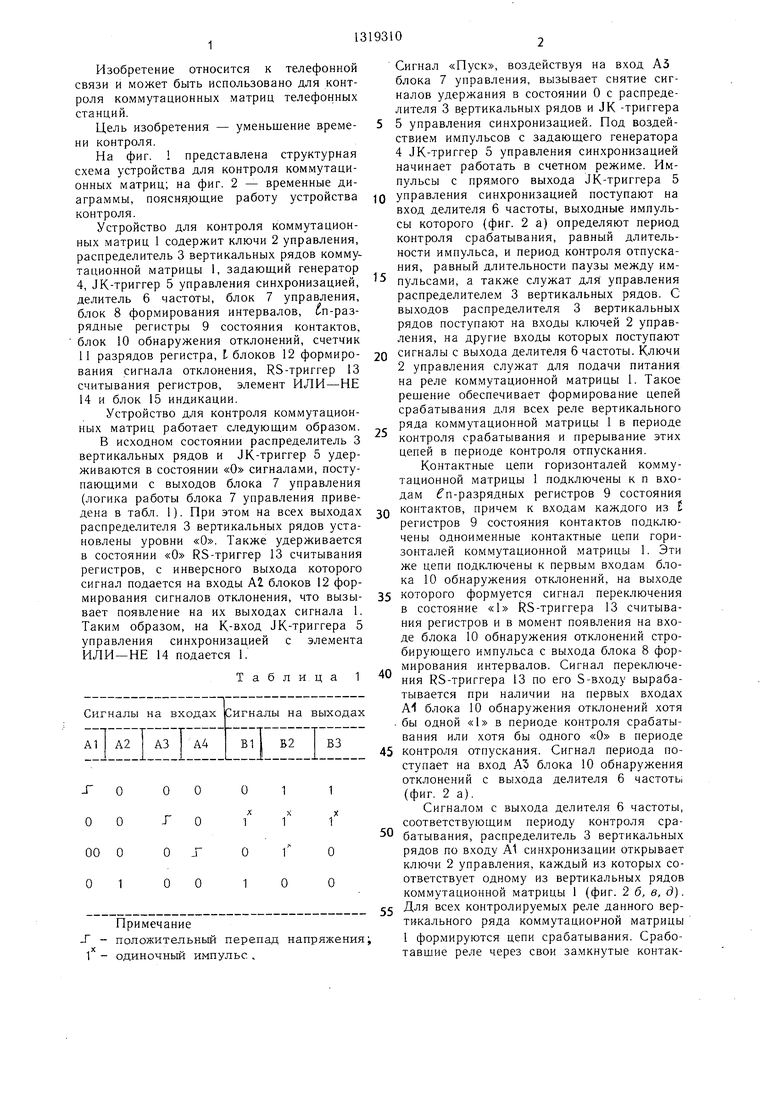

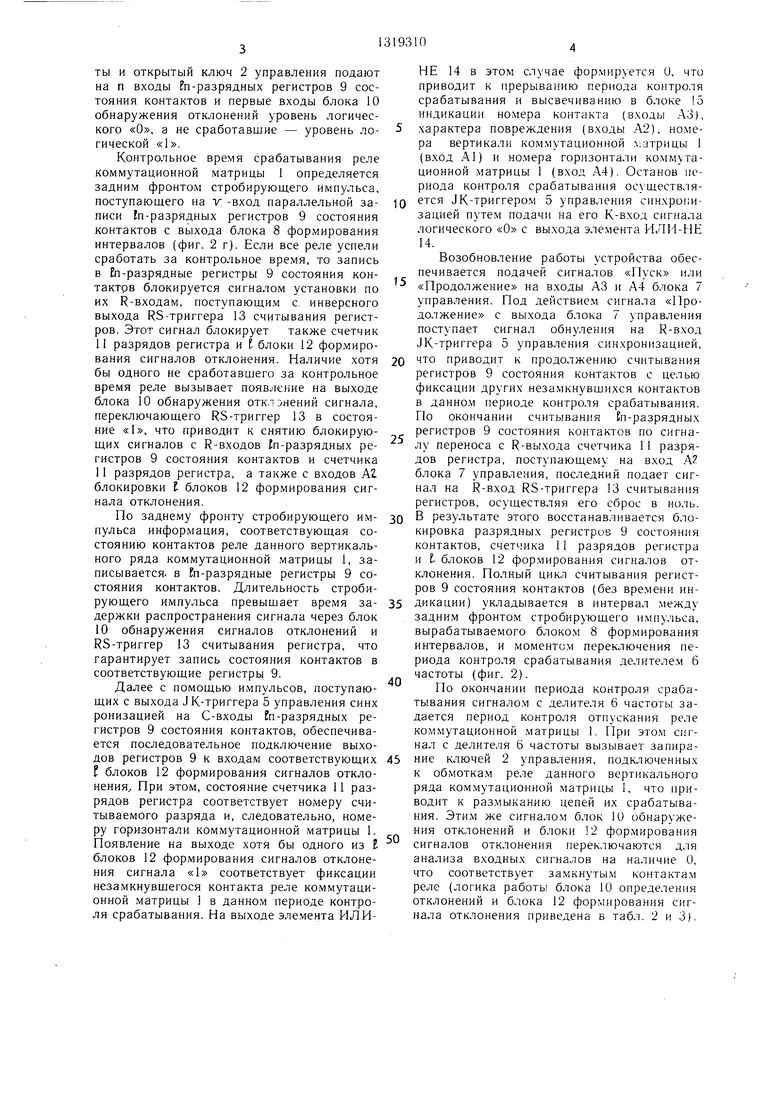

На фиг. представлена структурная схема устройства для контроля коммутационных матриц; на фиг. 2 временные диаграммы, поясняющие работу устройства контроля.

Устройство для контроля коммутационных матриц 1 содержит ключи 2 управления, распределитель 3 вертикальных рядов коммутационной матрицы 1, задающий генератор 4, JK-триггер 5 управления синхронизацией, делитель 6 частоты, блок 7 управления, блок 8 формирования интервалов, п-раз- рядные регистры 9 состояния контактов, блок 10 обнаружения отклонений, счетчик II разрядов регистра, L блоков 12 формирования сигнала отклонения, RS-триггер 13 считывания регистров, элемент ИЛИ-НЕ 14 и блок 15 индикации.

Устройство для контроля коммутационных матриц работает следующим образом.

В исходном состоянии распределитель 3 вертикальных рядов и JK-триггер 5 удерживаются в состоянии «О сигналами, поступающими с выходов блока 7 управления (логика работы блока 7 управления приведена в табл. 1). При этом на всех выходах распределителя 3 вертикальных рядов установлены уровни «О. Также удерживается в состоянии «О RS-триггер 13 считывания регистров, с инверсного выхода которого сигнал подается на входы А2 блоков 12 формирования сигналов отклонения, что вызывает появление на их выходах сигнала 1. Таким образом, на К-вход JK-триггера 5 управления синхронизацией с элемента ИЛИ-НЕ 14 подается 1.

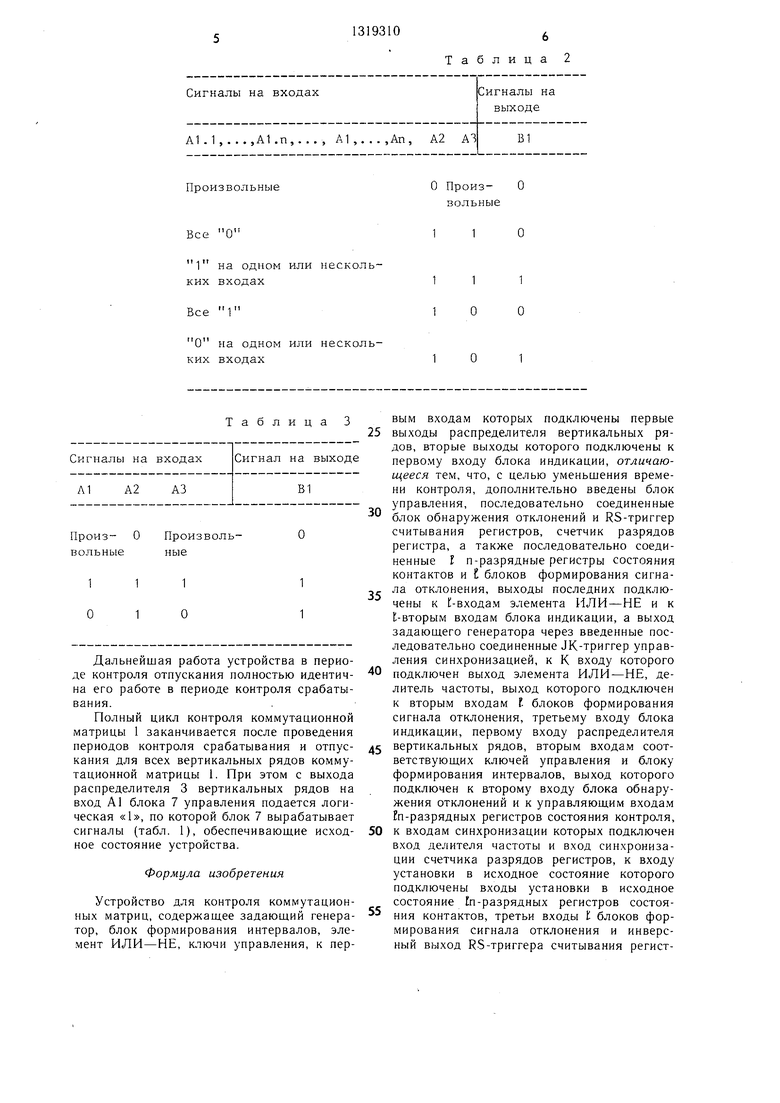

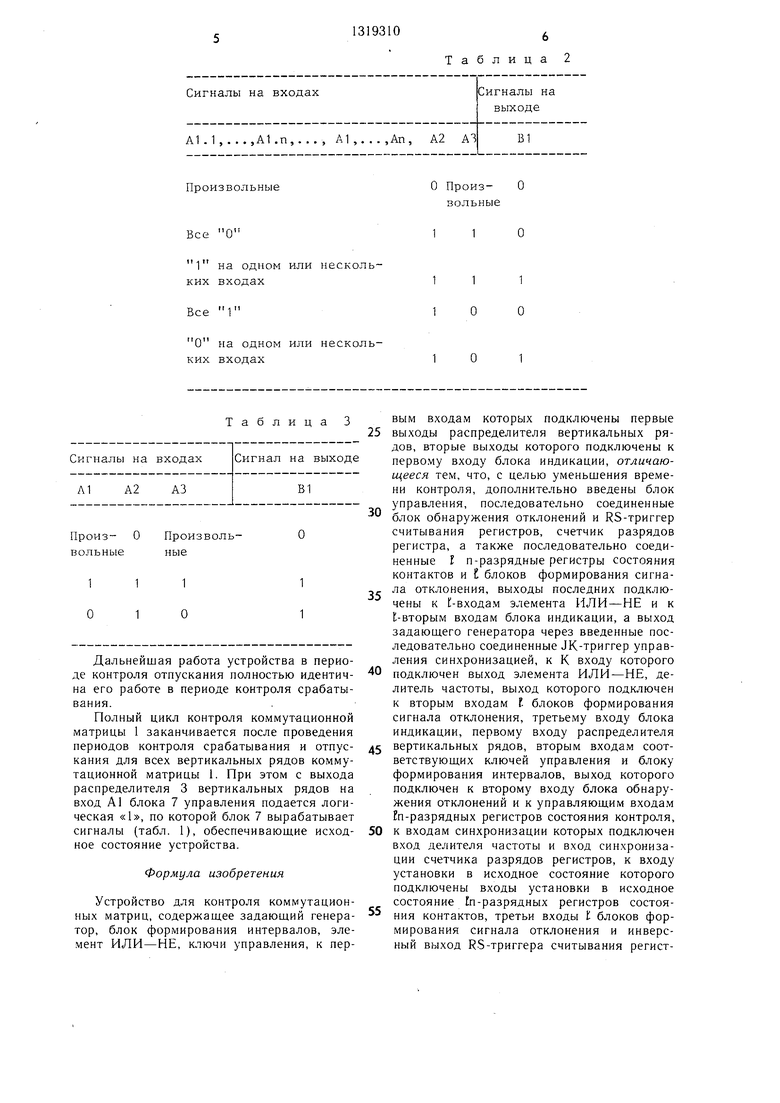

Таблица 1

Примечание

-Г - положительный перепад напряжения; 1 - одиночный импульс,

0

5

0

0

5

Сигнал «Пуск, воздействуя на вход A3 блока 7 управления, вызывает снятие сигналов удержания в состоянии О с распределителя 3 вертикальных рядов и JK -триггера 5 управления синхронизацией. Под воздействием импульсов с задающего генератора 4 JK-триггер 5 управления синхронизацией начинает работать в счетном режиме. Импульсы с прямого выхода JK-триггера 5 управления синхронизацией поступают на вход делителя 6 частоты, выходные импульсы которого (фиг. 2 а) определяют период контроля срабатывания, равный длительности импульса, и период контроля отпускания, равный длительности паузы между импульсами, а также служат для управления распределителем 3 вертикальных рядов. С выходов распределителя 3 вертикальных рядов поступают на входы ключей 2 управления, на другие входы которых поступают сигналы с выхода делителя 6 частоты. Ключи 2 управления служат для подачи питания на реле коммутационной матрицы 1. Такое рещение обеспечивает формирование цепей срабатывания для всех реле вертикального ряда коммутационной матрицы 1 в периоде контроля срабатывания и прерывание этих цепей в периоде контроля отпускания.

Контактные цепи горизонталей коммутационной матрицы 1 подключены к п входам п-разрядных регистров 9 состояния

Q контактов, причем к входам каждого из t регистров 9 состояния контактов подключены одноименные контактные цепи горизонталей коммутационной матрицы 1. Эти же цепи подключены к первым входам блока 10 обнаружения отклонений, на выходе которого формуется сигнал переключения в состояние «1 RS-триггера 13 считывания регистров и в момент появления на входе блока 10 обнаружения отклонений стро- бирующего импульса с выхода блока 8 формирования интервалов. Сигнал переключения RS-триггера 13 по его S-входу вырабатывается при наличии на первых входах А1 блока 10 обнаружения отклонений хотя . бы одной «1 в периоде контроля срабатывания или хотя бы одного «О в периоде

5 контроля отпускания. Сигнал периода поступает на вход АЪ блока 10 обнаружения отклонений с выхода делителя 6 частоты (фиг. 2 а).

Сигналом с выхода делителя 6 частоты, соответствующим периоду контроля батывания, распределитель 3 вертикальных рядов по входу А1 синхронизации открывает ключи 2 управления, каждый из которых соответствует одному из вертикальных рядов коммутационной матрицы 1 (фиг. 2 б, в, д). Для всех контролируемых реле данного вертикального ряда коммутационной матрицы 1 формируются цепи срабатывания. Сработавшие реле через свои замкнутые контак5

5

ты и открытый ключ 2 управления подают на п входы fn-разрядных регистров 9 состояния контактов и первые входы блока 10 обнаружения отклонений уровень логического «О, а не сработавшие - уровень ло- гической «1.

Контрольное время срабатывания реле коммутационной матрицы 1 определяется задним фронтом стробирующего импульса, поступающего на v -вход параллельной за- писи Еп-разрядных регистров 9 состояния контактов с выхода блока 8 формирования интервалов (фиг. 2 г). Если все реле успели сработать за контрольное время, то запись в Еп-разрядные регистры 9 состояния кон- тактрв блокируется сигналом установки по их R-входам, поступающим с. инверсного выхода RS-триггера 13 считывания регистров. Этот сигнал блокирует также счетчик 11 разрядов регистра и блоки 12 формирования сигналов отклонения. Наличие хотя бы одного не сработавшего за контрольное время реле вызывает появление на выходе блока 10 обнаружения отклонений сигнала, переключающего RS-триггер 13 в состояние «1, что приводит к снятию блокирующих сигналов с R-входов 1п-разрядных регистров 9 состояния контактов и счетчика 11 разрядов регистра, а также с входов AZ блокировки I блоков 12 формирования сигнала отклонения.

По заднему фронту стробирующего им- пульса информация, соответствующая состоянию контактов реле данного вертикального ряда коммутационной матрицы 1, записывается, в Кп-разрядные регистры 9 состояния контактов. Длительность стробирующего импульса превышает время за- держки распространения сигнала через блок 10 обнаружения сигналов отклонений и RS-триггер 13 считывания регистра, что гарантирует запись состояния контактов в соответствующие регистры 9.

Далее с помощью импульсов, поступающих с выхода JK-триггера 5 управления синх ронизацией на С-входы Еп-разрядных регистров 9 состояния контактов, обеспечивается последовательное подключение выходов регистров 9 к входам соответствующих f блоков 12 формирования сигналов отклонения,. При этом, состояние счетчика 11 разрядов регистра соответствует номеру считываемого разряда и, следовательно, номеру горизонтали коммутационной матрицы 1. Появление на выходе хотя бы одного из Е блоков 12 формирования сигналов отклонения сигнала «1 соответствует фиксации незамкнувщегося контакта реле коммутационной матрицы 1 в данном периоде контроля срабатывания. На выходе элемента ИЛИНЕ 14 в этом случае формируется О, что приводит к прерыванию периода контроля срабатывания и высвечиванию в блоке 15 индикации номера контакта (входы A3), характера повреждения (входы А2), номера вертикали ком.мутационной матрицы 1 (вход А1) и номера горизонтали коммутационной матрицы 1 (вход А4). Останов периода контроля срабатывания осуществляется JK-триггером 5 управления синхронизацией путем подачи на его К-вход сигнала логического «О с выхода элемента ИЛИ-НЕ 14.

Возобновление работы устройства обеспечивается подачей сигналов «Пуск или «Продолжение на входы A3 и А4 блока 7 управления. Под действие.м сигнала «Продолжение с выхода блока 7 управления поступает сигнал обнуления на R-вход JK-триггера 5 управления синхронизацией, что приводит к продолжению считывания регистров 9 состояния контактов с целью фиксации других незамкнувшихся контактов в данном периоде контроля срабатывания. По окончании считывания Сп-разрядных регистров 9 состояния контактов по сигналу переноса с R-выхода счетчика 11 разрядов регистра, поступающему на вход А2 блока 7 управления, последний подает сигнал на R-вход RS-триггера 13 считывания регистров, осуществляя его сброс в ноль. В результате этого восстанавливается блокировка разрядных регистров 9 состояния контактов, счетчика 11 разрядов регистра и I блоков 12 фор.мирования сигналов отклонения. Полный цикл считывания регистров 9 состояния контактов (без вре.мени индикации) укладывается в интервал .между задним фронтом стробирующего импульса, вырабатываемого блоком 8 формирования интервалов, и моментом переключения периода контроля срабатывания делителем 6 частоты (фиг. 2).

По окончании периода контроля срабатывания сигналом с делителя 6 частоты задается период контроля отпускания реле коммутационной .матрицы 1. При это.м cjir- нал с делителя 6 частоты вызывает запирание ключей 2 управления, подключенных к обмоткам реле данного вертикального ряда ком.мутационной матрицы 1, что приводит к размыканию цепей их срабатывания. Этим же сигналом блок 10 обнаружения отклонений и блоки 2 формирования сигналов отклонения переключаются для анализа входных сигналов на наличие О, что соответствует замкнутым контактам реле (логика работы блока 10 определения отклонений и блока 12 формирования сигнала отклонения приведена Б табл. 2 и 3).

Произвольные

О

на одном или нескольвходах

1

на одном или нескольвходах

Таблица 3

1 О

Дальнейшая работа устройства в периоде контроля отпускания полностью идентична его работе в периоде контроля срабатывания.

Полный цикл контроля коммутационной матрицы 1 заканчивается после проведения периодов контроля срабатывания и отпускания для всех вертикальных рядов коммутационной матрицы 1. При этом с выхода распределителя 3 вертикальных рядов на вход А1 блока 7 управления подается логическая «1, по которой блок 7 вырабатывает сигналы (табл. 1), обеспечивающие исходное состояние устройства.

Формула изобретения

Устройство для контроля коммутационных матриц, содержащее задающий генератор, блок формирования интервалов, элемент ИЛИ-НЕ, ключи управления, к перТаблица 2

О Произ- О вольные

11О

111

1ОО

1О1

5

0

5

0

5

0

5

вым входам которых подключены первые выходы распределителя вертикальных рядов, вторые выходы которого подключены к перво.му входу блока индикации, отличающееся тем, что, с целью уменьшения времени контроля, дополнительно введены блок управления, последовательно соединенные блок обнаружения отклонений и RS-триггер считывания регистров, счетчик разрядов регистра, а также последовательно соединенные I п-разрядные регистры состояния контактов и С блоков формирования сигнала отклонения, выходы последних подключены к t-входам элемента ИЛИ-НЕ и к 1-вторым входам блока индикации, а выход задающего генератора через введенные последовательно соединенные JK-триггер управления синхронизацией, к К входу которого подключен выход элемента ИЛИ-НЕ, делитель частоты, выход которого подключен к вторым входам I блоков формирования сигнала отклонения, третьему входу блока индикации, первому входу распределителя вертикальных рядов, вторым входам соответствующих ключей управления и блоку формирования интервалов, выход которого подключен к второму входу блока обнаружения отклонений и к управляющим входам Еп-разрядных регистров состояния контроля, к входам синхронизации которых подключен вход делителя частоты и вход синхронизации счетчика разрядов регистров, к входу установки в исходное состояние которого подключены входы установки в исходное состояние tn-разрядных регистров состояния контактов, третьи входы I блоков формирования сигнала отклонения и инверсный выход R.S-триггера считывания регистров, к входу установки в нуль которого, к входу установки в нуль JK-триггера управления синхронизацией, второму входу распределителя вертикальных рядов подключены соответственно первый, второй и третий выходы блока управления, к первому входу которого подключен третий выход распределителя вертикальных рядов, а к

/71

г 2

т. 1 2

П П П П П

Фиг. 2

второму входу блока управления - выход переноса счетчика разрядов регистров, К выходов которого подключены к четвертым входам блока индикации, при этом п входов 1п-разрядных регистров состояния контактов и блока обнаружения отклонений являются входами nxt горизонтальных шин коммутационной матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1982 |

|

SU1184105A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1354437A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Устройство для контроля модулей коммутации | 1986 |

|

SU1392633A1 |

| Многодвигательный электропривод переменного тока | 1985 |

|

SU1307521A1 |

| Коммутационное устройство | 1985 |

|

SU1251095A1 |

| Система телемеханики с временным разделением каналов для электрической централизации стрелок и сигналов | 1985 |

|

SU1345362A1 |

| УСТРОЙСТВО ДЛЯ ВИЗУАЛЬНОГО КОНТРОЛЯ ИСПОЛНЕНИЯ ПРОГРАММ | 1991 |

|

RU2012044C1 |

Изобретение относится к телефонной связи и уменьшает время контроля. Устр-во для контроля коммутационных матриц (КМ) 1 содержит ключи 2 управления, распределитель 3 вертикальных рядов КН 1, задающий г-р 4, УК-триггер 5 управления синхро1 т низацией, делитель 6 частоты, блок 7 управления, блок 8 формирования интервалов, t п-разрядные регистры 9 состояния контактов, блок 10 обнаружения отклонений, счетчик 11 разрядов регистра, 1 блоков 12 формирования сигнала отклонения, RS-триг- гер 13 считывания регистров, эл-т ИЛИ-НЕ 14, блок 15 индикации. Полный цикл контроля КМ 1 заканчивается гцэсле проведения периодов контроля срабатывания и отпускания для всех вертикальных рядов КМ 1. При этом с выхода распределителя 3 на вход А1 блока 7 подается логич. «1, по которой блок 7 вырабатывает сигналы, обеспечивающие исходное состояние устр-ва. 3 табл. 2 ил. (Л оо со со

| Колганов В | |||

| А | |||

| и др | |||

| М жтаж и наладка комплексов электросвязи | |||

| М., вып 2/10, 1980, с | |||

| Выбрасывающий ячеистый аппарат для рядовых сеялок | 1922 |

|

SU21A1 |

Авторы

Даты

1987-06-23—Публикация

1986-02-04—Подача