Изобретение относится к радиотехнике и может использоваться в асинхронных адресных системах связи.

Цель изобретения - увеличение объема ансамбля передаваемых сигналов.

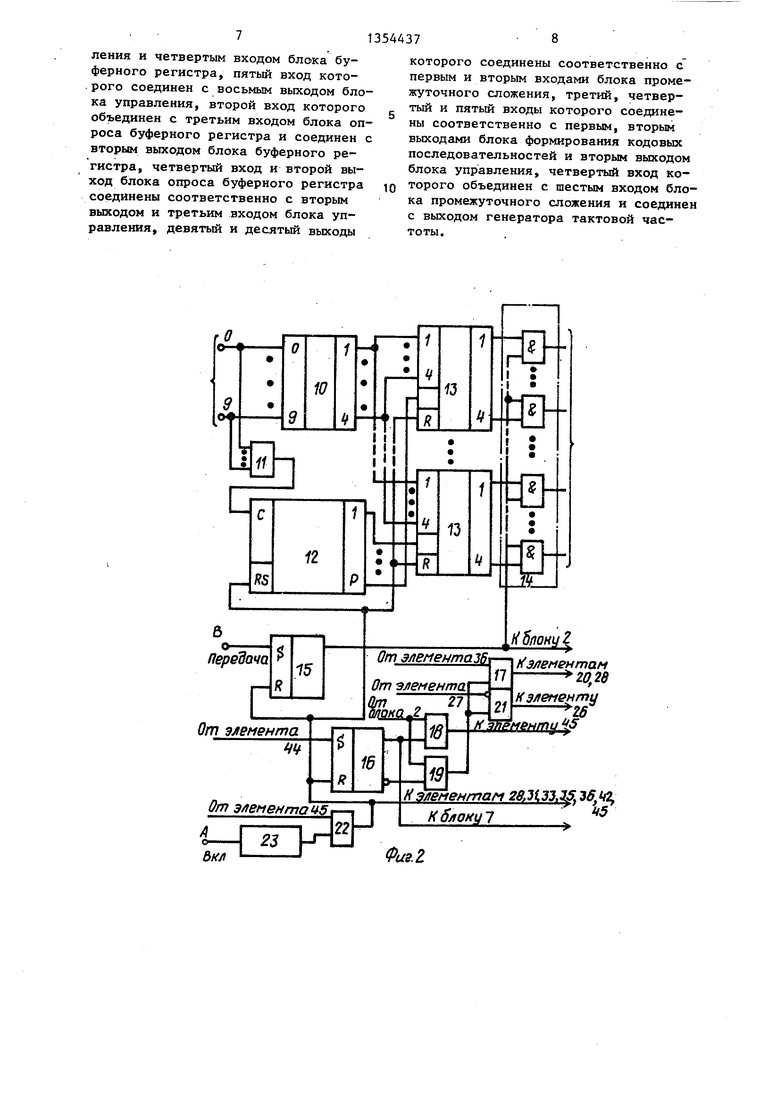

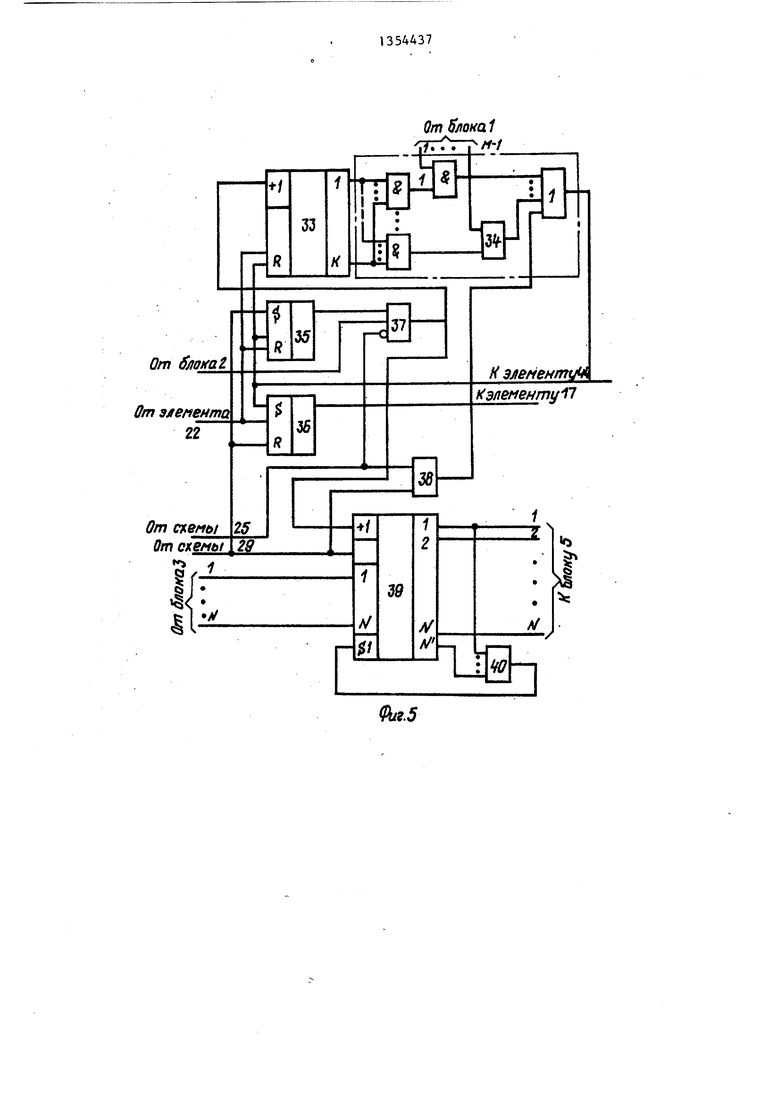

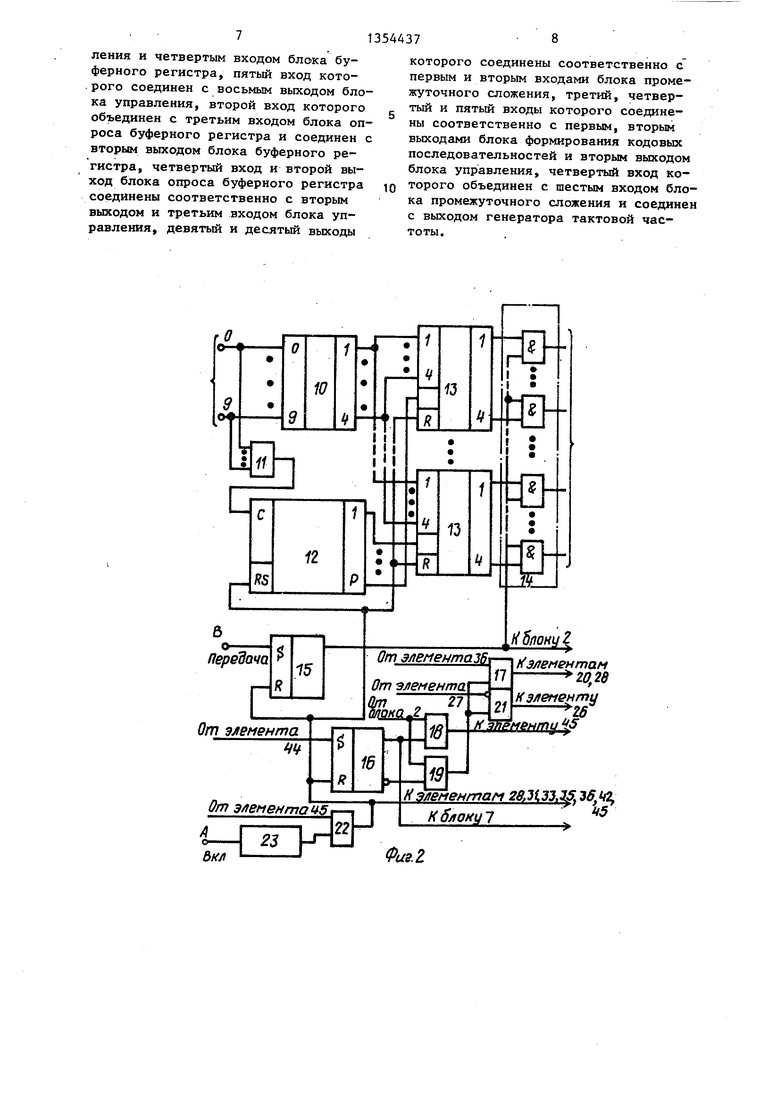

На фиг. 1 изображена структурная , электрическая схема предложенного устройства; на фиг.2 и 3 - схема блока управления; на фиг.4 - схема блока формирования кодовых последовательностей; на фиг.5 - схема блока промежуточного сложения; на фиг.6 - схема блока буферного регистра; на фиг.7 - схема блока опроса буферного регистра.

Устройство содержит блок 1 управления, генератор 2 тактовой частоты, блок 3 формирования кодовых последовательностей, блок 4 промежуточного сложения, блок 5 буферного регистра, блок 6 опроса буферного регистра,генератор 7 сетки частот, цифровой коммутатор 8, усилитель 9 мощности.

Блок 1 управления состоит из шифратора 10, элемента ИЛИ 11, распределителя 12, регистров 13,.блока 4 считывания адреса, RS-триггеров 15 . и 16 управления, элементов И 17-21, элемента ИЛИ 22, дифференциального блока 23, дешифратора 24, блока 25 преобразования, вычитающего счетчика 26 и элемента И 27.

Блок 3 формирования кодовых последовательностей состоит из счетчика 28, блока 29 настройки, регистра 30, распределителя 31 и блока 32 считывания кода.

Блок 4 промежуточного сложения состоит из счетчика 33, блока 34 настройки, RS-триггеров 35 и 36 управления, элементов И 37 и 38, счетчика 39 и элемента И 40.

Блок 5 буферного регистра состоит из регистра .41, распределителя 42, блока реле 43 и элемента И 44.

Блок 6 onpoda- буферного регистра состоит из регистра 43 и блока 46 опроса.

Устройство работает следующим об разом.

При включении (на блоке 1 управления нажата кнопка Вкл) на клемме А

появляется сигнал, который через диф- gg торое в параллельном коде через . ференциальный блок 23 и элемент И 22 блок 14 считывания адреса подается приводит все блоки устройства в ис- на вход дешифратора 24 блока 1. Де- кодное состояние. Импульс начальной шифратор 24 имеет М групп выходов

установки подается на R,S-вход расЬ

10

15

20

25

30

35

40

45

50

пределителя 12, на R-входы регистра 13, RS триггеров 15 и 16 .управления блока 1 управления, R-Sxoд счетчика 28, R,S-вxoд распределителя 31 блока 3 формирования кодовых последовательностей, на R-вход RS-тригге- ра 35 управления, S-вход RS-триггера 36 управления и R-вкод счетчика 33 блока 4 промежуточного сложения, на R,S-вход распределителя 42 блока 5 буферного регистра, а также на R- вход регистра 45 блока 6 опроса буферного регистра.

Установка распределителей 12 и 31 в исходное состояние означает, что поступающий на С-вход распределителя импульс после его установки в исходное состояние попадает в первый канал.

Установка распределителя 42 в исходное состояние предполагает наличие положительного уровня напряжения на выходе первого канала после прихода на С-вход первого импульса.

После включения питания на блоке 1 управления набирается номер передаваемого сигнала (нажимаются цифровые кнопочные выключатели от О до 9, подающие питание на С-клеммы). Номер передаваемого сигнала имеет от 1 доР цифр. При наборе первой цифры в течение времени нажатия кнопки на одной из клемм появляется сигнал. Сигнал через элемент ИЛИ 11 поступает на С-вход распределителя 12, который распределяет его в первый канал и подает на вход EWR регистра 13. Шифратор 10, преобразующий десятичный код в двоичный, при наличии сигнала на входе EWR, подает двоичный код первой цифры абонента в первый регистр 13. При наборе второй цифры процедура повторяется, но двоичный код цифры будет записан уже во второй регистр 13 и т.д.

После набора сигнала на блоке 1 нажимается кнопка Передача, на клемме В появляется сигнал, который переводит триггер 15 в единичное состояние, что приводит к запуску генератора 2 тактовой частоты и считыванию содержимого регистров 13, копо М-1 выходу в каждой группе, появ,31354437

лениесигнала на одном из выходов дешифратора 24 соответствует строго определенному номеру сигнала в композиционной системе. Сигнал с выхода дешифратора 24 подается на блок 25 преобразования, который одновременно определяет, к какой из оптимальных

систем, образующих композиционную.

мирование структуры первого сигнала алгоритма (1), если сигнал имеется на первом входе второго элемента И, то К 2 (происходит формирование второго сигнала алгоритма (1) и т.д. Число KB (1) соответствует числу импульсов, поступающих с выхода блока 29 настройки на вход блока 32 считы- 1Q вания кода, i-номера выходов N-pas- рядных ячеек регистра 30, которые связаны с элементами И блока считывания кода 32, на двух оставшихся входах которых имеется сигнал при 3 и устанавливает коэффициент сче-15 поступлении очередного тактового

импульса на счетный вход счетчика 28 и С-вход распределителя 31. Сигнал с выхода блока 29 настройки поступает также в блок 4 промежуточного сложеSo относится номер набранного сигнала и какое место этот сигнал занимает в самой оптимальной системе. При этом сигнал о месте в системе подается на вход блока 29 настройки блока

та счетчиков 28., а таюке через дифференциальные блоки (формирующие импульсы положительной полярности по переднему фронту сигнала) подается на вход установки в состояние S (М-2) счетчика 26.

Сигнал о номере оптимальной системы с выхода элементов ИЛИ блока 25 преобразования поступает в блок 4 промежуточного сложения.

На первом этапе формирование частотной структуры сигнала производится в соответствии с алгоритмом о.-(К) ),(j) (1), для чего в устройстве синхронизирована работа счетчика 28 и распределителя 31 блока 3 формирования кодовых последовательностей. Синхронизация достигается тем, что счетчик 26 блокирует прохождение тактовых импульсов через элемент И 20 блока 1 до тех пор, пока его состояние не будет соответствовать состоянию S , при достижении которого на выходе элемента И 27 появится сигнал, который заблокирует прохождение импульсов через элемент И 21 и обеспечит прохождение тактовых импульсов через элемент И 20 блока 1. С выхода элемента И 20 тактовые импульсы поступают на вход распределителя 31. Одновременно тактовые импульсы через. элемент И 17 блока 1 подаются на счетный вход счетчика 28 блока 3.

Счетчик 28 и распределитель 31 блока 3 формирования кодовых после- доват ельностей обеспечивают считывание содержимого ячеек регистра 30, сообразуясь с алгоритмом (1). При этом счетчик 28 совместно с блоком 29 настройки задает номер сигнала j b (1), причем если сигнал имеет место на первом входе элемента И блока 29 настройки, коэффициент счета счетчика 28 равен 1 и происходит фор20

25

30

35

ния, на вход EWR счетчика 39, разрешающего запись содержимого, считываемой N-разрядной ячейки регистра 30 блока 3 в параллельном коде в счетчике 39, на S-йход RS-триггера 35 управления и на R-вход RS-триггера 36 управления, а также на С-вход распре- делителя 42 блока 5. RS-триггер 35 управления переходит в единичное состояние и разрешает прохождение тактовых импульсов через элемент И 37,при отсутствии сигнала с выхода первой М-1 входовой схемы ИЛИ блока 25 преобразования (сигнал на входе этой схемы соответствует тому, что номер формируемого сигнала не превосходит М-1 сигнала первой оптимальной системы, т.е. Ср 0). Тактовые импульсы с выхода элемента И 37 подаются на счетные входы счетчиков 33 и 39.

40

45

50

55

Счетчик 33 совместно с блоком 34 настройки представляет собой счетчик с перенастраиваемым коэффициентом счета. Коэффициент счета счетчика 33 соответствует в процедуре формирования композиционной системы коэффициенту Cjj и меняется от 1 до М-1. Содержимое счетчика 39 при поступлении тактовых импульсов с элемента И 37 увеличивается на величину счетчика 39 и как только на выходе блока 34 настройки появляется сигнал, он вновь устанавливает триггер 36 управления в единичное, а триггер 35 - в нулевое состояние, производят тем самым разблокировку прохождения импульсов через элемент И 17 и блокировку прохождения импульсов через элемент И 37.

ния, на вход EWR счетчика 39, разрешающего запись содержимого, считываемой N-разрядной ячейки регистра 30 блока 3 в параллельном коде в счетчике 39, на S-йход RS-триггера 35 управления и на R-вход RS-триггера 36 управления, а также на С-вход распре- делителя 42 блока 5. RS-триггер 35 управления переходит в единичное состояние и разрешает прохождение тактовых импульсов через элемент И 37,при отсутствии сигнала с выхода первой М-1 входовой схемы ИЛИ блока 25 преобразования (сигнал на входе этой схемы соответствует тому, что номер формируемого сигнала не превосходит М-1 сигнала первой оптимальной системы, т.е. Ср 0). Тактовые импульсы с выхода элемента И 37 подаются на счетные входы счетчиков 33 и 39.

Счетчик 33 совместно с блоком 34 настройки представляет собой счетчик с перенастраиваемым коэффициентом счета. Коэффициент счета счетчика 33 соответствует в процедуре формироваия композиционной системы коэффициенту Cjj и меняется от 1 до М-1. Соержимое счетчика 39 при поступлении тактовых импульсов с элемента И 37 увеличивается на величину счетчика 39 и как только на выходе блока 34 настройки появляется сигнал, он вновь устанавливает триггер 36 управления в единичное, а триггер 35 - в нулевое состояние, производят тем самым разблокировку прохождения импульсов через элемент И 17 и блокировку прохождения импульсов через элемент И 37.

Причем прибавление тактовых импульсов с выхода элемента И 37 к содержимому счетчика 39 (их число равно К(..ц счетчика 33) производится по модулю М. Данную операцию осуществляет элемент И 40 блока 4 промежуточного сложения, на выходе которого возникает сигнал (когда содержимое счетчика 39 равно M+l), который устанавливает счетчик 33 в единичное состояние (по входу S ), а следующий тактовый импульс будет прибавляться по модулю М уже к данному состоянию.

Записью N-разрядного кода в регистр 41 управляет распределитель 42 совместно с блоком реле 43. По приходу первого импульса с блока 29 настройки блока 3 формирования кодовых последователей на С-вход распределителя 42 блока 5 буферного регистра на выходе первого канала распределителя возникает положительный потенциал, который вызывает срабатывание реле Р блока реле 43 и N-выходов счетчика 39 подключаются к соответствующей ячейке регистра 41. При этом происходит перепись содержимого счетчика 39 в N-разрядную ячейку регистра 41. Данная перепись будет осуществляться на этапе прибавления к содержимому счетчика 39 С -такто- вых импульсов, и N-разрядный код подключенной ячейки регистра 41 буде меняться в соответствии с изменением содержимого счетчика 39. Причем двоичный код первого частотного элемента записывается в последнюю ячейку регистра 41, второго - в предпоследнюю и т.д.

При возникновении -на М-вькоде распределителя 42 потенциала и наличии, сигнала на выходе блока 34 настройки RS-триггер 16 управления бло- ка 1 переходит в единичное состояние и записывается единица в первьй разряд регистра 5° блока 6 опроса буферного регистра. Переход RS-триггера 16 управления в единичное состояние разрешает прохождение тактовых импульсов с генератора 2 через элемент И 18 на сдвигающий вход регистра 45 и запрещает прохождение импульсов через э,ле- мент И 19. Единица, передвигаясь по разрядам регистра 45, через блок 46 опроса считывает содержимое первой, второй и т.д., М,Н-разрядной ячейки регистра 41,.которое через блок 46

5

0

0

0

5

5

опроса в двоичном коде подается на вход цифрового коммутатора 8.

Цифровой коммутатор 8 ставит каждому числу -J

j

заранее определенный

сигнал сетки частот

и;/ (л) - ,

где Ыр - несущая часто.та ДЧ-сигнала, JW - минимальный частотный сдвиг.

Для-получения фазы выходного сигнала в моменты переключения без скачков сетка частот формируется от такой опорной частоты, которая синхронизирует работу блока 6 опроса буферного регистра.

С выхода цифрового коммутатора 8 сформированньш сигнал поступает в усилитель 9 мощности, где усиливается и далее подается для излучения в антенну.

Формула изобретения

5 Устройство для передачи многочастотных сигналов, содержащее блок управления, первый выход которого соединен с первым входом блока опроса буферного регистра, второй вход ко0 торого соединен с первым выходом блока буферного регистра, первый вход которого объединён с первым входом блока формирования кодовых последовательностей и соединен с вторым выходом блока управления, третий, четвертый и пятый выходы которого соединены соответственно с вторым, третьим и четв гртым входами блока формирования кодовых последовательностей, первый выход которого соединен с вторым входом блока буферного регистра, первый выход блока опроса буферного регистра через цифровой коммутатор соединен с входом усилителя мощности, выход которого является выходом устройства, шестой выход блока управления через генератор сетки частот соединен с вторым входом цифрового коммутатора, седьмой выход блока управления через генератор тактовой частотой соединен с вторым входом генератора сетки частот, отличающееся тем, что, с целью увеличения объема ансамбля передаваемых сигналов, введен блок промежуточного сложения, причем его первый, второй и третий выходы соединены соответственно с третьим входом блока буферного регистра, первым входом блока управления и четвертым входом блока буферного регистра, пятый вход которого соединен с восьмым выходом блока управления, второй вход которого объединен с третьим входом блока опроса буферного регистра и соединен с вторым выходом блока буферного регистра, четвертый вход и второй выход блока опроса буферного регистра соединены соответственно с вторым выходом и третьим входом блока управления, девятый и десятый выходы

которого соединены соответственно с первым и вторым входами блока промежуточного сложения, третий, четвертый и пятый входы которого соединены соответственно с первым, вторым выходами блока формирования кодовых последовательностей и вторым выходом блока управления, четвертый вход которого объединен с шестым входом блока промежуточного сложения и соединен с выходом генератора тактовой частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Устройство для передачи многочастотных сигналов | 1983 |

|

SU1107328A1 |

| Устройство для передачи многочастотных сигналов | 1987 |

|

SU1406817A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Многоканальный счетчик импульсов | 1983 |

|

SU1170610A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1990 |

|

RU2010455C1 |

Изобретение обеспечивает увеличение объема ансамбля передаваемых сигналов. Устройство состоит из блока управления (БУ) 1, генератора 2 тактовой частоты, блока 3 формирования кодовых последовательностей,блока промежуточного сложения (БПС) 4, блока 5 буферного регистра, блока 6 опроса буферного регистра, генератора 7 сетки частот, цифрового кокяму- татора 8 и усшштеля мощности 9. На БУ 1 набирается номер передаваемого . сигнала. При нажатии кнопки Передача запускается генератор 2, а Б БУ 1 определяется номер оптимальной системы, к которой относится номер набранного сигнала. Сигнал о номере оптимальной системы поступает в БПС 4, который введен для обеспечения увеличения объема ансамбля передаваемых сигналов. 7 ил. 00 сд 4 СО

Передача

От элемента

Ч

16

19

П 1(элементам

Н элементу

Н элементу

От элемента Its

j}-n

J

гг

Н элементам 2g Л JJ. 3. i/X HUiii 5

К блоку

0us.Z

От цянентл

I

«

N

Кзлвмунтон Ц

От элемента ZS

От унемента

9М

От бло1ш1

От элепенти

От пвны От схемы

От Sflona 1

... M t

L,3 -fvj

a7Lfxg/«,

Фиг.6

От 9/№нен- та itif

fl уценен-

От мемен- та 22

| Устройство для передачи многочастотных сигналов | 1985 |

|

SU1319305A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-11-23—Публикация

1985-08-02—Подача