Изобретение относится к гибридной вычислительной технике и предназначено для решения систем алгебраических уравнений с произвольной матрицей коэ фбшциентов.

Цель изобретения - повышение быстродействия и расширение класса решаемых задач.

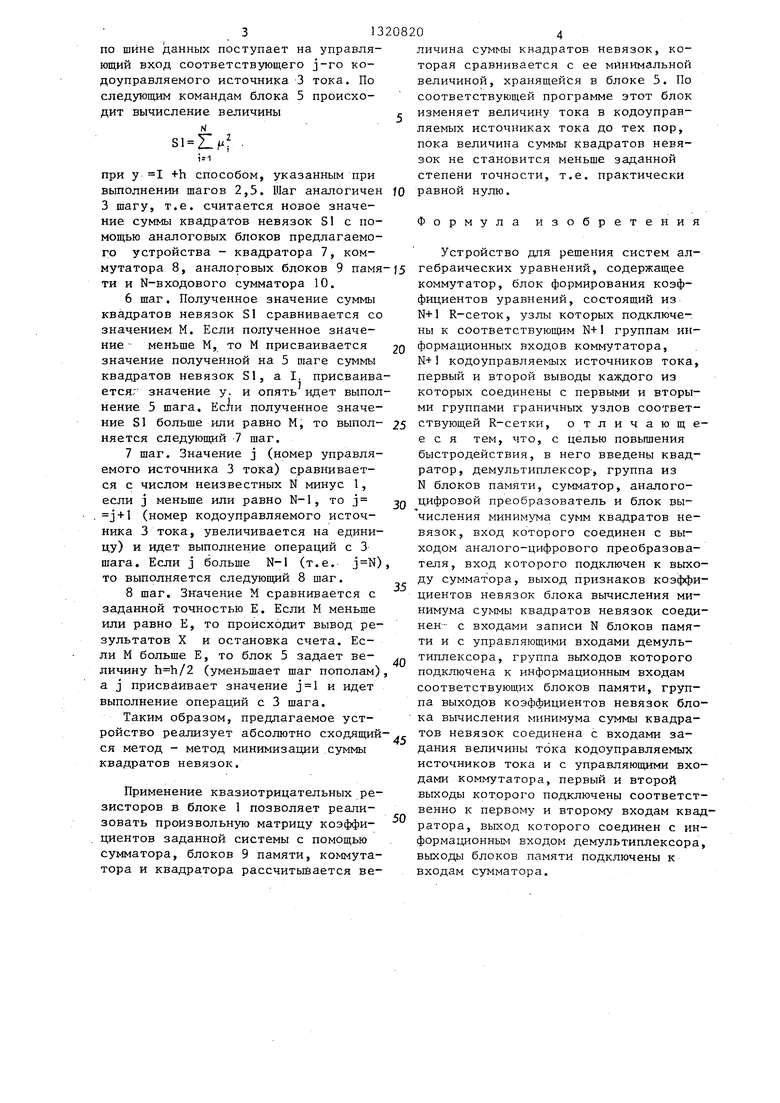

На фиг, 1 представлена блок-схема устройства; на фиг, 2 - схема алгоритма работы блока 5,

Устройство содержит блок 1 формирования коэффициентов уравнений состоящий из N+1-R-ceTOK 2, группу N+ кодоуправляемых источников 3 тока, первый коммутатор 4, цифровой вычислительный блок 5, аналого-цифровой преобразователь 6, квадратор 7, второй коммутатор 8, блоки 9 памяти, суматор 10,- Цифровой вычислительны блок 5 содержит микроЭВМ,, два выходных регистра и входной регистр.

Устройство работает следующим образом.

1 шаг, В блок 5 (фиг, 2) задаются

величины

I, J U N, А, В, Е, h,

где I; - начальные произвольные значения токов, задаваемые в кодоуправляемых источниках 3 тока (фиг, 1); номер кодоуправляемого источника 3 тока, которым уп равляет в данный момент блок 5;

число неизвестных в заданной системе уравнений; матрица коэффициентов заданной системы; вектор свободных членов; заданная точность; величина щага,

2 шаг. По первой команде блока 5 замыкаются соответствующие реле коммутатора А таким образом, что элемен ты R,,, ,. ,R,R блока 1 объединяются в последовательную цепь, причем один выход коммутатора 4 (свободный вывод резистора R,) подключается к одному входу квадратора 7, а другой выход (свободный вывод резистора R) подключается к другому входу квадратора 7. Как элементы резистивной матрицы блока 1, резисторы R,R,5. подключены к соответствующим

)

j NАВЕh

iH 1

кодоуправляемым источникам 3 тока 1°,Ij,,,,,1,IN+1 и по ним протекает ток 1° ,1° ,, .., 1 , 1., (начальное значение тока может быть произвольным)

Таким образом, к входам квадратора 7 приложено напряжение

f RlIwfr- -H- - - --( iH

Это напряжение, соответствующее невязке первой строки системы алгебраических уравнений А.Вэ возводится в квадрат и подается через одно- входовой коммутатор 8 в первый блок

9 памяти. После этого, из блока 5 подается следующая команда, по которой переключаются одновходовой коммутатор 8 и коммутатор 4, Теперь к входам квадратора 7 подключается

последовательно цепь элементов резистивной матрицы блока 1 Rj,R,..,, R ,R , а напряжение на входах квадратора 7 равно .,.. Величина этого напряжения возводится в квадрат и записывается во второй блок 9 памяти. По следующей команде блока 5 в последующие блоки 9 памяти записываются квадраты величины напряжений и , ., ,|Ц , соответствуюш 1е квадратам невязок каждой следующей строки заданной системы, С выхода N-входного сумматора 10 напряжение, соответствующее

N

2

через аналогово-цифровой преобразователь 6 поступает в блок 5, На заканчивается 2 шаг.

3 шаг. По первой команде блока 5 значение у- I--h }3 виде цифрового кода по шине данных поступает на управляющий вход (на цифроаналоговый преобразователь) j-ro кодоуправляе- ого источника 3 тока. По второй и CJIeдyюш м командам блока 5 происхоит вычисление величины N

5, 1.

2 1

при у. I -h, способом,- указанным

45

50

при выполнении шага 2.

4шаг. Полученное значение суммы квадратов невязок S сравнивается со- значением М. Если полученное значение S1 меньше М, то М присваивается значение полученной на 3 шаге величины суммы квадратов невязок S1, а

I.- присваивается значзние у. и опять 55 идет выполнение 3 шага. Если полученное значение S больше или равно М, то выполняется следующий 5 шаг.

5шаг. По команде блока 5 значение в виде цифрового кода

по шине данных поступает на управляющий вход соответствующего j-ro ко- доуправляемого источника 3 тока. По следующим командам блока 5 происходит вычисление величины

,f .

iil

при у 1 +h способом, указанным при выполнении шагов 2,5. Шаг аналогичен 3 шагу, т.е. считается новое значение суммы квадратов невязок S1 с помощью аналоговых блоков предлагаемо- г о устройства - квадратора 7, коммутатора 8, аналоговых блоков 9 памя-15 гебраических уравнений, содержащее

ти и N-входового сумматора 10.

6щаг. Полученное значение суммы квадратов невязок S1 сравнивается со значением М. Если полученное значение- меньше М, то М присваивается значение полученной на 5 шаге суммы квадратов невязок S1, а I, присваивается; значение у. и опять идет выполнение 5 шага. Если полученное значение S1 больше или равно М, то выпол- няется следуюш 1й 7 шаг.

7шаг. Значение j (номер управляемого источника 3 тока) сравнивается с числом неизвестных N минус 1, если j меньше или равно N-1, то j j+I (номер кодоуправляемого источника 3 тока, увеличивается на единицу) и идет выполнение операций с 3 шага. Если j больше N-1 (т.е. ) то выполняется следующий 8 шаг.

8шаг. Значение М сравнивается с заданной точностью Е. Если М меньше или равно Е, то происходит вывод результатов X и остановка счета. Если М больше Е, то блок 5 задает величину (уменьшает шаг пополам) а j присваивает значение и идет выполнение операций с 3 шага.

Таким образом, предлагаемое устройство реализует абсолютно сходящийся метод - метод минимизации суммы квадратов невязок.

Применение квазиотрицательных резисторов в блоке 1 позволяет реализовать произвольную матрицу коэффициентов заданной системы с помощью сумматора, блоков 9 памяти, коммутатора и квадратора рассчитывается ве

личина квадратов невязок, которая сравнивается с ее минимальной величиной, хранящейся в блоке 5. По соответствующей программе этот блок изменяет величину тока в кодоуправ- ляемых источниках тока до тех пор, пока величина суммы квадратов невязок не становится меньше заданной степени точности, т.е. практически равной нулю.

Формула изобретения Устройство для решения систем ал

0

5

5

0

5

0

коммутатор, блок формирования коэффициентов уравнений, состоящий из N+1 R-сеток, узлы которых подключены к соответствующим N+1 группам информационных входов коммутатора, NH-1 кодоуправляемых источников тока, первый и второй выводы каждого из которых соединены с первыми и вторыми группами граничных узлов соответствующей R-сетки, отличающееся тем, что, с целью повьш1ения быстродействия, в него введены квадратор, демультиплексор-, группа из N блоков памяти, сумматор, аналого- цифровой преобразователь и блок вы- числения минимл ма сумм квадратов невязок, вход которого соединен с выходом аналого-цифрового преобразователя, вход которого подключен к выходу сумматора, выход признаков коэффициентов невязок блока вычисления минимума суммы квадратов невязок соединен- с входами записи N блоков памяти и с управляющими входами демуль- типлексора, группа выходов которого подключена к информационным входам соответствующих блоков памяти, группа выходов коэффициентов невязок блока вычисления минимума суммы квадратов невязок соединена с входами задания величины тока кодоуправляемых источников тока и с управляющими входами коммутатора, первый и второй выходы которого подключены соответственно к первому и второму входам квадратора, выход которого соединен с информационным входом демультиплексора, выходы блоков памяти подключены к входам сумматора.

J/i й;В

. -

y,

fi-sr. 3j,-yj,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения линейных систем алгебраических уравнений | 1985 |

|

SU1325464A1 |

| Устройство для моделирования трубопроводных систем | 1978 |

|

SU750520A1 |

| Цифровое устройство для решения систем линейных алгебраических уравнений | 1976 |

|

SU648988A1 |

| Устройство для решения систем линйныхАлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU824217A1 |

| Устройство для решения краевых задач | 1989 |

|

SU1640718A1 |

| Цифровое устройство для решения систем линейных алгебраических уравнений | 1975 |

|

SU559241A1 |

| Устройство для сжатия и передачи информации | 1988 |

|

SU1515183A1 |

| Устройство для решения нелинейных задач теплопроводности | 1986 |

|

SU1363269A1 |

| Цифровое устройство для реше-Ния СиСТЕМ АлгЕбРАичЕСКиХ уРАВ-НЕНий | 1979 |

|

SU798863A1 |

| Устройство для решения систем линейных алгебраических уравлений | 1972 |

|

SU564638A1 |

Изобретение относится к гибридной вычислительной технике и нред- назначено для решения систем алгебраических уравнений с произвольной невырожденной матрицей коэффициентов. Цель изобретения - повьшение быстродействия и расширение класса решаемых задач. Устройство содержит блок 1 формирования коэффициентов уравнений, состоящий из группы R-ce- ток 2, два коммутатора 4 и 8, группу кодоуправляемых источников 3 тока, квадратор 7, группу блоков 9 памяти, сумматор 10, аналого-цифровой преобразователь 6 и цифровой вычислительный блок 5, состоящий из микроэвм, двух выходных регистров и входного регистра. Устройство позволяет повысить быстродействие и расширить класс решаемых задач за счет возможности решения нелинейных систем алгебраических уравнений. 2 ил. О S (Л с Ё со ГчЭ О 00 Is5 О

5jMZ 7 шае

;v-/

1Z

/ fj

Вывод результата

Составитель В.Рыбин Редактор И.Касарда Техред Н.Глущенко

Заказ 2660/52 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. 2.

Корректор С. Черни

| Фадеев Д.К | |||

| и Фадеева В.Н | |||

| Вычислительные методы линейной алгебры, М.: | |||

| Физматгиз, 1960 | |||

| УСТРОЙСТВО для РЕШЕНИЯ СИСТЕМ ЛИНЕЙНЫХ АЛГЕБРАИЧЕСКИХ УРАВНЕНИЙ | 0 |

|

SU166150A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-06-30—Публикация

1984-11-26—Подача