Изобретение относится к вычислительной технике и может быть использовано как автономно, так и в составе цифровых и аналого-цифровых вычислительных комплексов. Известно цифровое устройство для решения систем алгебраических уравне ний , содержащее блок формирования коэффициентов, сумматоры/ регистры, цифровые интеграторы, блок уравновешивания. В них вычислительный процес реализован на основе инкрементных модификаций методов минимизации Р-. Недостатком известного устрюйства является низкая надежность и технологичность . Наиболее близким по технической сущности к предлагаемому является цифровое устройство для решения систем алгебраических уравнений, которое содержит блоки уравновешивания и синхронизации. В блоках формирования коэффициент тов происходит умножение кодов коэффициентов на 31;аки приращений переменных. Результаты умножения построч но алгебраически суммируются в накапливающих сумматорах и регистрах и образуют, вектор невязок. Алгоритм минимизации регшизуется блоком уравновешивания, на выходе которого формируются приращения вектора переменных. Полное значение вектора переменных накапливается в цифровых интеграторах. Вычислительный процесс заканчивается, когда все величины невязок становятся равными нулю 2. Недостатком этого устройства является ориентация их структур на применение интегральных схем малой и средней степени интеграции, что определяет более низкую надежность и технологичность таких устройств, в частности степень однородности используемого оборудования, по сравнению с устройствами, структуры которых ориентированы на применение больших интегральных схем. Кроме этого, в схеме устройства не предусмотрены какие-либо блоки для удобного сопряжения с такими же и другими вычислительными и периферийными устройствами, в .частности с цифровыми или Гдифроаналоговымр;. вычислительными комплексами, и использовании в качестве аппаратурио реализованной подпрограммы, что существенно ограничивает ее функциональные возможности..

Цель изобрет.ения - повышение надежностиустройства.

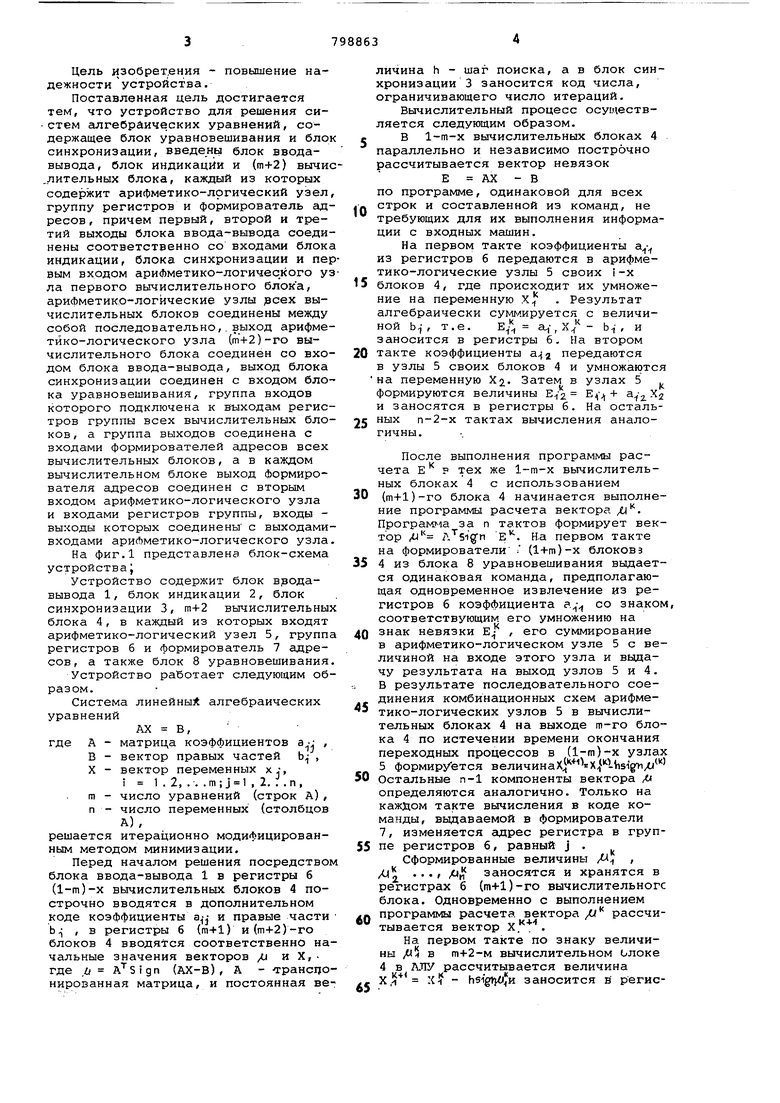

Поставленная цель достигается тем, что устройство для решения систем алгебраических уравнений, содержащее блок уравновешивания и блок синхронизации, введены блок вводавывода, блок индикации и (т+2) вычис„лительных блока, каждый из которых содержит арифметико-логический узел группу регистров и формирователь адресов, причем первый, второй и третий выходы блока ввода-вывода соединены соответственно со входами блока индикации, блока синхронизации и первым входом ариФметико-логичес кого узла первого вычислительного блока, арифметико-логические узлы рсех вычислительных блоков соединены между собой последовательно,. выход арифметико-логического узла (т+2)-го вычислительного блока соединен со входом блока ввода-вывода, выход блока синхронизации соединен с входом блока уравновешивания, группа входов которого подключена к выходам регистров группы всех вычислительных блоков, а группа выходов соединена с входами формирователей адресов всех вычислительных блоков, а в каждом вычислительном блоке выход формирователя адресов соединен с вторым входом арифметико-логического узла и входами регистров группы, входы выходы которых соединены с выходамивходами арифметико-логического узла.

На фиг.1 представлена блок-схема устройстваJ

Устройство содержит блок вродавывода 1, блок индикации 2, блок синхронизации 3, ni+2 вычислительных блока 4, в каждый из которых входят арифметико-логический узел 5, группа регистров 6 и формирователь 7 адресов, а также блок 8 уравновешивания.

Устройство работает следующим образом.

Система линейный алгебраических уравнений

АХ В,

где А - матрица коэффициентов , В - вектор правых частей Ь , X - вектор переменных х.-,

i 1 . 2, . , . m ; j 1 , 2. . . п , m - число уравнений (строк А), п - число переменных (столбцов

А),

решается итерационно модифицированным методом минимизации.

Перед началом решения посредством блока ввода-вывода 1 в регистры 6 (l-m)-x вычислительных блоков 4 построчно вводятся в дополнительном коде коэффициенты .,- и правые части Ь , в регистры 6 (m+l) и(т+2)-го блоков 4 вводятся соответственно начальные значения векторов дд и X, где а ASign (АХ-В) , А - транспонированная, матрица, и постоянная величина h - шаг поиска, а в блок синхронизации 3 заносится код числа, ограничивающего число итераций.

Вычислительный процесс осуществляется следующим образом. В 1-т-х вычислительных блоках 4 параллельно и независимо построчно рассчитывается вектор невязок

Е АХ - В по программе, одинаковой для всех

строк и составленной из команд, не требующих для их выполнения информации с входных машин.

На первом такте коэффициенты регистров 6 передаются в арифметико-логические узлы 5 своих -X

блоков 4, где происходит их умножение на переменную Х . Результат алгебраически суг/Ц/ируется с величиной Ь , т.е. Е/ ,Х/- Ь , и заносится в регистры 6, На втором

такте коэффициенты передаются

в узлы 5 своих блоков 4 и умножа1отся на переменную Xj. Затем в узлах 5 формируются величины , + и заносятся в регистры 6. На остальных n-2-x тактах вычисления аналогичны.

После выполнения программы расчета Е р тех же 1-т-х вычислительных блоках 4 с использованием

(т+1)-го блока 4 начинается выполнение программы расчета вектора . ПрограгФ1а за п тактов формирует вектор /и A Sign Е. На первом такте на формирователи (1+т)-х блоковз

4 из блока 8 уравновешивания выдается одинаковая команда, предполагающая одновременное извлечение из регистров 6 коэффициента со знаком, соответствующим его умножению на

знак невязки EJ , его суммирование в арифметико-логическом узле 5 с величиной на входе этого узла и выдачу результата на выход узлов 5 и 4. В результате последовательного соединения комбинационных схем арифметико-логических узлов 5 в вычислительных блоках 4 на выходе т-го блока 4 по истечении времени окончания переходных процессов в (l-m)-x узлах 5 формируется величинаХ «Х 11131дт1Л1

Остальные п-1 компоненты вектора 4 определяются аналогично. Только на кажйом такте вычисления в коде команды, выдаваемой в формирователи 7, изменяется адрес регистра в группе регистров б, равный j .

Сформированные величины Л , /j( ..,, fJi заносятся и хранятся в регистрах б (т+1)-го вычислительногс блока. Одновременно с выполнением

программы расчета вектора JU рассчитывается вектор X. .

На первом такте по знаку величины ;К5 в m+2-M вычислительном с/локе 4 в АЛУ рассчитывается величина

X,i Х - . заносится в регис

тры 6. На остальных п-1 тактах по знакам соответствующих компонентов вектора /tj рассчитываются осталыше компоненты вектора .

После определения вектора X в блоке 8 уравновешивания проверяют условия окончания итерационного вычислительного процесса по ,эада.нномьс1 числу итераций или зацикливанию процесса поиска вблизи точки искомого решения..При невыполнении этих условий итерационный процесс продолжается и повторяется вычислительный процесс.

При вводе и выводе информации в какой-либо i-и вычислительный блок 4 в формирователи 7 всех остальных вычислительных блоков 4 выдается команда , по которой информация с входа блока 4 проходит без изменений на его выход.

На формирователь 7 i-го блока 4 поступает команда ввода-вывода, обеспечивающая запись информации с входа блока 4 в регистры 6 или считывание информации из регистров 6 на выход блока 4; Выводимая информация по цепочке последовательно соединённых АЛУ 5 поступает на блок 1 и чере.з него на блок 2 индикации. -Управление вводом и выводом-информации, а также решением задачи «осуществляется блоком 8 уравновешивания по сигналам с блоков ввода-вывода 1 и синхронизации 3

Блок ввода-вывода представляет собой интерфейс ввода-вывода, состоящий из подканалов ручного и автоматического ввода-рывода информации, и необходим для ввода исходной ин-. формации и команд, а также для организации обмена ин ормацией и командами при неавтономном (системном) использовании предлагаемого устройства. Пример выполнения блокя вводавывода приведен м-- .2. Он содержит клавиатуру 9, преобразователь 10 десятичного кода в двоичный, мультиплексоры 11 и 12, узел управления 13 генератор 14 синхроимпульсов, входной регистр 15, память 16, узел 17 регистров, выходной регистр 18, коммутатор 19 и преобразователь 20 двоичного года в двоично-десятичный.

Блок ввода-вывода работает следующим образом.

Лины 21-25 составляют внешний интерфейс для связи с каналом вводавывода. Прямая информационная шина 21, обратная - 25, адресная шина 22, шины управления 23 и 24. По шине 26 информация с блока вводвывода поступает на информационную шину первого вычислительного блока. Шина 27 .используется для передачи, синхроимпульсов с генератора 14 и управляющего слова из регистров 17 в блок синхронизации и далее не блок ураёновешив ния. По шине 28 информация с вьйсодной ши.ны m+2-ro вычислительного блока Поступает на выходной регистр 18. гаины 26-29 образуют внутренний интерфейс устройства.

При ручном вводе посредством клавиатуры 9 набирается вводимое число, выдается сигнал переключения мультиплексоров 11 и 12 на ручной подканал ввода, в регистрах 17 через мультиплексор 12 и память 16 вводится адресная информация. Вводимое число с клавиатуры 9 через преобразователь

0 10, блоки 11, 15 поступают на вход б. При автоматическом -вводе мультиплексоры 11,12 переключаются на шины 21, 22. Информация с шины 21 через мультиплексор 11 и входной регистр 15

5 поступает на шину 26. Адресная информация с шины 22 под управлением узла 13 и генератора 14 синхроимпульсов побайтно .заносится через мультиплексор 12 и память 16 в узел 17 регист0ров. Сформированное управляющее слово передается в шину 21.

Ручной и автоматический вывод информации осуществляется аналогично вводу с той лишь разницей, что мультиплексор 11 блокируется для прохож5дения информации и с узла 13 управления на коммутатор 19 поступает сигнал разрешения выдачи информации с выходного регистра 18 на шину 8. Через преобразователь 20 код с выходного

0 регистра 18 выдается на блок индикации.

Блок уравновешивания представляет собой управляющий автомат для задания порядка выполнения всех подпро5грамм вычис лительными блоками. Он состоит из m+2-x микроавтоматов, схема одного из которых показана на фиг.З. Каждый вычислительный блок управляется .своим микроавт.оматом.

0 Такой микроавтомат состоит из узла логических условий: (улу) 30, элемента и 31, памяти 32, дешифратора 33, счетчика 34, элемента ИЛИ 35,, коммутатора 36, 37, схемы 38 сравнения и элемента И 39.

5

Применение ni+2-x последовательно соединенных однотипных вычислительных блоков повышает надежность и степень однородности применяемой аппаратуры в устройстве и делает

0 возможным его реализацию на больших интегральных схемах.

Применение блока ввода-вывода по.зволяет/ испольэовать устройство как в автономном режиме, так и в качест5ве специализированного процессора в составе цифровых и .цифроаналоговкхх вычислительных комплексов. Этот блок позволяет для решения задач большой размерности создать однородную,блочно наращиваемую структур из предла0гаемых устройств.

Формула изобретения

Цифровое устройство для решения XJ систем алгебраических уравнений, содержащее блок уравновешивания и блок синхронизации, отличающеес я тем, что, с целью повышения 1аДежности, в-него введены блок в ода-вывода, блок индикации и (т+2) вычислительных блока, каждый иа которых, содержит арифметико-логйчв€кий узел, .группу регистров и формирователь адресов, причем первый, второй и третий выходы блока вводавывода соединены соответственно со входами блока индикации, блока синхронизации и первым входом арифметико-логического узла первого вычислительного блока, арифметико-логические У..ЗЛЫ всех вычислительных блоков соединены между собой последов-ательноf выход арифметико-логического узла (т+2)-го вьмислительного блока соединен со входом блока ввода-вывода, выход блока синхронизации соединен с входом блока уравновешиваний, группа входов которого подключена: к выходам регистров группы всех вычислительных блоков, а группа выходов соединена с входами Формирователей адресов всех вычислительных блоков, а в каждом вычислительном блоке выхо формирователя адреса соединен с вторым входом арифметико-логического узла и входами регистров группы, вхо ды-выходы которых соединены с выходами-входами арифметико-логического узла..

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 559241, кл.С 06 F 15/32, 1977.

2.Авторское свидетельство СССР № 529468, кл.а 06 F 15/32, 1976

(прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения системы алгебраических уравнений | 1981 |

|

SU966702A1 |

| Мультиплексный канал | 1984 |

|

SU1167613A1 |

| Устройство для сопряжения оперативной памяти с внешними устройствами | 1981 |

|

SU993237A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Микропрограммное устройство для управления каналами ЭВМ | 1982 |

|

SU1068938A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Процессор | 1989 |

|

SU1725224A1 |

Авторы

Даты

1981-01-23—Публикация

1979-02-21—Подача