Изобретение относится к запоминающим устройствам, которые иснользуются для временного хранения данных, и может быть использовано в устройствах автоматики и вычислительной техники.

Цель изобретения - расширение области применения устройства за счет организации режима «последний вошел - пкр- вый вышел.

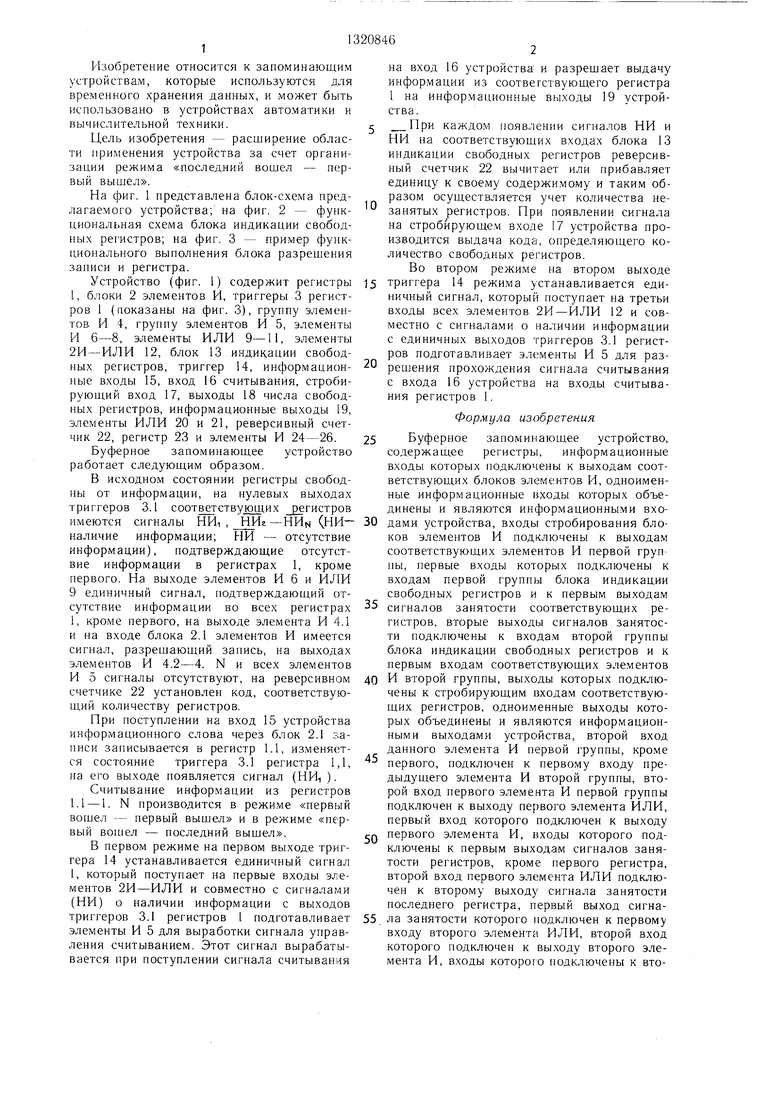

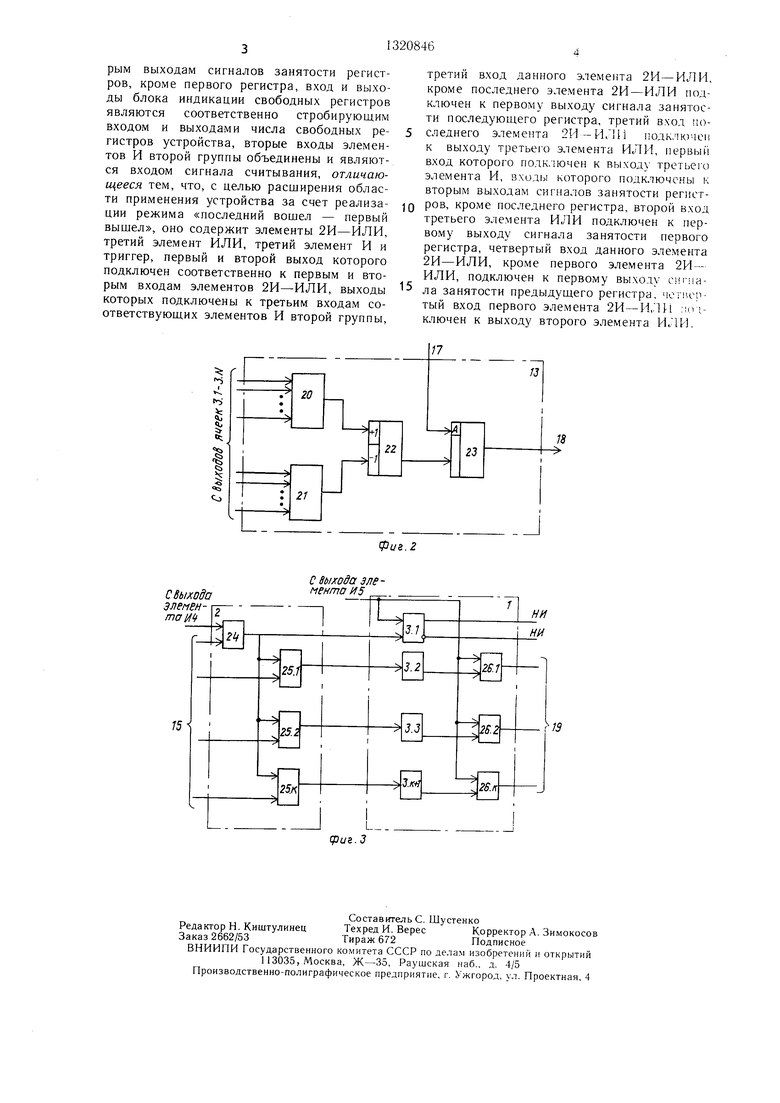

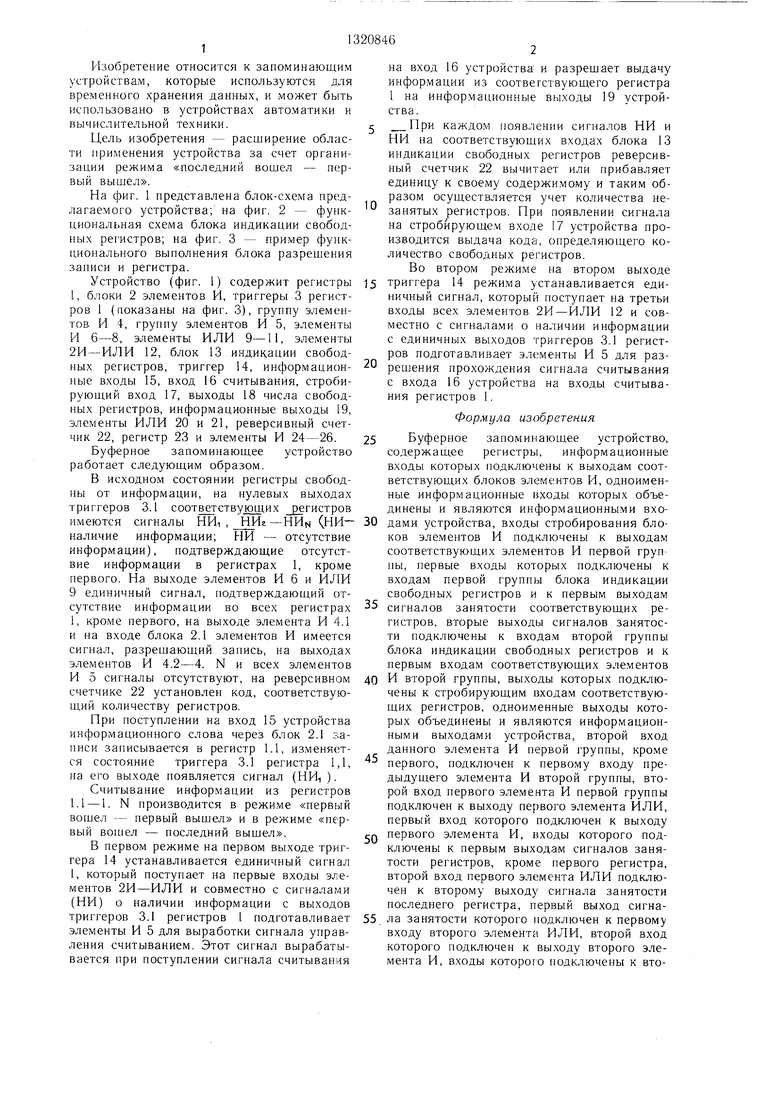

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - функциональная схема блока индикации свободных регистров; на фиг. 3 - пример функционального выполнения блока разрешения записи и регистра.

на вход 16 устройства и разрешает выдачу инфор.мации из соотвегствующего регистра 1 на информационные выходы 19 устройства.

5 При каждом появлении сигналов НИ и

НИ на соответствуюших входах блока 13 индикации свободных регистров реверсивный счетчик 22 вычитает или прибавляет единицу к своему содержимому и таким образом осуществляется учет количества незанятых регистров. При появлении сигнала на стробйруюц1ем входе 17 устройства производится выдача кода, определяющего количество свободнЕ1 х регистров.

Во втором режиме па втором выходе

10

Устройство (фиг. 1) содержит регистры 1 триггера 14 режи.ма устанавливается еди- 1, блоки 2 элементов И, триггеры 3 регист-ничный сигнал, который поступает на третьи

ров 1 (показаны на фиг. 3), группу элемен-входы всех элементов 2И-ИЛИ 12 и совтов И 4, группу элементов И 5, элементыместно с сигналами о наличии информации

И 6-8, элементы ИЛИ 9-11, элементы 2И-ИЛИ 12, блок 13 индикации свободных регистров, триггер 14, информацион- 20 ные входы 15, вход 16 считывания, строби- рующий вход 17, выходы 18 числа свободных регистров, информационные выходы 19, элементы ИЛИ 20 и 21, реверсивный счетчик 22, регистр 23 и элементы И 24-26. 25 Буферное запоминающее устройство.

с единичных выходов триггеров 3.1 регистров подготавливает эл(;менты И 5 для раз- рещения прохождения сигнала считывания с входа 16 устройства на входы считывания регистров 1.

Формула изобретения

Буферное запоминающее устройство работает следующим образом.

В исходном состоянии регистры свободны от информации, на нулевых выходах триггеров 3.1 соответствуккцих 2егистров

содержащее регистры, информационные входы которых подключены к выходам соответствующих блоков элементов И, одноименные информационные входы которых объединены и являются информационными вхоков элементов И подключены к выходам соответствующих элементов И первой группы, первые входы которых подключены к входам первой группы блока индикации свободных регистров и к первым выходам сигналов занятости соответствующих регистров, вторые выходы сигналов занятости подключены к входам второй группы блока индикации свободных регистров и к первым входам соответствующих элементов

имеются сигналы HHi , НИг-НИ|ч (НИ 30 дами устройства, входы стробирования бло- наличие информации; НИ - отсутствие информации), подтверждающие отсутствие информации в регистрах 1, кроме первого. На выходе элементов И 6 и ИЛИ 9 единичный сигнал, подтверждающий отсутствие информации во всех регистрах 35 1, кроме первого, на выходе элемента И 4.1 и на входе блока 2.1 элементов И имеется сигнал, разрешающий запись, на выходах элементов И 4.2-4. N и всех элементов И 5 сигналы отсутствуют, на реверсивном 40 И второй группы, выходы которых подклю- счетчике 22 установлен код, соответствую-чены к стробирующим входам соответствующих регистров, одноименные выходы которых объединены и являются информационными выходами устройства, второй вход данного элемента И первой группы, кроме первого, подключен к первому входу предыдущего элемента И второй группы, второй вход первого элемента И первой группы подключен к выходу первого элемента ИЛИ, первый вход которого подключен к выходу CQ первого элемента И, входы которого подключены к первым выходам сигналов занятости регистров, кроме первого регистра, второй вход первого элемента ИЛИ подключен к второму выходу сигнала занятости последнего регистра, первый выход сигна- триггеров 3.1 регистров 1 подготавливает 55 ла занятости которого нодключен к первому элементы И 5 для выработки сигнала управ-входу второго элемента ИЛИ, второй вход

которого подключен к выходу второго элемента И, входы которого подключены к втощий количеству регистров.

При поступлении на вход 15 устройства информационного слова через блок 2.1 записи записывается в регистр 1.1, изменяется состояние триггера 3.1 регистра 1,1, на его выходе появляется сигнал (НИ1 ).

Считывание информации из регистров 1.1 - 1. N производится в режиме «первый вошел - первый вышел и в режиме «первый вошел - последний выщел.

В первом режиме на первом выходе триггера 14 устанавливается единичный сигнал 1, который поступает на первые входы элементов 2И-ИЛИ и совместно с сигналами (НИ) о наличии информации с выходов

ления считыванием. Этот сигнал вырабатывается при поступлении сигнала считывания

на вход 16 устройства и разрешает выдачу инфор.мации из соотвегствующего регистра 1 на информационные выходы 19 устройства.

При каждом появлении сигналов НИ и

НИ на соответствуюших входах блока 13 индикации свободных регистров реверсивный счетчик 22 вычитает или прибавляет единицу к своему содержимому и таким образом осуществляется учет количества незанятых регистров. При появлении сигнала на стробйруюц1ем входе 17 устройства производится выдача кода, определяющего количество свободнЕ1 х регистров.

Во втором режиме па втором выходе

местно с сигналами о наличии информации

Буферное запоминающее устройство.

с единичных выходов триггеров 3.1 регистров подготавливает эл(;менты И 5 для раз- рещения прохождения сигнала считывания с входа 16 устройства на входы считывания регистров 1.

Формула изобретения

Буферное запоминающее устройство.

содержащее регистры, информационные входы которых подключены к выходам соответствующих блоков элементов И, одноименные информационные входы которых объединены и являются информационными вхо дами устройства, входы стробирования бло- И второй группы, выходы которых подклю- чены к стробирующим входам соответствуюков элементов И подключены к выходам соответствующих элементов И первой группы, первые входы которых подключены к входам первой группы блока индикации свободных регистров и к первым выходам сигналов занятости соответствующих регистров, вторые выходы сигналов занятости подключены к входам второй группы блока индикации свободных регистров и к первым входам соответствующих элементов

дами устройства, входы стробирования бло- И второй группы, выходы которых подклю- чены к стробирующим входам соответствуюрым выходам сигналов занятости регистров, кроме первого регистра, вход и выходы блока индикации свободных регистров являются соответственно стробирующим входом и выходами числа свободных регистров устройства, вторые входы элементов И второй группы объединены и являются входом сигнала считывания, отличающееся тем, что, с целью расширения области применения устройства за счет реализации режима «последний вошел - первый вышел, оно содержит элементы 2И-ИЛИ, третий элемент ИЛИ, третий элемент И и триггер, первый и второй выход которого подключен соответственно к первым и вторым входам элементов 2И-ИЛИ, выходы которых подключены к третьим входам соответствующих элементов И второй группы.

Сдыхода

С Выхода элемента и 5

15

третий вход данного элемента 2И-ИЛИ, кроме последнего элемента 2И-ИЛИ подключен к первому выходу сигнала занятости последуюш,его регистра, третий вход последнего элемента 2И-ИЛ11 подключен к выходу третье|-о элемента ИЛИ, первый вход которого подключен к выходу третьего элемента И, Bxoaiji которого подключены к вторым выходам сигналов занятости регпстров, кроме последнего регистра, второй вход третьего элемента ИЛИ подключен к первому выходу сигнала занятости первого регистра, четвертый вход данного элемента 2И-ИЛИ, кроме первого элемента 2И - ИЛИ, подключен к первому выходу ciirim- ла занятости предыдущего регистра, четиор- тый вход первого элемента 2И-ИЛИ invb ключен к выходу второго элемента ИЛИ.

V5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1983 |

|

SU1149236A1 |

| Микропрограммное вычислительное устройство | 1984 |

|

SU1229761A1 |

| Буферное запоминающее устройство | 1981 |

|

SU959164A2 |

| Устройство для ввода информации | 1982 |

|

SU1078419A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1332384A2 |

| Устройство для отладки многопроцессорных систем | 1988 |

|

SU1644145A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для управления памятью | 1985 |

|

SU1280626A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

Изобретение относится к запоминающим устройствам, которые используются для временного хранения данных, и может быть использовано в устройствах автоматики и вычислительной техники. Цель изобретения - расширение области применения за счет реализации режима «последний вошел - первый вышел. Буферное запоми- наюш.ее устройство содержит регистры 1, блоки 2 элементов И, триггеры, группы элементов И 4 и 5, элементы И 6-8, элементы ИЛИ 9-11, элементы 2И-ИЛИ 12, блок 13 индикации свободных регистров, триггер 14, информационные входы 15, вход 16 чтения, стробирующий вход 17, выходы 18 числа свободных регистров и информационные выходы 19. Устройство работает в двух режимах, определяемых состоянием триггера 14. В режиме «первый воше.т - первый вышел информация с входов 15 переписывается последовательно в регистры 1 от первого к последнему. При этом перепись осуществляется через блоки 2, управляемые сигналами с выходов элементов И 4, если последующий регистр свободен. При поступлении сигнала на вход 16 происходит выдача данных из последнего регистра и сдвиг всего массива данных в сторону последнего регистра. В режиме «последний вощел-первый вышел при записи данных с входов 15 осуществляется занесение их в первый регистр. При записи последующих данных осуществляется сдвиг данных на один регистр в сторону последнего. При чтении данных по сигналам на входе 16 на выход 19 поступают данные из первого регистра и осуществляется сдвиг массива данных на одну порцию в сторону первого регистра 1. Блок 13 осуществляет индикацию по сигналу на входе 17 числа свободных регистров. 3 ил. 77 (Л оо ьо о 00 05 J8

| Магазинное запоминающее устройство | 1979 |

|

SU1026164A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Преобразователь кода во временной интервал | 1981 |

|

SU957429A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-06-30—Публикация

1985-10-08—Подача