Изобретение птносится к вычислите льнорЧ технике и может быть использовано при. разработке электронных вычислительных пашин.

Цель изобретения - повьшение быстродействия „

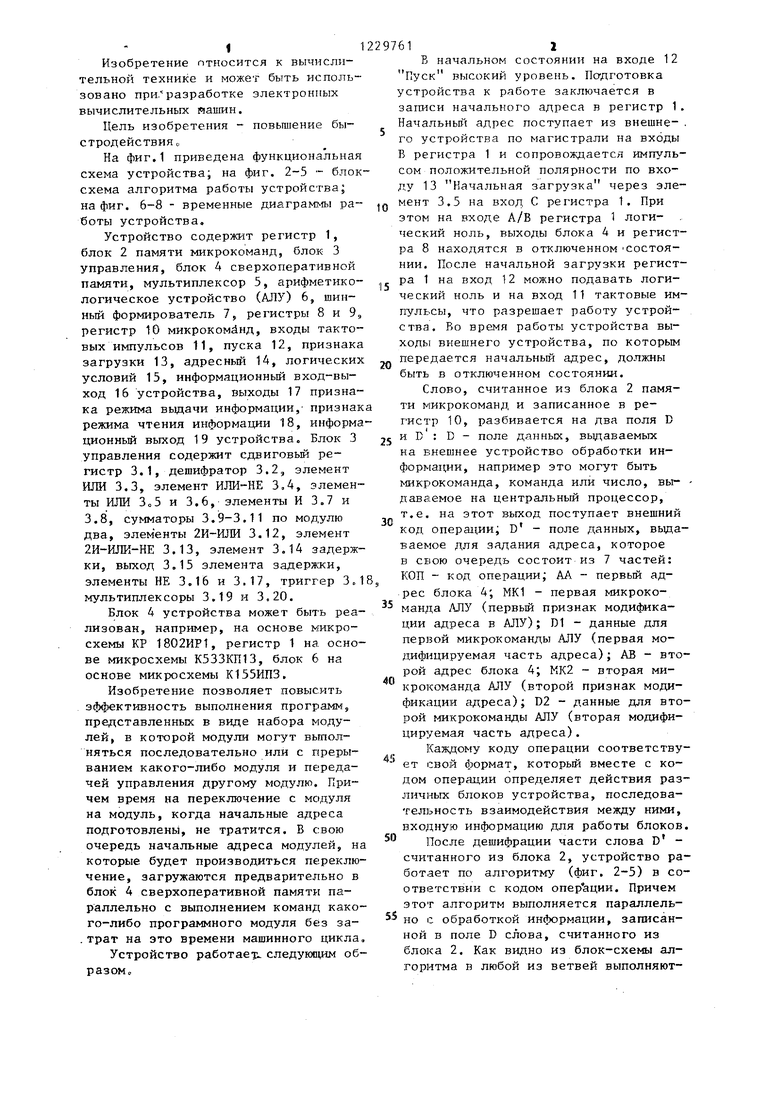

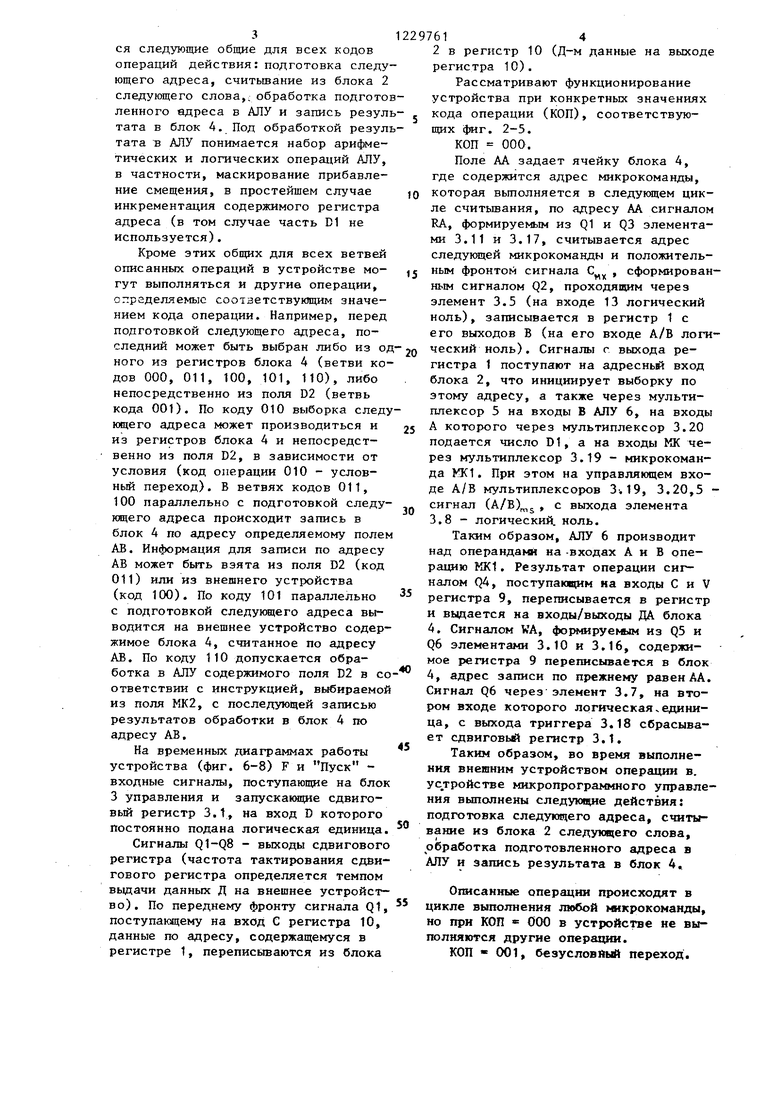

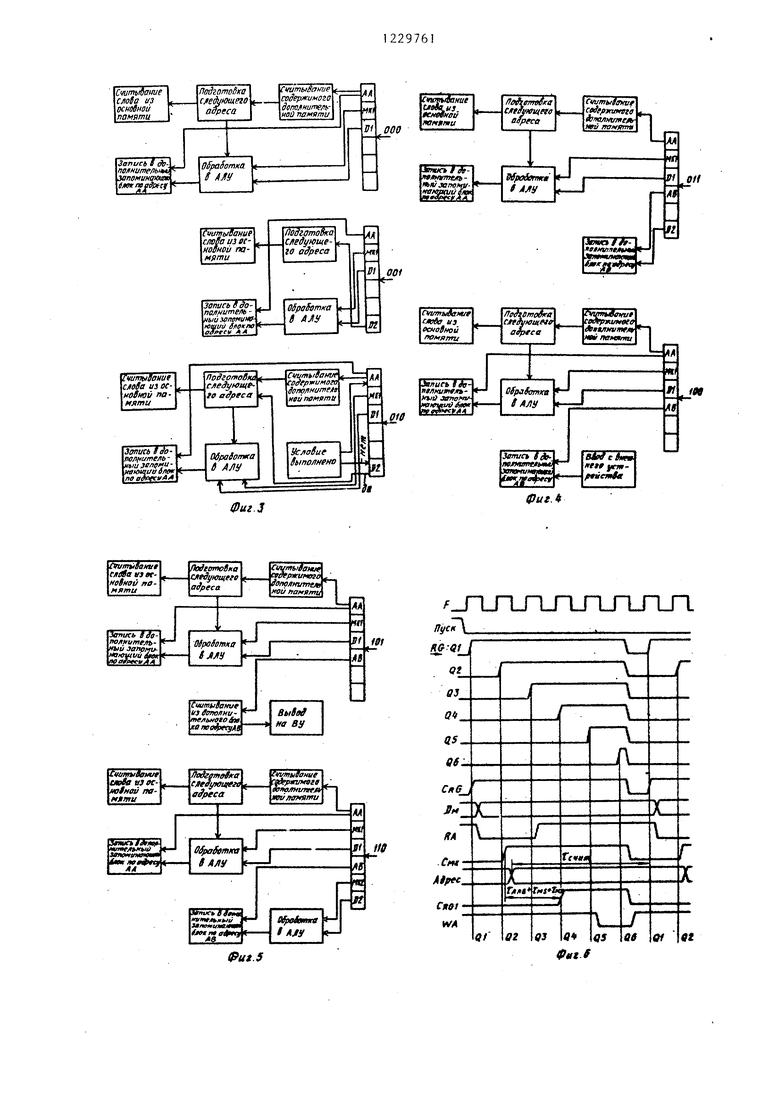

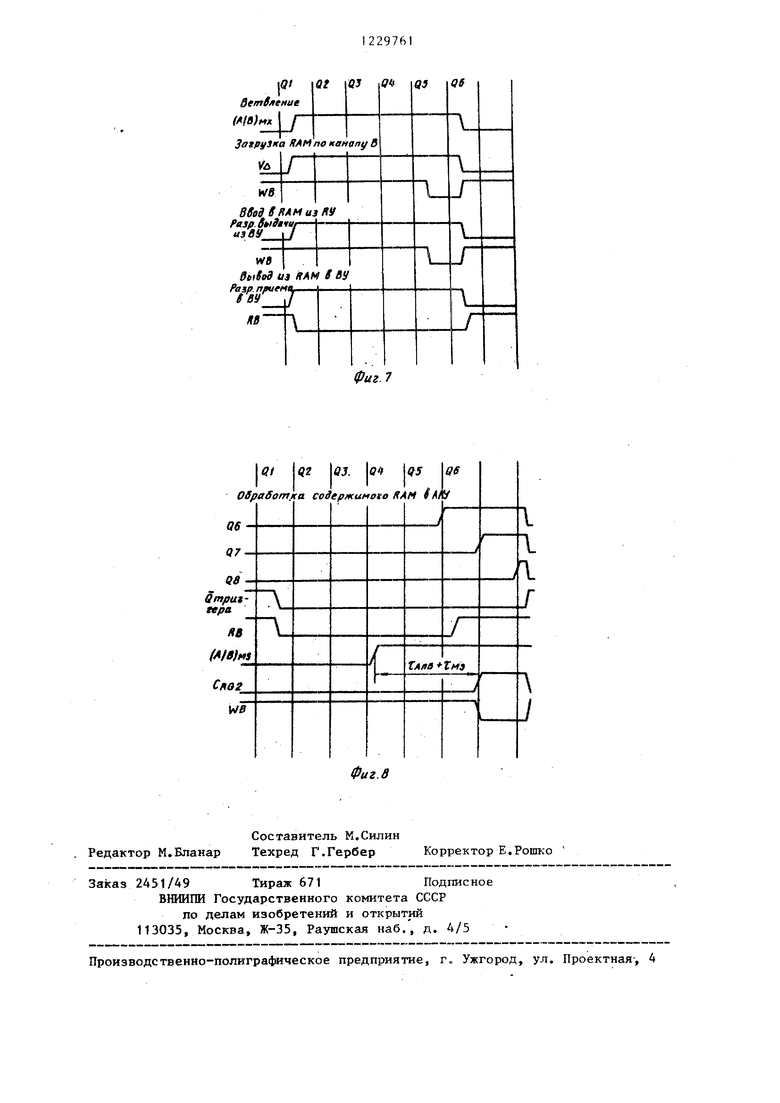

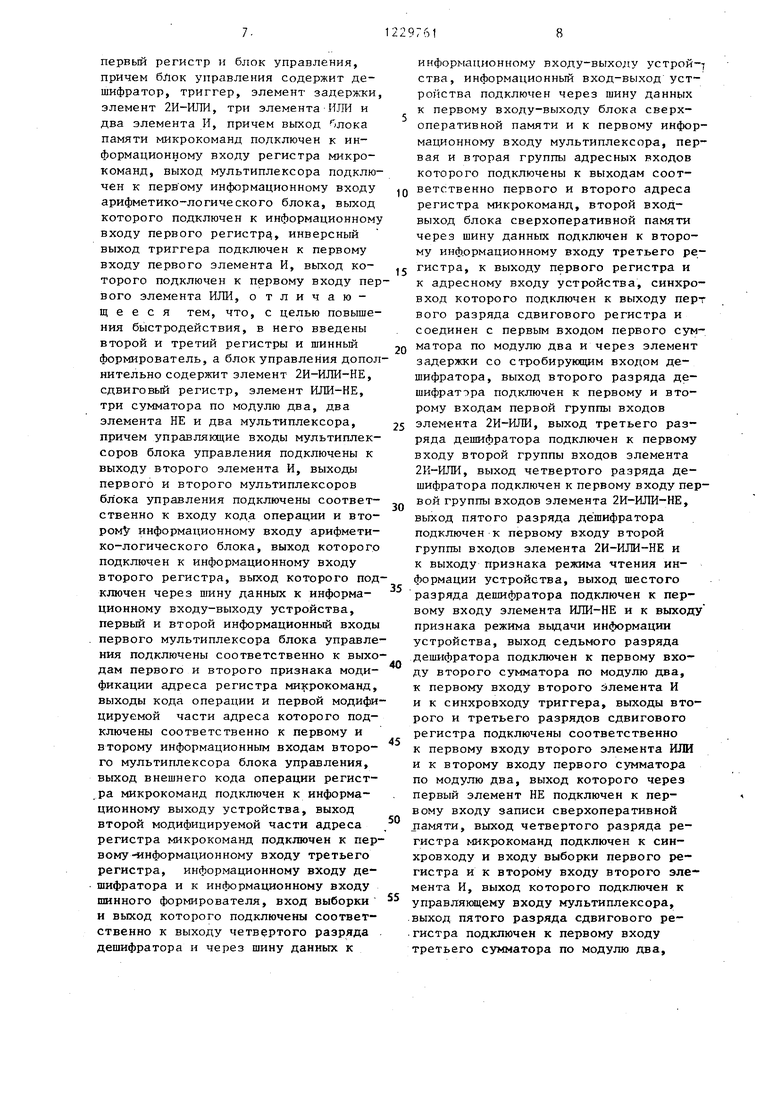

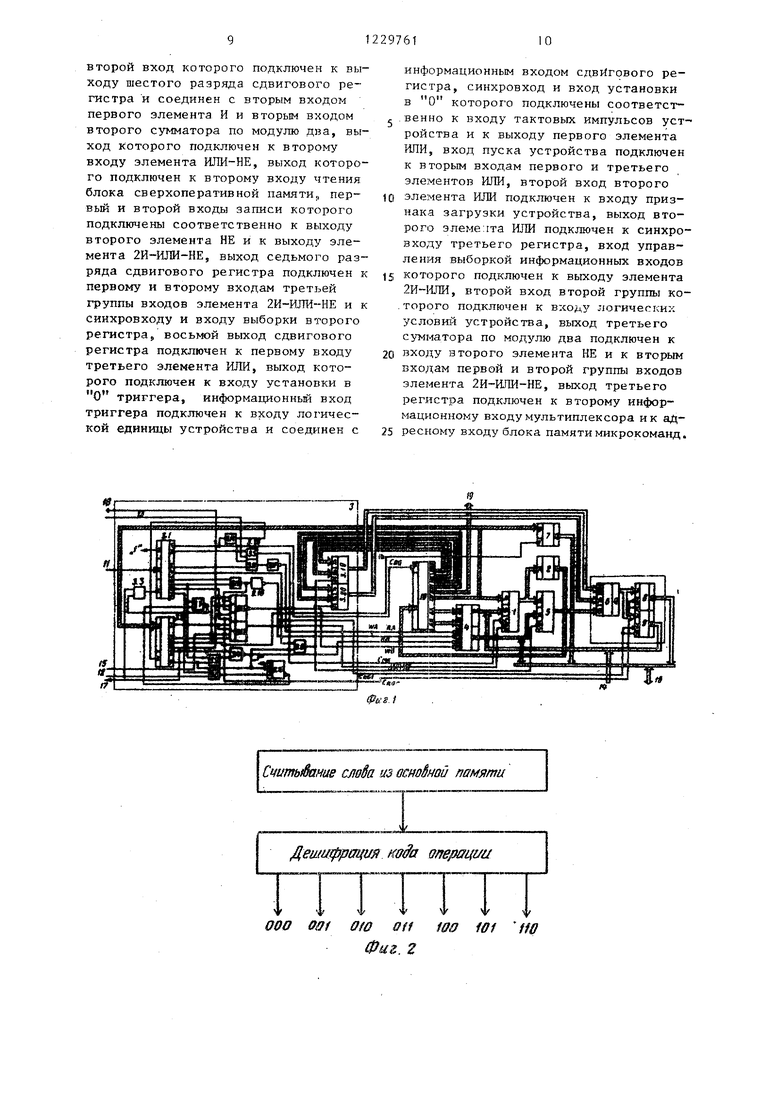

На фиг.1 приведена функциональная схема устройства; на фиг. 2-5 - блок схема алгоритма работы устройства; на фиг. 6-8 - временные диаграммы ра боты устройства,

Устройство содержит регистр 1, блок 2 памяти микрокоманд, блок 3 управления, блок 4 сверхоперативной памяти, мультиплексор 5, арифметико- логическое устройство (АЛУ) 6, шинный формирователь 7 регистры 8 и 9, регистр 10 микрокоманд, входы тактовых импульсов 11, пуска 12, признака загрузки 13, адресньш 14, логических условий 15, информационный вход-выход 16 устройства, выходы 17 признака режима выдачи информации,- признак режима чтения информации 18, информа ционньй выход 19 устройства. Блок 3 управления содержит сдвиговьй регистр 3.1, дешифратор 3.2,, элемент ИЛИ 3.3, элемент ИЛИ-НЕ 3.4, элементы ИЛИ Зо5 и 3,6, элементы И и 3.8, сумматоры 3,9-3.11 по модулю два, элементы 2И-ИЛИ 3.12, элемент 2И-ИЛК-НЕ 3.13, элемент 3,14 задержки, выход 3,15 элемента задержки, элементы НЕ 3,16 и 3,17, триггер ЗЛ мультиплексоры 3.19 н 3.20.

Блок 4 устройства может быть реализован, например, на основе микросхемы КР 1802ИР1, регистр 1 на основе микросхемы K533KII13, блок 6 на основе микросхемы К155ИПЗ.

Изобретение позволяет повысить , эффективность выполнения программ, представленных в виде набора модулей, в которой модули могут выполняться последовательно или с прерыванием какого-либо модуля и передачей управления другому модулю. Причем время на переключение с модуля на модуль, когда начальные адреса подготовлены, не тратится. В свою очередь начальные адреса модулей, на которые будет производиться переключение, загружаются предварительно в блок 4 сверхоперативной памяти параллельно с выполнением команд какого-либо программного модуля без за- . трат на это времени машинного цикла,

Устройство работает следуютщм образом „

5

j

В начальном состоянии на входе 12 Пуск высокий уровень. Подготовка устройства к работе заключается в записи начального адреса в регистр 1. Начальный адрес поступает из внешне- . го устройства по магистрали на входы Б регистра 1 и сопровождается импульсом положительной полярности по входу 13 Начальная загрузка через элемент 3.5 на вход С регистра 1. При этом на входе А/В регистра 1 логический ноль, выходы блока 4 и регистра 8 находятся в отключенном состоянии. После начальной загрузки регистра 1 вход 12 можно подавать логический ноль и на вход 11 тактовые импульсы, что разрешает работу устройства. Во время работы устройства выходы внешнего устройства, по которым

- передается начальный адрес, должны быть в отключенном состоянии.

Слово, считанное из блока 2 памяти микрокоманд и записанное в регистр 10, разбивается на два поля D и Г : D - поле данных, выдаваемых на Ешешнее устройство обработки ин- , например это могут быть микрокоманда, команда или число, вы- - даваемое на центральный процессор, т.е. на этот выход поступает внешний код операции; D - поле данных, вьща- ваемое для задания адреса, которое в свою очередь состоит из 7 частей: КОП - код операции; АЛ - первьш адрес блока 4; МК1 - первая микроко манда (ЛУ (первьй признак модификации адреса в АЛУ); D1 - данные для первой микрокоманды АЛУ (первая модифицируемая часть адреса); АВ - второй адрес блока 4; КК2 - вторая микрокоманда АЛУ (второй признак модификации адреса); D2 - данные для второй микрокоманды АЛУ (вторая модифицируемая часть адреса).

Каж,цому коду операции соответствует свой формат, который вместе с кодом операции определяет действия различных блоков устройства, последовательность взаимодействия между ними, в.ходную информацию для работы блоков, После дешифрации части слова D - считанного из блока 2, устройство работает по алгоритму (фиг. 2-5) в соответствии с кодом опер ации. Причем этот алгоритм выполняется параллельно с обработкой информации, записанной в поле D слова, считанного из блока 2. Как видно из блок-схемы алгоритма в любой из ветвей выполняют0

0

0

5

3

ся следующие общие для всех кодов операций действия: подготовка следующего адреса, считьшание из блока 2 следукицего слова,; обработка подготовленного адреса в АЛУ и запись результата в блок 4. Под обработкой результата та АЛУ понимается набор арифметических и логических операций АЛУ, в частности, маскирование прибавление смещения, в простейшем случае инкрементация содержимого регистра адреса (в том случае часть D1 не используется).

Кроме этих общих для всех ветвей описанных операций в устройстве могут выполняться и другие операции, определяемые соответствующим значением кода операции. Например, перед подготовкой следующего адреса, последний может быть выбран либо из одного из регистров блока 4 (ветви кодов 000, 011, 100, 101, 110), либо непосредственно из поля D2 (ветвь кода 001). По коду 010 выборка следующего адреса может производиться и из регистров блока 4 и непосредственно из поля D2, в зависимости от условия (код операции 010 - условный переход). В ветвях кодов 011, 100 параллельно с подготовкой следующего адреса происходит запись в блок 4 по адресу определяемому полем АВ. Информация для записи по адресу АВ может быть взята из поля D2 (код 011) или из внешнего устройства (код 100). По коду 101 параллельно с подготовкой следующего адреса выводится на внешнее устройство содержимое блока 4, считанное по адресу АВ. По коду 110 допускается обработка в АЛУ содержимого поля D2 в соответствии с инструкцией, выбираемой из поля МК2, с последующей записью результатов обработки в блок 4 по адресу АВ.

На временных диаграммах работы устройства (фиг. 6-8) F и Пуск - входные сигналы, поступающие на блок 3 управления и запускающие сдвиговый регистр 3.1, на вход D которого постоянно подана логическая единица.

Сигналы Q1-Q8 - выходы сдвигового регистра (частота тактирования сдвигового регистра определяется темпом вьщачи данных Д на внешнее устройство). По переднему фронту сигнала Q1, поступающему на вход С регистра 10, данные по адресу, содержащемуся в регистре 1, переписываются из блока

297614

2 в регистр 10 (Д-м данные на выходе регистра 10).

Рассматривают функционирование устройства при конкретных значениях , кода операции (КОП), соответствующих фиг, 2-5.

КОП 000.

Поле АА задает ячейку блока 4, где содержится адрес микрокоманды, JO которая вьтолняется в следукядем цикле считывания, по адресу АА сигналом RA, формируемым из Q1 и Q3 элементами 3.11 и 3.17, считывается адрес следующей микрокоманды и положитель- ( ным фронтом сигнала С , сформированным сигналом Q2, проходящим через элемент 3.5 (на входе 13 логический ноль), записывается в регистр 1 с его выходов В (на его входе А/В логи- 0 ческий ноль). Сигналы г выхода регистра 1 поступают на адресньй вход блока 2, что инициирует выборку по этому адресу, а также через мультиплексор 5 на входы В АЛУ 6, на входы 5 А которого через мультиплексор 3.20 подается число D1, а на входы МК через мультиплексор 3.19 - микрокоманда КК1. При этом на управляющем входе А/В мультиплексоров 3-. 19, 3.20,5 - сигнал (A/B)j, с выхода элемента 3,8 - логический, ноль.

Таким образом, АЛУ 6 производит над операндами на -входах А и В опе- КК1. Результат операции сигналом Q4, поступающим на входы С и V регистра 9, переписывается в регистр и выдается на входы/выходы ДА блока 4. Сигналом КА, формнруекым из Q5 и Q6 элементами 3.10 и 3.16, содержимое регистра 9 переписывается в блок 4, адрес записи по прежнему равен АА. Сигнал Q6 через элемент 3.7, на втором входе которого логическая.единица, с выхода триггера 3.18 сбрасывает сдвиговый регистр 3.1.

Таким образом, во время выполнения внешним устройством операции в, устройстве микропрограммного управления выполнены следуювще действия: подготовка следующего адреса, считывание из блока 2 следующего слова, обработка подготовленного адреса в АЛУ и запись результата в блок 4,

Оггасанные операции происходят в 5 цикле выполнения любой микрокомаиды, но при КОП 000 в устройстве не выполняются другие операщш.

КОП «001, безусловный переход.

5

0

Выход Q1 сдвигового регистра 3.1 через элемент 3.14 задержки, на время установле.ния информации в регистре 10, стробирует дешифратор 3.2. Сигнал со второго выхода дешифратора через элемент 3.12 подается на вход А/В регистра 1 (сигнал (А/В) . фиг.7)

ПП О

Таким образом сигнал С записывает в регистр 1 данные со входов А, т.е. поле D2 - адрес безусловного перехода. В остальном микрокоманда выполняется, как в случае КОП 000.

КОП 010, условный: переход.

Внешнее условие поступает с входа 15 на вход элемента 3.12, другой вхо которого стробируется третьим выходом дешифратора 3,2, при совпадении сигналов (условие выполнено) на входе А/В регистра 1 появляется логи-

ческая 1

что обеспечивает запись

в него поля D2, где записан адрес условного перехода. Если условие не выполнено, запись следующего адреса в регистр 1 происходит с направления В, дальнейшее выполнение микрокоманды аналогично случаю КОП 000.

КОП 011, загрузка блока 4 памяти.

Данные, загружаемые в блок 4, за- писаны в поле D2 микрокоманды, адрес загрузки - в поле АВ.

Сигнал с выхода 4 дешифратора 3,2 (Va, фиг.7) переводит выходы шинного формирователя 7 в активное состояние, а сигнал WB (фиг.7), сформированный на элементе 3.10, через элемент 3.13 подается на вход WB блока 4, что обеспечивает запись данных.

КОП 100, загрузка блока 4 из внешнего устройства.

Адрес загрузки - АВ. Сигнал с пятого выхода дешифратора 3.2 выдается на внешнее устройство по выходу 18 и разрешает ему выдачу информации на вход-выход 16 устройства. Запись информации в блок 4 осуществляется сигналом WB , сформированным на элементах 3.10 и 3.13 (фиг.7).

КОП 101, вьщача данньгк из блока .4 во внешнее устройство.

Адрес выдачи - АВ. Сигнал с шестого выхода дешифратора 3.2 вьщается на внешнее устройство по выходу 17, он же через элемент 3.4 (на втором входе которого логический О) подается на вход RB блока 4 (фиг.7) и инициирует выдачу из него по каналу ДВ на вход-выход 16.

0

,.

5

0

5

Операции для КОП 011, 100, 101 происходят параллельно с обработкой адреса, выполняемой при КОП 000.

КОП 110, обработка в АЛУ содержимого блока 4.

Адрес обрабатываемых данных - АВ, способ обработки в арифметико-логическом блоке МК2, второй операнд - D2 (фиг.8). Операции, описанные для случая КОП 000, связанные с подготовкой следующей микрокоманды, не изменяются, однако цикл выполнения микрокоманды несколько увеличен.

Сигнал с седьмого выхода дешифратора 3.2 передним фронтом взводит D-триггер 3.18, выход Q ко торого запрещает проход через элемент 3.7 сигнала Q6 на сброс сдвигового регистра 3.1. Триггер 3.18 через элемент 3.6 сбрасьшается выходом Q8 сдвигового регистра, и таким образом происходит удлинение цикла микрокоманды. Этот же сигнал с седьмого выхода дешифратора, логически умножаясь на элементе 3.8 с сигналом Q4, переклк1чает мультиплексоры 3.19, 3.20 и 5 (сигнал (А/В) фиг.8). В, этот момент времени обработка в АЛУ б адреса, содержащегося в регистре 1 закончена (за промежуток времени

илБ+L 3 -«x ), а результат обработки переписан в регистр 9. Сигнал с седьмого выхода дешифратора через элементы 3.9 и 3.4 подается на вход 1УЗ блока 4 и обеспечивает считывание из него по адресу АВ в канал ДВ до момента времени Q6.

Таким образом на входы А и В АЛУ подаются входные данные, на вход МК - микрокоманда. Интервал времени на переключение мультиплексоров и работу арифметико-логического блока обозначен (фиг.8). Сигналом Q7 (Ср,,, , фиг.8) результат операции переписывается в регистр 8, с выхода которого сигналом WB, сформированным сигналом Q7, проходящим через элемент 3.13, он переписывается в блок 4. На этом выполнение микрокоманды заканчивается.

Формула изобрет ения

Микропрограммное вычислительное устройство, содержащее блок памяти микрокоманд, блок сверхоперативной памяти, регистр микрокоманд, мультиплексор, арифметико-логический блок.

первый регистр н блок управления, причем блок управления содержит дешифратор, триггер, элемент задержки элемент 2И-ИЛИ, три элемента ИЛИ и два элемента И, причем выход шока памяти микрокоманд подключен к информационному входу регистра микрокоманд, выход мультиплексора подключен к перв ому информационному входу арифметико-логического блока, выход которого подключен к информационном входу первого регистра, инверсный выход триггера подключен к первому входу первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в него введены второй и третий регистры и шинный формирователь, а блок управления дополнительно содержит элемент 2И-ИЛИ-НЕ, сдвиговый регистр, элемент ИЛИ-НЕ, три сумматора по модулю два, два элемента НЕ и два мультиплексора, причем управляющие входы мультиплексоров блока управления подключены к выходу второго элемента И, выходы первого и второго мультиплексоров блока управления подключены соответ

ственно к входу кода операции и второму информационному входу арифметико-логического блока, выход которого подключен к информационному входу второго регистра, выход которого подключен через шину данных к информа ционному входу-выходу устройства, первый и второй информационный входы первого мультиплексора блока управления подключены соответственно к выходам первого и второго признака модификации адреса регистра микрокоманд, выходы кода операции и первой модифицируемой части адреса которого подключены соответственно к первому и

второму информационным входам второго мультиплексора блока управления, выход внешнего кода операции регистра микрокоманд подключен к информационному выходу устройства, выход второй модифицируемой части адреса регистра микрокоманд подключен к первому -информационному входу третьего регистра, информационному входу дешифратора и к информационному входу шинного формирователя, вход выборки и выход которого подключены соответственно к выходу четвертого разряда дешифратора и через шину данных к

15

.Q -25 35

30

40

45

.

информационному входу-выходу устрой- ства, информационный вход-выход устройства подключен через шину данных к первому входу-выходу блока сверхоперативной памяти и к первому информационному входу мультиплексора, первая и вторая группы адресных входов которого подключены к выходам соответственно первого и второго адреса регистра микрокоманд, второй вход- выход блока сверхоперативной памяти через шину данных подключен к второму информационному входу третьего регистра, к выходу первого регистра и к адресному входу устройства, синхро- вход которого подключен к выходу перт вого разряда сдвигового регистра и соединен с первым входом первого сумматора по модулю два и через элемент задержки со стробирующим входом дешифратора, выход второго разряда дешифратора подключен к первому и второму входам первой группы входов элемента 2И-ИЛИ, выход третьего разряда дешифратора подключен к первому входу второй группы входов элемента 2И-ИЛИ, выход четвертого разряда дешифратора подключен к первому входу первой группы входов элемента 2И-ИЛИ-НЕ, выход пятого разряда дешифратора подключен к первому входу второй группы входов элемента 2И-ИЛИ-НЕ и к выходу признака режима чтения информации устройства, выход шестого разряда дешифратора подключен к первому входу элемента ИЛИ-НЕ и к выходу признака режима вьщачи информации устройства, выход седьмого разряда дешифратора подключен к первому входу второго сумматора по модулю два, к первому входу второго элемента И и к синхровходу триггера, выходы второго и третьего разрядов сдвигового регистра подключены соответственно к первому входу второго элемента ИЛИ и к второму входу первого сумматора по модулю два, выход которого через первый элемент НЕ подключен к первому входу записи сверхоперативной 11амяти, выход четвертого разряда регистра микрокоманд подключен к син- хровходу и входу выборки первого регистра и к второму входу второго элемента И, выход которого подключен к управлякяцему входу мультиплексора, выход пятого разряда сдвигового ре- .гистра подключен к первому входу третьего сумматора по модулю два.

второй вход которого подключен к выходу шестого разряда сдвигового регистра и соединен с вторым входом первого элемента И и вторым входом второго сумматора по модулю два, выход которого подключен к второму входу элемента ИЛИ-НЕ, выход которого подключен к второму входу чтения блока сверхоперативной памяти,, пер- вьй и второй входы записи которого подклкгчень соответственно к выходу второго элемента НЕ и к выходу элемента 2И-ИЛИ-НЕ, выход седьмого разряда сдвигового регистра подключен к первому и второму входам третьей группы входов элемента 2И-ИЛИ-НЕ и к синхровходу и входу выборки второго регистра;, восьмой выход сдвигового регистра подключен к первому входу третьего элемента ИЛИ, выход которого подключен к входу установки в О триггера, информационный вход триггера подключен к входу логической единицы устройства и соединен с

информационным входом сдвигового регистра, синхровход и вход установки в О которого подключены соответст- венно к входу тактовых импульсов устройства и к выходу первого элемента ИЛИ, вход пуска устройства подключен к вторым входам первого и третьего элементов ИЛИ, второй вход второго

элемента ИЛИ подключен к входу признака загрузки устройства, выход второго элемента ИЛИ подключен к синхровходу третьего регистра, вход управления выборкой информационных входов

которого подключен к выходу элемента , второй вход второй группы ко- торого подключен к входу логических условий устройства, выход третьего сумматора по модулю два подключен к

входу второго элемента НЕ и к вторым входам первой и второй группы входов элемента 2И-ИЛИ-НЕ, выход третьего регистра подключен к второму информационному входу мультиплексора и к аДресному входу блока памяти микрокоманд.

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обработки нечеткой информации | 1990 |

|

SU1758642A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Генератор тестовых воздействий | 1987 |

|

SU1439564A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Устройство обработки данных процессора | 1988 |

|

SU1647584A1 |

| Процессор параллельной обработки | 1990 |

|

SU1797126A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Операционное устройство микропроцессорной вычислительной системы | 1982 |

|

SU1198532A1 |

Изобретение относится к вычислительной технике и может быть использовано при разработке устройств управления ЭВМ. Целью изобретения является повьшение быстродействия. Устройство содержит три регистра, блок памяти микрокоманд, блок управления, блок сверхоперативной памяти, мультиплексор, арифметико-логическое устройство, регистр микрокоманд. Сущность Изобретения заключается в повышении быстродействия за счет параллельного вычисления начальных адресов модулей подпрограмм и загрузки их в сверхоперативную память. 8 ил. (Л с ю ts9 СО о

СчитьЛание сло§а из оснобиой памяти

ооо ОО1 ош Off igs wi ffo

i&. 2

он

Фиг.З

(ut.S

фиг. 4t

W

jnJTJ jnJlJ-LriJT

Фвг S

Составитель М.Силин Редактор М.Бланар Техред Г.Гербер Корректор Е.Роппсо

Заказ 2А51/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г„ Ужгород, ул. Проектная-, 4

| Устройство для управления и микродиагностики | 1981 |

|

SU968815A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Микропрограммное вычислительное устройство | 1981 |

|

SU1008741A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-07—Публикация

1984-08-03—Подача