1

Изобретение относится к ш тельной технике и может &ыть зовано при построении устроймирования адресов команд и д двухадресных универсальных и лизированных цифровых вычисл машинах.

Целью изобретения являетсрение области применения за вышения гибкости адресации сративной памяти при хранении различного формата.

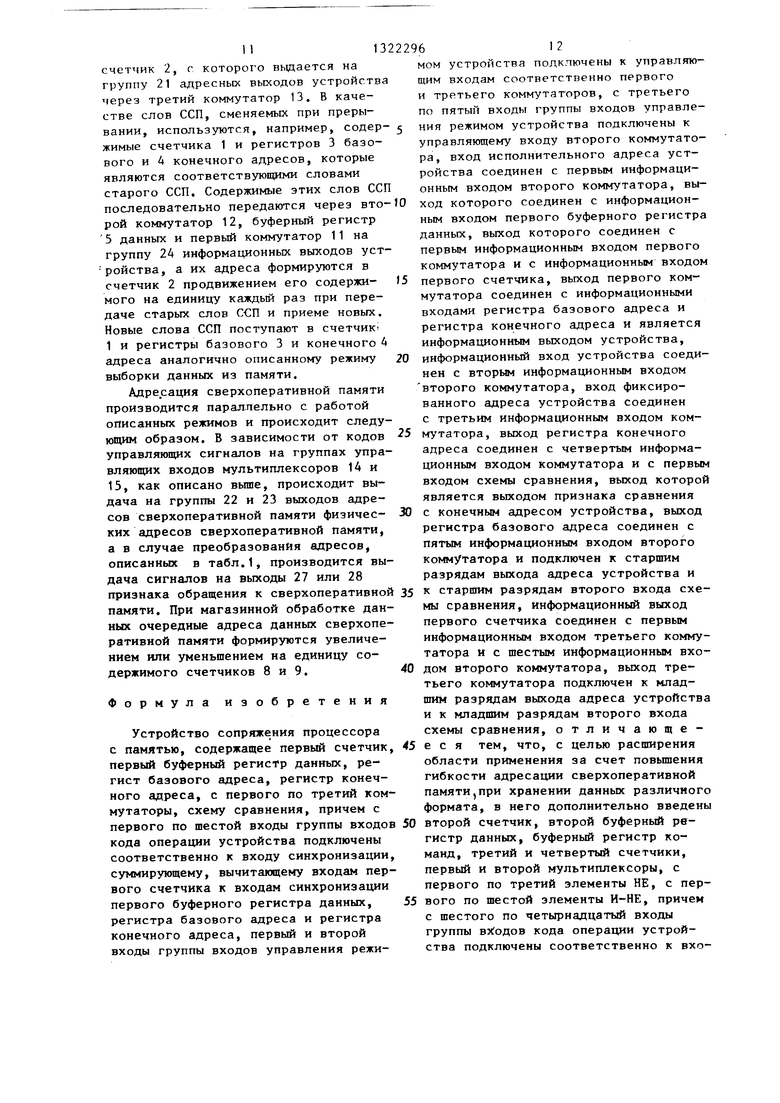

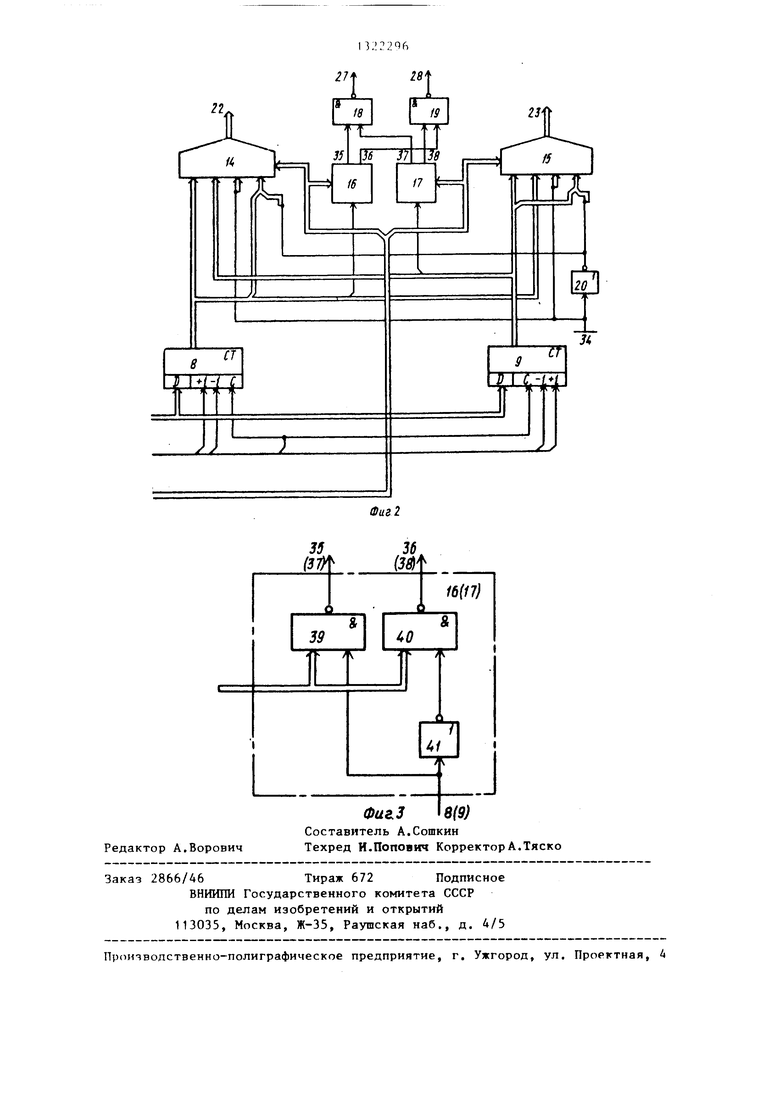

На фиг.1 и 2 представлена турная схема устройства; на структурная схема вьтолнения признака обращения к сверхопной памяти.

Устройство для формирования адресов памяти двухадресной ЦВМ (фиг,1 и 2) содержит первый и второй счетчики 1 и 2, регистры базового 3 и конечного А адресов, первый 5 и второй 6 буферные регистры данных, буферный регистр 7 команд, третий 8 и четвер- тый 9 счетчики, схему 10 сравнения, первый 11, второй 12 и третий 13 коммутаторы, первый 14 и второй 15 мультиплексоры, первый 16 и второй 17 блоки признака обращения к сверхопе- ративной памяти, первый 18 и второй 19 элементы И-НЕ, первый элемент НЕ 20, Кроме того, на фиг, 1а и lEi обозначены: группа 21 адресных выходов устройства, группы 22 и 23 выходов соответственно первого и второго адресов сверхоперативной памяти, группы 24 и 25 выходов соответственно информации и команд устройства, выход

Счетчик 1 предназначен для адресации последовательности командных слов и формирования адреса очередной команды путем увеличения на единицу содержимого счетчика 1 при естественном следовании команд, либо путем изменения состояния счетчика 1 адреса команд при выполнении команд передачи управления и при смене слова состояния программы (ССП) в прерываниях программе Занесение новой информации в счетчик 1 происходит при подаче синхросигнала на синхровход С счетчика 1, причем информация в счетчик 1 заносится с выходов первого буферного регистра 5 данных. Увеличение содержимого счетчика 1 на единицу происходит при подаче сигнала на его вход +1 суммирования, а при подаче сигнала на вход -1 вычитания счетчика 1 его содержимое уменьшается на единицу. Поскольку выборка очередной команды производится в процессе выполнения текущей команды, то состояние счетчика 1 после вьтолнения текущей команды на единицу превьш1ает но- 35 мер (адрес) очередной команды. Поэтому перед запоминанием старого ССП содержимое счетчика 1 должно уменьшаться на единицу. Изменение содержимого счетчика 1 происходит по переднему

26 признака сравнения с конечным ад- 40 j.

„ „ фронту сигналов, подаваемых на его

ресом устройства, первый 27 и второй и.и и ii

входы 9 или 1 ,

28 выходы устройства признака обращения к сверхоперативной памяти, группы 29-31 входов соответственно исполнительных адресов, данных и фикси- обработке массивов данных или слов рованных адресов устройства, группа увеличенного формата формирование оче- 32 входов управления устройства, груп- группа 33 входа кода операции устройства, шина 34 нулевого потенциала.

Счетчик 2 предназначен для формирования адресов данных, причем при

редных адресов данных или частей слов увеличенного формата производится увеличением или уменьшением на единицу сопервый 35 и второй 36 выходы первого 0 Держимого счетчика 2, Работа счетчика

блока 16 признака обращения к сверхоперативной памяти, первый 37 и второй 38 выходы второго блока 17 признака обращения к сверхоперативной памяти.

Первый блок 16 признака обращения к сверхоперативной памяти (фиг,3) содержит третий 39 и четвертый 40 э:де- менты И-НЕ, выходы которых образуют

2 производится аналогично описанной работе счетчики 1.

Регистр 3 базового адреса предназначен для разделения объема памяти на отдельные базовые области, объем которых определяется разрядностью группы выходов третьего коммутатора 13 или счетчиков 1 и 2, Таким образом, суммарная разрядность группы

5

0 5 0

cociTnt TCTBCHHo nepBbiif 35 и второй ЗЬ вьгхпды блока И), и второй элемент HF. А1. Структура второго блока признака обращения к сверхоперативной памяти аналогична первом .

Перед описанием работы устройства в целом опишем назначение и работу отдельных его узлов и блоков.

Счетчик 1 предназначен для адресации последовательности командных слов и формирования адреса очередной команды путем увеличения на единицу содержимого счетчика 1 при естественном следовании команд, либо путем изменения состояния счетчика 1 адреса команд при выполнении команд передачи управления и при смене слова состояния программы (ССП) в прерываниях программе Занесение новой информации в счетчик 1 происходит при подаче синхросигнала на синхровход С счетчика 1, причем информация в счетчик 1 заносится с выходов первого буферного регистра 5 данных. Увеличение содержимого счетчика 1 на единицу происходит при подаче сигнала на его вход +1 суммирования, а при подаче сигнала на вход -1 вычитания счетчика 1 его содержимое уменьшается на единицу. Поскольку выборка очередной команды производится в процессе выполнения текущей команды, то состояние счетчика 1 после вьтолнения текущей команды на единицу превьш1ает но- 5 мер (адрес) очередной команды. Поэтому перед запоминанием старого ССП содержимое счетчика 1 должно уменьшаться на единицу. Изменение содержимого счетчика 1 происходит по переднему

0 j.

обработке массивов данных или слов увеличенного формата формирование оче-

Счетчик 2 предназначен для формирования адресов данных, причем при

обработке массивов данных или слов увеличенного формата формирование оче-

редных адресов данных или частей слов увеличенного формата производится увеличением или уменьшением на единицу Держимого счетчика 2, Работа счетчика

2 производится аналогично описанной работе счетчики 1.

Регистр 3 базового адреса предназначен для разделения объема памяти на отдельные базовые области, объем которых определяется разрядностью группы выходов третьего коммутатора 13 или счетчиков 1 и 2, Таким образом, суммарная разрядность группы

21 адресных выходов устройства равна сумме разрядностей выхода третьего коммутатора 13 и регистра 3 базового адреса. Поэтому адресация каждой указанной базовой области памяти осуще- ствляется так, что после максимального адреса ячейки этой области (например, при продвижении адресов области) в счетчиках 1 и 2 указьтается начальный адрес ячейки этой же области, а не начальный адрес следующей по порядку базовой области. Доступность записи в регистр 3 базового адреса только операционной системе обеспечивает не только распределение неза- висимых областей памяти различным подзадачам, но обеспечивает также защиту памяти одних подзадач от вмешательства со стороны других. Запись

информации в регистр 3 базового адре-20 мутатор 11. Запись информации в буса осуществляется с выходов первого коммутатора 11 по заднему фронту синхросигнала на синхровходе С регистра 3.

ферный регистр 7 команд производится по заднему фронту синхросигнала, подаваемого на синхровход С регистра 7 только в моменты выборки командного

Регсйтр 4 конечного адреса предна-25 слова. Содержимое буферного регистра

7 команд делится на три поля: поле кодов операций, вьодаваемое на группу 25 выходов команд устройства, и поля

значен для задания конечного адреса подпрограммы, по достижении которой устройство должно вьфабатывать управляющий сигнал, например, в систему прерьшания процессора. Разрядность 30 регистра А конечного адреса равна суммарной разрядности регистра 3 базового адреса и группы выходов третьего коммутатора 13.

Запись информации в регистр 4 ба- 35 для сравнения кодов адреса памяти, зового адреса, подаваемой на его сформированного на группе 21 адрес- группу информационных входов D с группы информационных выходов первого

R, и R для адресации сверхоперативной памяти - РОН, подаваемые на груп пы информационных входов D счетчиков 8 и 9 и второго адреса сверхоператив ной памяти.

Схема 10 сравнения предназначена

ных выходов устройства, и конечного адреса программы или адреса необходи мой ячейки памяти, хранящей данные, заданного в регистре 4 конечного адреса, и дпя выработки сигнала, подаваемого на выход 26 признака сравнения с конечным адресом устройства пр совпадении этих адресов.

коммутатора 11, осуществляется по заднему фронту синхросигнала, подаваемого на синхровход С регистра 4,

Буферные регистры 5 и 6 данных выполнены в виде регистров-защелок, используемых для временного хранения 5 информации. Для их построения могут быть использованы, например, микросхемы типа 583ВАЗ. Передача информации с входов на выходы этих регистров производится при подаче сигнала на их синхровходы, а запоминание (защелка) информации осуществляется в момент снятия сигнала на синхровходах буферных регистров 5 и 6 данных. Назначение этих регистров следует из 55 дальнейшего описания работы устройства.

Применение двух буферных регистров 5 и 6 данных обусловлено двумя причинами. Во-первых, обеспечиваетгя прием информации, поступающей на информапд - онные входы второго коммутатора 12 от различных источников в различное время и, во-вторых, дпя увеличения производительности обеспечивается совмещение во времени хранения информации, например, в регистре 6 для выдачи на выходы первого коммутатора 11, а в регистре 5 - для выдачи на информационные входы счетчиков 1 и 2. Буферный регистр 7 команд предназначен для приема командного слова в момент его выборки по содержимому счетчика 1 и поступающего в буферный регистр 7 команд с группы 30 входов данных устройства соответственно через второй коммутатор 12, второй буферный регистр 6 данных и первый комферный регистр 7 команд производится по заднему фронту синхросигнала, подаваемого на синхровход С регистра 7 только в моменты выборки командного

слова. Содержимое буферного регистра

7 команд делится на три поля: поле кодов операций, вьодаваемое на группу 25 выходов команд устройства, и поля

R, и R для адресации сверхоперативной памяти - РОН, подаваемые на группы информационных входов D счетчиков 8 и 9 и второго адреса сверхоперативной памяти.

Схема 10 сравнения предназначена

для сравнения кодов адреса памяти, сформированного на группе 21 адрес-

ных выходов устройства, и конечного адреса программы или адреса необходимой ячейки памяти, хранящей данные, заданного в регистре 4 конечного адреса, и дпя выработки сигнала, пода , ваемого на выход 26 признака сравнения с конечным адресом устройства при совпадении этих адресов.

Первый коммутатор 11 предназначен для вьщачи информации на группу 24 выходов данных устройства и группы информационных входов D регистров базового 3 и конечного 4 адреса и буферного регистра 7 команд с выходов буферных регистров 5 или 6 данных под управлением сигнала на управляющем входе коммутатора 11.

Второй коммутатор 12 в зависимости от кода управления, подаваемого на его группу управляющих входов, осуществляет передачу информации на группы информационных входов первого

5 и второго 6 буферных регистров данных со следующих источников: с г рупп информационных выходов счетчика 1 и регистров 3 базового и 4 конечного адресов и с групп входов исполнитель- ньк адресов 29, данных 30 и фиксированных 31 адресов устройства.

Третий коммутатор 13 предназначен для выдачи информации с выходов счетчика 1 или счетчика 2 на группу 21 адресных выходов устройства и вторую группу входов блока 10 сравнения под управлением сигнала на управляющем входе третьего коммутатора 13,

Первый и второй мультиплексоры 14 и 15 предназначены для:

-передачи кодов адресов сверхоперативной памяти с выходов счетчиков

8 и 9 на группы вькодов соответственно первого 22 и второго 23 адресов сверхоперативной памяти (передача кодов сщресов через первые информационные входы мультиплексоров 14 и 15);

-осуществления рокировки указанных адресов, т.е. передачи кодов ад- ресов со счетчика 8 (9) на группу выходов 23 второго (22 первого) адреса сверхоперативной памяти, т.е. передача кодов через вторые группы информационных входов мультиплексоров 14 и 15;

-выдачи фиксированного адреса нулевой ячейки сверхоперативной памяти, путем передачи нулевого кода с шины

34 нулевого потенциала через третьи группы информационных входов мультиплексоров 14 и 15 на группы выходов

Выход 28

22 первого и 23 второго адреса сверхоперативной памяти (использование ячейки сверхоперативной памяти с фиксированным нулевым адресом позволяет увеличить число адресуемых ячеек в |0дной команде без расширения формата командного слова, например, полем Р 3, что привело бы к значительному увеличению объемов памяти программ и недоиспользованию ее объемов при размещении команд, в которых поле Р 3 не используется);

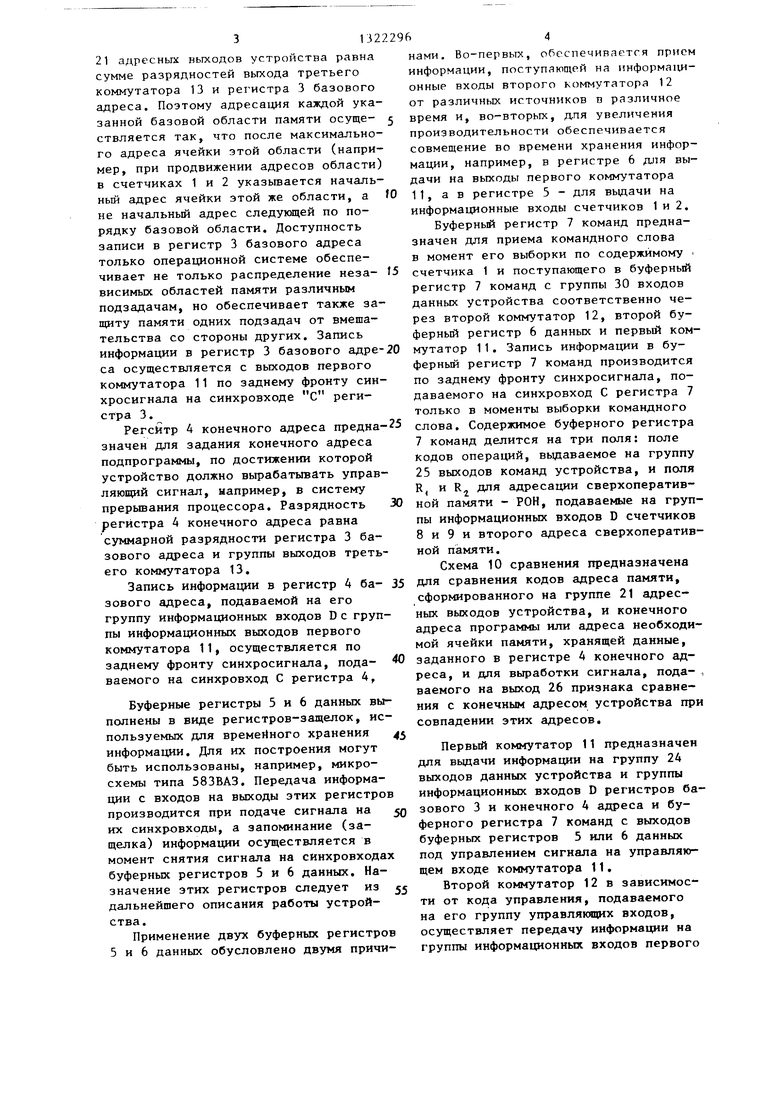

- преобразования кодов адресов, хранимых в счетчиках 8 и 9 в физические адреса оперативной памяти для уплотнения расположения в них различных кодов по закону, который поясняется табл.1, т.е. передача кодов через четвертые группы информационных входов мультиплексоров 14 и 15 таким образом, что через их первый и второй разряды передаются константы 11, а через третий и четвертый разряды - соответственно содержимое второго и третьего разрядов счетчиков 8 и 9. При этом состояние младшего четвертого разряда счетчиков 8 и 9 определяет, какая из половин сверхоперативной памяти должна возбуждаться при обращении. Табл.2 иллюстрирует пример заполнения сверхоперативной памяти при отсутствии средств уплотнения в ней данных, а тйбл,3 - при наличии таких средств (мультиплексоры 14 и 15, блоки 16 и 17 признаков обращения к сверхоперативной памяти и элементы

И-НЕ 18 и 19),

I

Таблица 1

Выход 27

71322296

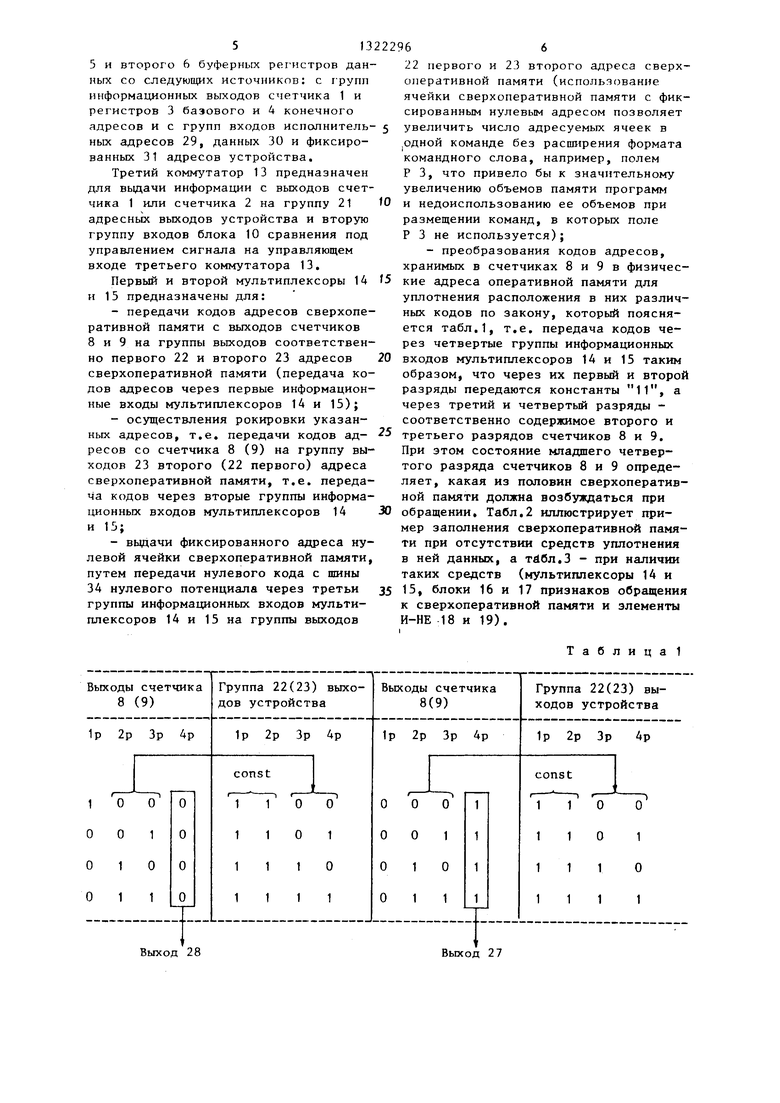

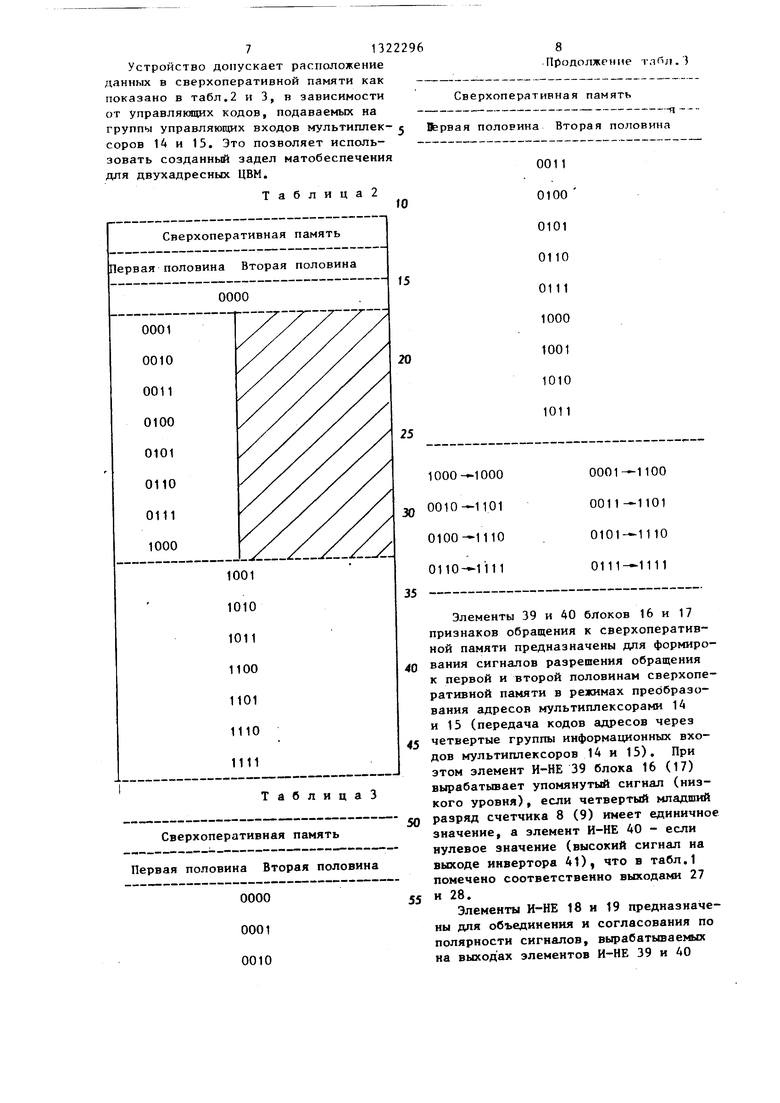

Устройство допускает расположение данных в сверхоперативной памяти как показано в табл.2 и 3, в зависимости от управляющих кодов, подаваемых на группы управляющих входов мультиплек- с соров 14 и 15. Это позволяет использовать созданный задел матобеспечения для двухадресных ЦВМ.

Таблица2

10

Сверхоперативная память

Первая половина Вторая половина 0000

ТаблицаЗ

Сверхоперативная память

т..в..

Первая половина Вторая половина

0000 0001 0010

8 Продолжение тлПл.)

Сверхоперативная память

ч - 1Ьрвая половина Вторая половина

ООП

0100

0101

0110

0111

1000

1001

1010

1011

25

1000-1000

0110- 1111

0001-1100 0011 -1101 0101-1110 0111-1111

35

5

0

5

0

Элементы 39 и 40 блоков 16 и 17 признаков обращения к сверхоперативной памяти предназначены для формирования сигналов разрешения обращения к первой и второй половинам сверхоперативной памяти в режимах преобразования адресов мультиплексорами 14 и 15 (передача кодов адресов через четвертые группы информационных входов мультиплексоров 14 и 15). При этом элемент И-НЕ 39 блока 16 (17) вырабатывает упомянутый сигнал (низкого уровня), если четвертый младший разряд счетчика 8 (9) имеет единичное значение, а элемент И-НЕ 40 - если нулевое значение (высокий сигнал на выходе инвертора 41), что в табл.1 помечено соответственно выходами 27 и 28.

Элементы И-НЕ 18 и 19 предназначены дпя объединения и согласования по полярности сигналов, вырабатываемых на выходах элементов И-НЕ 39 и 40

(первых 35 и 37 и вторьк ЧЬ и J8 выходах блоков 16 и 17) и вьщгрщ этих сигналов на выходы 27 и 28 устрой- ства для выработки признаков обращения к соответствующим половинам сверх оперативной памяти в моменты преобразования мультиплексорами 14 и 15 кодов адресов, хранимых в счетчиках 8 и 9, в физические адреса сверхоперативной памяти..

Элемент НЕ 20 предназначен для выработки единичного потенциала const 1 на первом и втором разрядах четвертых групп информационных входов мультиплексоров 14 и 15.

Рассмотрим функционирование устройства.

В режиме выборки команды устройство работает следующим образом. Со- 20 держимое счетчика 1, указывающее адрес очередной команды, через третий коммутатор 13 передается на группу 21 адресных выходов устройства, на которую старшая часть адреса (номер страницьО вьщается с выходов регистра 3 базового адреса. Командное слово с выходов памяти через группу 30 входов данных устройства и второй коммутатор 12 подается на второй буферный ре- ЗО гистр 6 данных и запоминается в нем по сигналу, поступающему на синхро- вход регистра 6. Далее командное слово через первый коммутатор 11 подает(операнд 1) не записывается в буферный регистр 7 команд, а выдается на группу 24 выходов данных устройства. В режиме выборки данных из памяти устройство работает следующим образом. Исполнительный адрес с группы 29 входов исполнительных адресов устройства через второй коммутатор 12 и первьм буферный регистр 5 данных заносится в счетчик 2 о Этот адрес через третий коммутатор 13 подается на группу 21 адресных выходов устройства, а информация памяти, соответствующая данному адресу, через группу 30 входов данных устройства и второй коммутатор 12 заносится в первый 5 и второй 6 буферные регистры. Далее, в зависимости от типа исполняемой команды, данная информация может быть записана в счетчик 1 (в командных пе- редачи управления), либо подаваться на выход первого коммутатора 11 для выдачи на группу 24 выходов данных устройства дли для записи в регистры базового 3 или конечного 4 адреса. Если обработке подлежат массивы данных, адрес очередного слова которых на единицу больше (меньше) текущего адреса, то после выборки очередного слова данных происходит увеличе- ся на информационные входы буферного /-

« j-f i- j5 (уменьшение) на единицу содержирегистра 7 команд и запоминается в нем по синхросигналу, поступающему на синхровход регистра 7. Выборка очередного командного слова производится в конце выполнения очередной 40 команды, поэтому перед выполнением очередной команды код операции команды с выходов буферного регистра 7 команд подается на группу 23 выходов команд устройства, а поля R, и R 45 команды для адресации сверхоперативной памяти по сигналу, поступающему на синхровходы С счетчиков 8 и 9, записываются в эти счетчики. После выборки командного слова содержимое зо счетчика 1 увеличивается на единицу. Если команда имеет короткий формат, например RR, то на этом выборка ко мандного слова заканчивается, а если дан - длинный формат, например, RX 55 или RI, происходит выборка соответственно смещения или непосредственного операнда I аналогично выборке команды, после чего содержимое счетчимого счетчика 2 и очередное слово выбирается аналогично описанному.

На протяжении всего времени работы устройства блок 10 сравнения сравнивает адрес, вьщаваемый устройством на группу 21 адресных выходов, с содержимым регистра 4 конечного адреса и при их равенстве формирует сигнал на управляющем выходе 26 устройства. По этому сигнешу может быть остановлена работа устройства, например, при отладке программ, или устройство перейдет к прерывающей подпрограмме.

В режим смены ССП при выходе на прерьтание программы по окончании исполнения очередной команды устройство работает следующим образом. Фиксированный адрес зоны хранения старых и новых ССП соответствующего класса прерывания подается через группу 31 входов фиксированных адресов устроит ства, второй коммутатор 12, буферный регистр 5 данных и записывается в

ка 1 также увеличнвает(;я на единицу. Отличие выборки смешения или непосредственного операнда от выборки ко

1

5

0 О

(операнд 1) не записывается в буферный регистр 7 команд, а выдается на группу 24 выходов данных устройства. В режиме выборки данных из памяти устройство работает следующим образом. Исполнительный адрес с группы 29 входов исполнительных адресов устройства через второй коммутатор 12 и первьм буферный регистр 5 данных заносится в счетчик 2 о Этот адрес через третий коммутатор 13 подается на группу 21 адресных выходов устройства, а информация памяти, соответствующая данному адресу, через группу 30 входов данных устройства и второй коммутатор 12 заносится в первый 5 и второй 6 буферные регистры. Далее, в зависимости от типа исполняемой команды, данная информация может быть записана в счетчик 1 (в командных пе- редачи управления), либо подаваться на выход первого коммутатора 11 для выдачи на группу 24 выходов данных устройства дли для записи в регистры базового 3 или конечного 4 адреса. Если обработке подлежат массивы данных, адрес очередного слова которых на единицу больше (меньше) текущего адреса, то после выборки очередмого счетчика 2 и очередное слово выбирается аналогично описанному.

На протяжении всего времени работы устройства блок 10 сравнения сравнивает адрес, вьщаваемый устройством на группу 21 адресных выходов, с содержимым регистра 4 конечного адреса и при их равенстве формирует сигнал на управляющем выходе 26 устройства. По этому сигнешу может быть остановлена работа устройства, например, при отладке программ, или устройство перейдет к прерывающей подпрограмме.

В режим смены ССП при выходе на прерьтание программы по окончании исполнения очередной команды устройство работает следующим образом. Фиксированный адрес зоны хранения старых и новых ССП соответствующего класса прерывания подается через группу 31 входов фиксированных адресов устроит ства, второй коммутатор 12, буферный регистр 5 данных и записывается в

счетчик 2, г которого выдается на группу 21 адресных выходов устройства через третий коммутатор 13. В качестве слов ССП, сменяемых при прерывании, используются, например, содер- жимые счетчика 1 и регистров 3 базового и 4 конечного адресов, которые являются соответствующими словами старого ССП. Содержимые этих слов ССП

мом устройства подключены к управляло- щим входам соответственно первого и третьего коммутаторов, с третьего по пятый входы группы входов управления режимом устройства подключены к управляющему входу второго коммутатора, вход исполнительного адреса устройства соединен с первым информационным входом второго коммутатора, выпоследовательно передаются через ход которого соединен с информацион- рой коммутатор 12, буферный регистр

5 данных и первый коммутатор 11 на группу 2А информационных выходов устройства, а их адреса формируются в счетчик 2 продвижением его содержи- 15 мого на единицу каждый раз при передаче старых слов С€П и приеме новых. Новые слова ССП поступают в счетчик 1 и регистры базового 3 и конечного А адреса аналогично описанному режиму 20 выборки данных из памяти.

Адресация сверхоперативной памяти производится параллельно с работой описанных режимов и происходит следующим образом. В зависимости от кодов 5 управляющих сигналов на группах управляющих входов мультиплексоров 1А и 15, как описано вьппе, происходит выдача на группы 22 и 23 выходов адресов сверхоперативной памяти физичес- 30 ких адресов сверхоперативной памяти, а в случае преобразования адресов, описанных в табл.1, производится выдача сигналов на выходы 27 или 28

ным входом первого буферного регистра данных, выход которого соединен с первым информационным входом первого коммутатора и с информационным входом первого счетчика, выход первого коммутатора соединен с информационными входами регистра базового адреса и регистра конечного адреса и является информационным выходом устройства, информационный вход устройства соединен с вторым информационным входом второго коммутатора, вход фиксированного адреса устройства соединен с третьим информационным входом коммутатора, выход регистра конечного адреса соединен с четвертым информационным входом коммутатора и с первым входом схемы сравнения, выход которой является выходом признака сравнения с конечным адресом устройства, выход регистра базового адреса соединен с пятым информационным входом второго коммутатора и подключен к старшим разрядам выхода адреса устройства и

признака обращения к сверхоперативной 35 старщим разрядам второго входа схе- памяти. При магазинной обработке дан- мы сравнения, информационный выход

ных очередные адреса данных сверхоперативной памяти формируются увеличением или уменьшением на единицу содержимого счетчиков 8 и 9.

Формула изобретения

Устройство сопряжения процессора с памятью, содержащее первый счетчик, 45 первый буферный регистр данных, ре- гист базового адреса, регистр конечного адреса, с первого по третий коммутаторы, схему сравнения, причем с

первого счетчика соединен с первым информационным входом третьего коммутатора и с шестым информационным вхо- 40 дом второго коммутатора, выход третьего коммутатора подключен к младшим разрядам выхода адреса устройства и к младшим разрядам второго входа схемы сравнения, отличающееся тем, что, с целью расширения

области применения за счет повьш ения гибкости адресации сверхоперативной памяти,при хранении данных различного формата, в него дополнительно введены первого по шестой входы группы входов 50 второй счетчик, второй буферный ре- кода операции устройства подключены гистр данных, буферный регистр команд, третий и четвертый счетчики, первый и второй мультиплексоры, с первого по третий элементы НЕ, с пер- 55 вого по шестой элементы И-НЕ, причем с шестого по четырнадцатый входы группы взводов кода операции устройства подключены соответственно к вхосоответственно к входу синхронизации, суммирующему, вычитающему входам первого счетчика к входам синхронизации первого буферного регистра данных, регистра базового адреса и регистра конечного адреса, первый и второй входы группы входов управления реживар- СП

132229612

мом устройства подключены к управляло- щим входам соответственно первого и третьего коммутаторов, с третьего по пятый входы группы входов управления режимом устройства подключены к управляющему входу второго коммутатора, вход исполнительного адреса устройства соединен с первым информационным входом второго коммутатора, выход которого соединен с информацион-

ным входом первого буферного регистра данных, выход которого соединен с первым информационным входом первого коммутатора и с информационным входом первого счетчика, выход первого коммутатора соединен с информационными входами регистра базового адреса и регистра конечного адреса и является информационным выходом устройства, информационный вход устройства соединен с вторым информационным входом второго коммутатора, вход фиксированного адреса устройства соединен с третьим информационным входом коммутатора, выход регистра конечного адреса соединен с четвертым информационным входом коммутатора и с первым входом схемы сравнения, выход которой является выходом признака сравнения с конечным адресом устройства, выход регистра базового адреса соединен с пятым информационным входом второго коммутатора и подключен к старшим разрядам выхода адреса устройства и

первого счетчика соединен с первым информационным входом третьего коммутатора и с шестым информационным вхо- дом второго коммутатора, выход третьего коммутатора подключен к младшим разрядам выхода адреса устройства и к младшим разрядам второго входа схемы сравнения, отличающееся тем, что, с целью расширения

131322296

дам синхронизации второго буферного регистра данных, буферного регистра команд, суммирующим и вычитающим входам с второго по четвертый счетчиков, к входу синхронизации второго счетчи- 5 ка, входы синхронизации третьего и четвертого счетчиков подключены к пятнадцатому входу группы входов кода операции устройства, выход первого коммутатора соединен с информацион- W ным входом буферного регистра команд, выход старших разрядов которого подключен к информационным входам третьего и четвертого счетчиков, выход младших разрядов буферного регистра 5 команд является выходом команды устройства, информационный выход второго счетчика соединен с вторым информационным входом третьего коммутатора, , выход первого буферного регистра дан-20 ных соединен с информационным входом второго счетчика, выход второго коммутатора соединен с информационным входом второго буферного регистра данных, выход которого соединен с вто рым информационным входом первого коммутатора, информационный выход ,третьего счетчика подключен к первому информационному входу первого мультиплексора,

вертого счетчика соединен с первым информационным входом второго мультиплексора, вторым информационным входом первого мультиплексора, первый

14

мультиплексоров н вход первого элемента НЕ подключены к шине нупевого потенциала устройства, выход первого элемента НЕ подключен к первому и второму разрядам четвертых информационных входов первого и второго мультиплексоров, второй и третий разряды информационного выхода четвертого счетчика соединены соответственно с третьим и четвертым разрядами четвертого информационного входа второго мультиплексора, выход которого является выходом первого адреса сверхоперативной памяти устройства, второй и третий разряды информационного выхода третьего счетчика соединены соответственно с третьим и четвертым разрядами четвертого информационного входа первого мультиплексора, выход которого является выходом второго адреса сверхоперативной памяти устройства, выход третьего элемента И-НЕ соединен с первым входом первого элемента И-НЕ, выход которого является выходом первого признака обращения к сверхоперативной памяти устройства, выход пятого элемента И-НЕ соединен с вторым входом первого элемента И- НЕ, выход шестого элемента И-НЕ соеинформационный выход чет- -30 дивен с первым входом второго элемента И-НЕ, выход которого является выходом второго признака обращения к сверхоперативной памяти, выход четвертого элемента И-НЕ соединен с вто.-25

разряд информационного выхода третье-35 рым входом второго элемента И-НЕ,

го счетчика соединен с первым входом третьего элемента И-НЕ и с входом второго элемента НЕ, выход которого соединен с первым входом четвертого элемента И-НЕ, информационный выход третьего счетчика подключен к второму информационному входу второго мультиплексора, первый разряд информационного выхода четвертого счетчика соешестой и седьмой входы группы входо управления режимом устройства подкл чены соответственно к первому и вто рому управляющим входам первого мул 40 типлексора, восьмой и девятый входы группы входов управления режимом ус ройства подключены соответственно к первому и второму управляющим входа второго мультиплексора, с десятого

динен с первым входом пятого элемента 5 по тринадцатый входы группы входов

И-НЕ и с входом третьего элемента НЕ, выход которого соединен с первым входом шестого элемента И-НЕ, третьи информационные входы первого и второго

, - 5 а W , 5 о -20у .-25

шестой и седьмой входы группы входов управления режимом устройства подключены соответственно к первому и второму управляющим входам первого муль- типлексора, восьмой и девятый входы группы входов управления режимом устройства подключены соответственно к первому и второму управляющим входам второго мультиплексора, с десятого

по тринадцатый входы группы входов

управления режимом устройства подключены соответственно к вторьм входам с третьего по шестой элементов И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования адресов команд и данных | 1985 |

|

SU1312573A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Устройство для формирования адреса | 1979 |

|

SU860072A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении устройств формирования адресов памяти в двухадресных ЦВМ: Цель изобретения - расширение области применения за счет повышения гибкости адресации сверхоперативной памяти при хранении данных различных форматов. Устройство содержит первый и второй счетчики 1 и 2, регистры 3 базового и 4 конечного адресов, первый 5 и второй 6 буферные регистры данных, буферный регистр 7 команд, третий и четвертый счетчики, схему 10 сравнения, первый 11, второй 12 и третий 13 коммутаторы, первый и второй мультиплексоры, первый и второй блоки признака обращения к сверхоперативной памяти, первый и второй элементы И-НЕ и первый элемент НЕ. Новыми элементами в устройстве являются второй счетчик 2, второй буферный регистр 6 данных, буферный ре- с гистр 7 команд, третий и четвертый счетчики, первый и второй мультиплексоры, первый и второй блоки признака обращения к сверхоперативной памяти и первый элемент НЕ. 3 ил., 3 табл. (Л t;i

Редактор А.Ворович

ФигЗ 8(9)

Составитель А.Сошкин

Техред И.Попович Корректор А. Тяско

Заказ 2866/46Тираж 672 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Пр(1ичволственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

| Формирователь адреса | 1972 |

|

SU489106A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса | 1979 |

|

SU860072A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1067939, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-07-07—Публикация

1986-02-05—Подача