Изобретение относится к вычислительной технике и дискретной авто1матике, в частности к устройствам контроля программируемых постоянных запоминающих устройств, и может быть использовано для контроля качества программирования микросхем в программаторах.

Цель изобретения - повышение точности контроля.

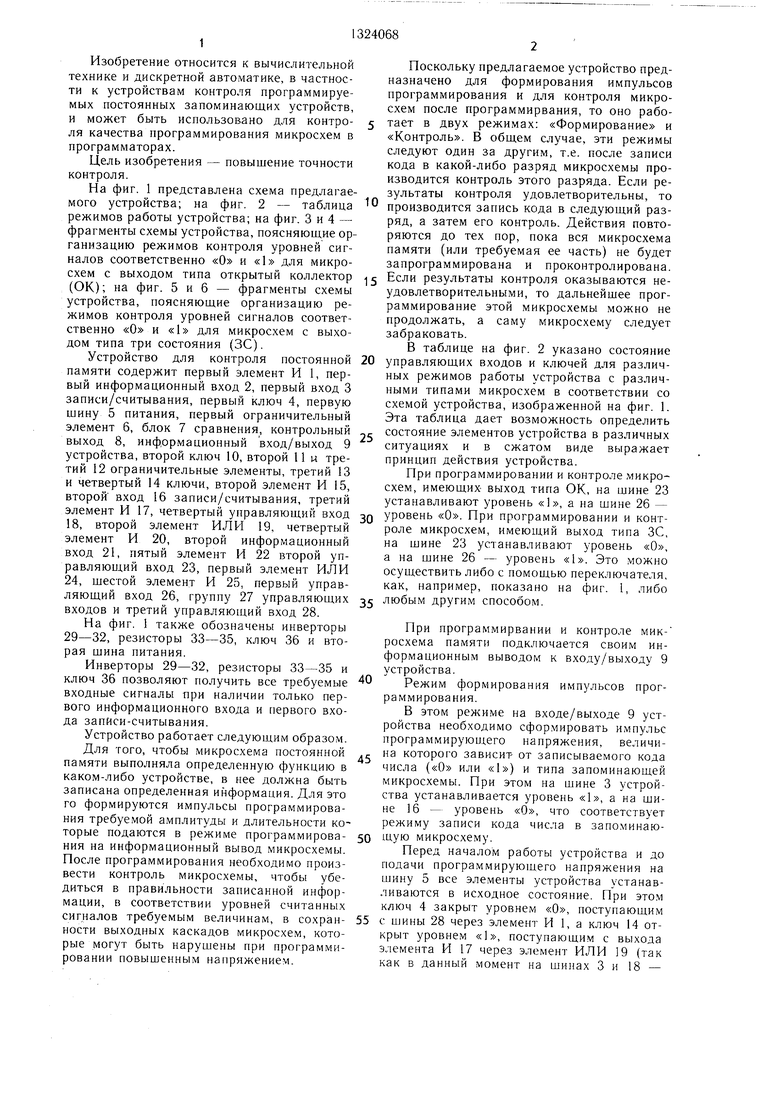

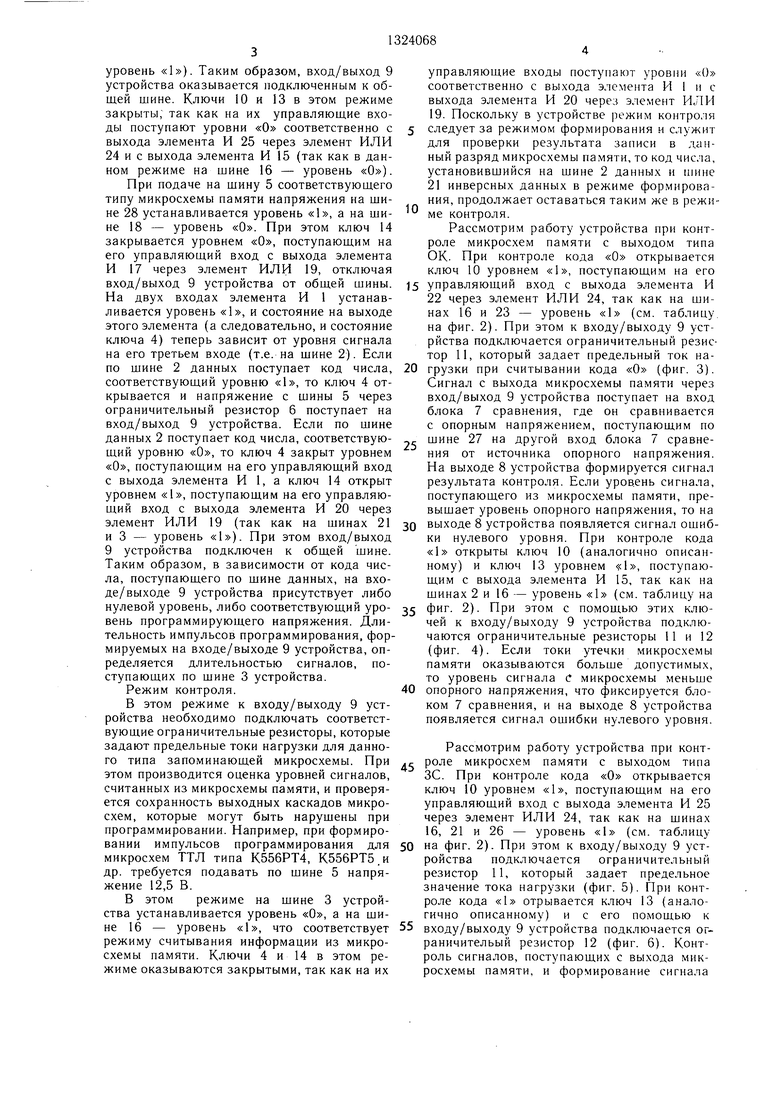

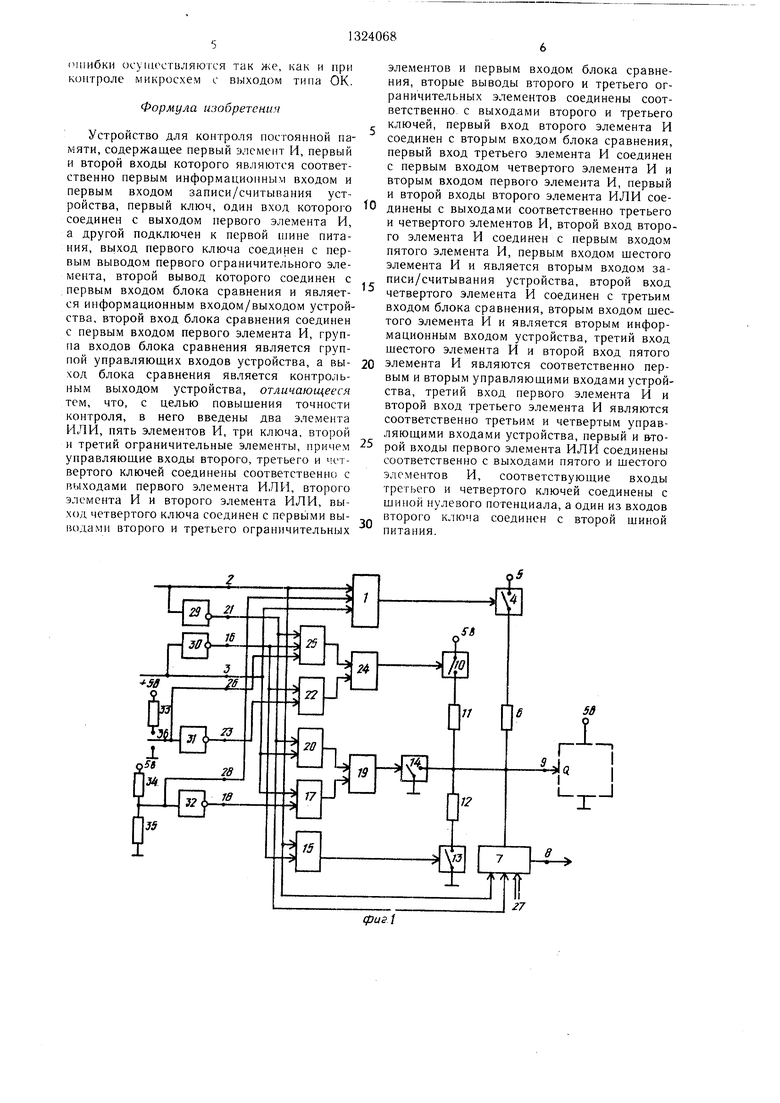

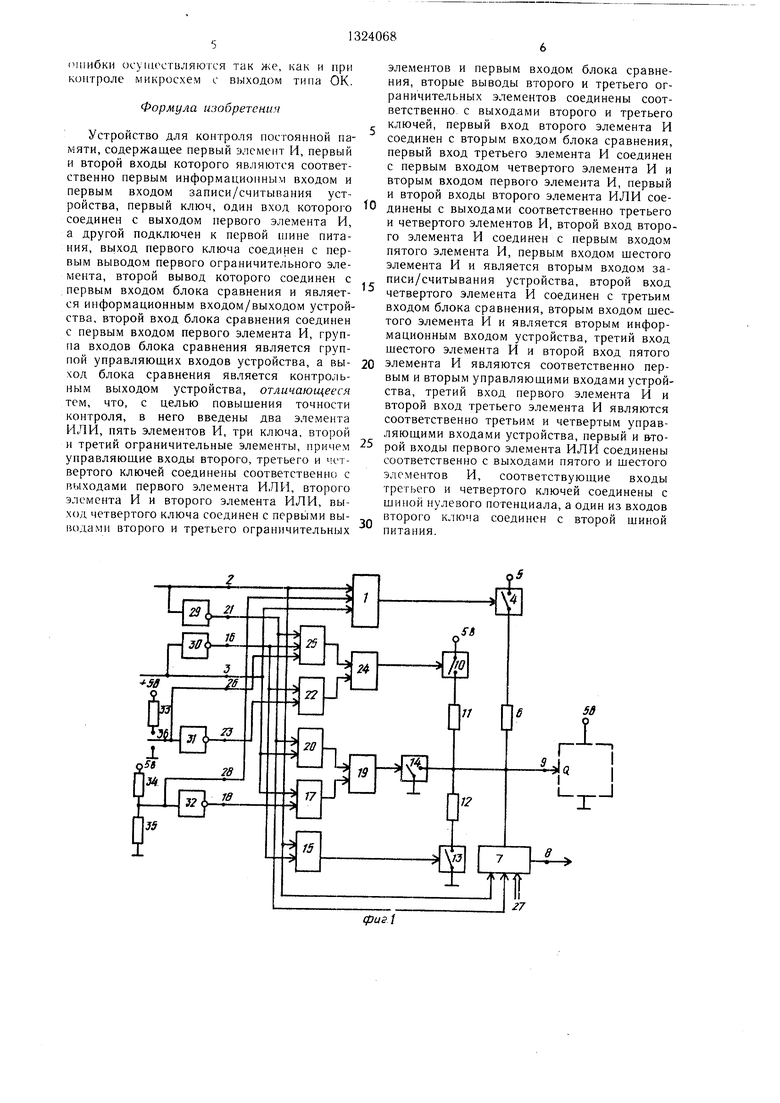

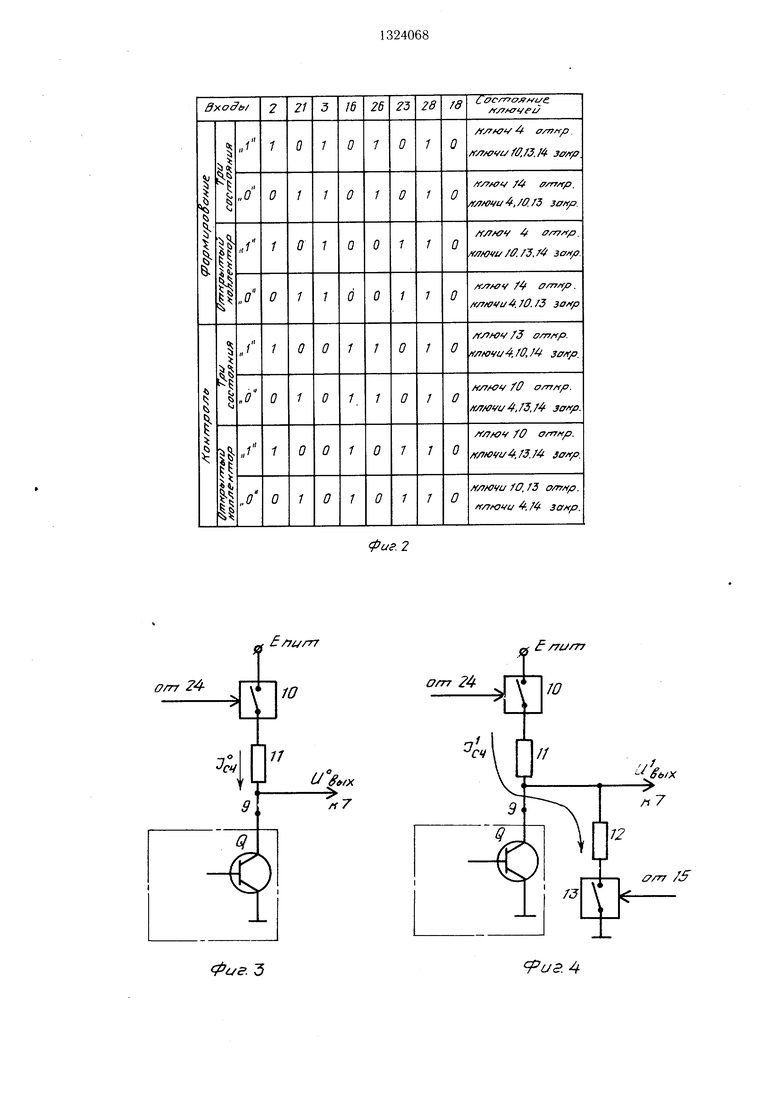

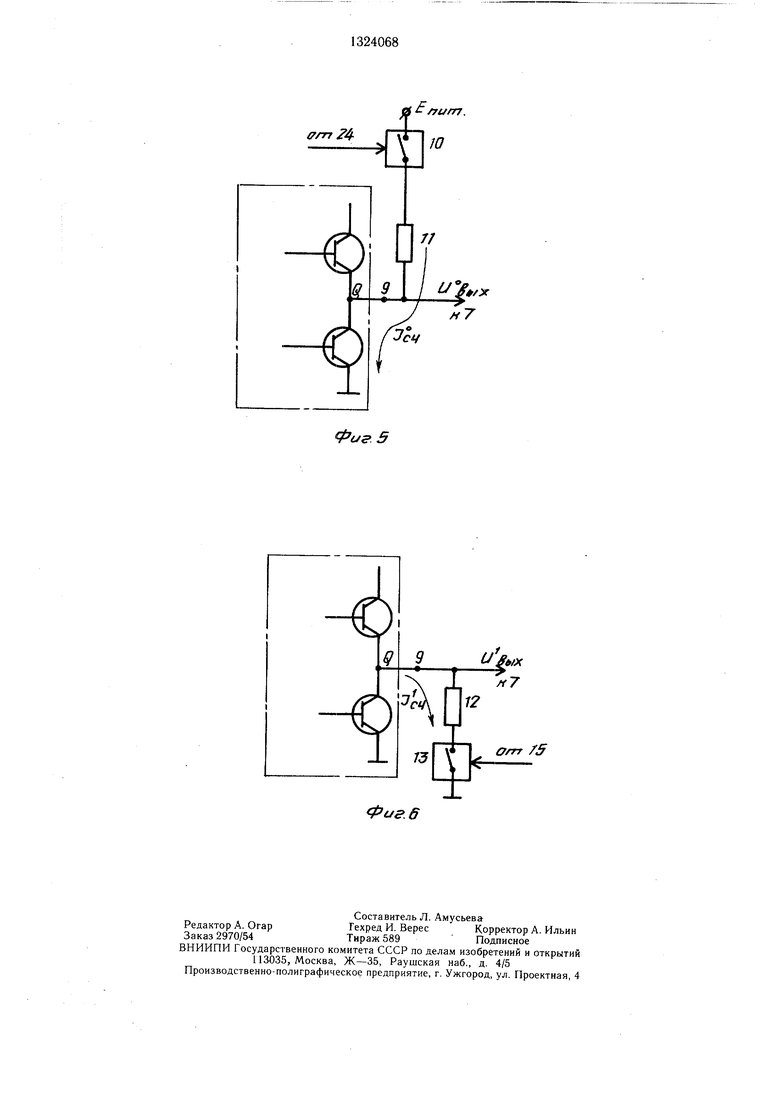

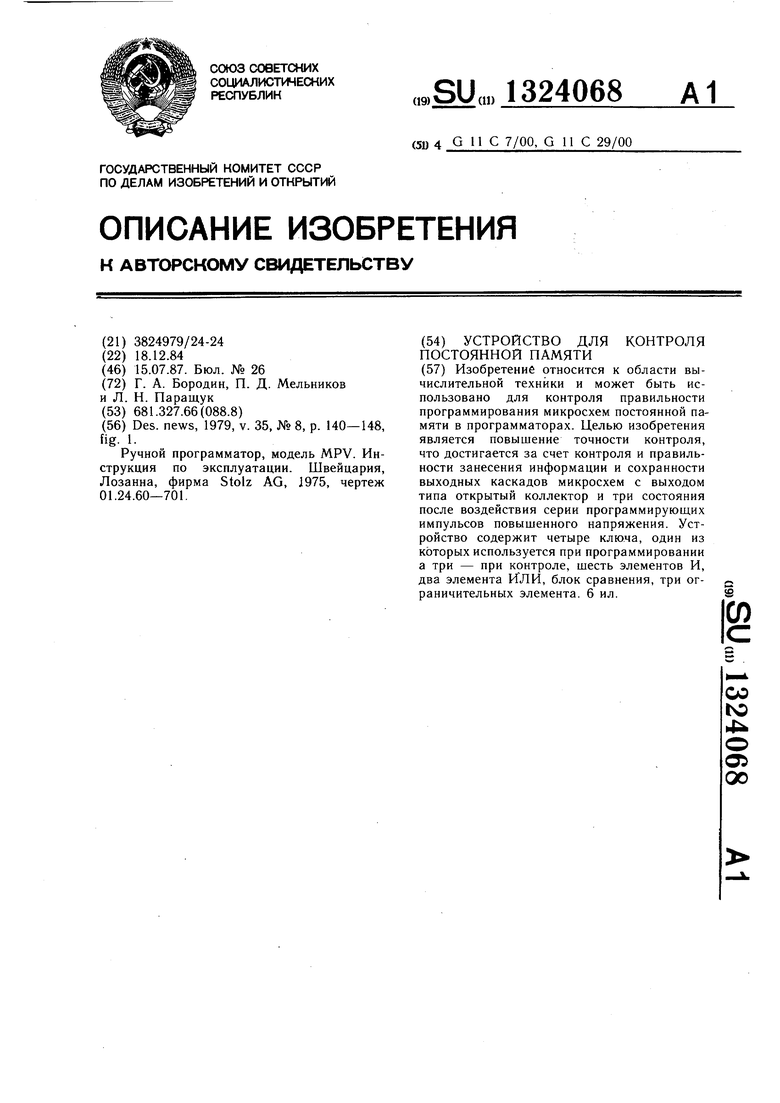

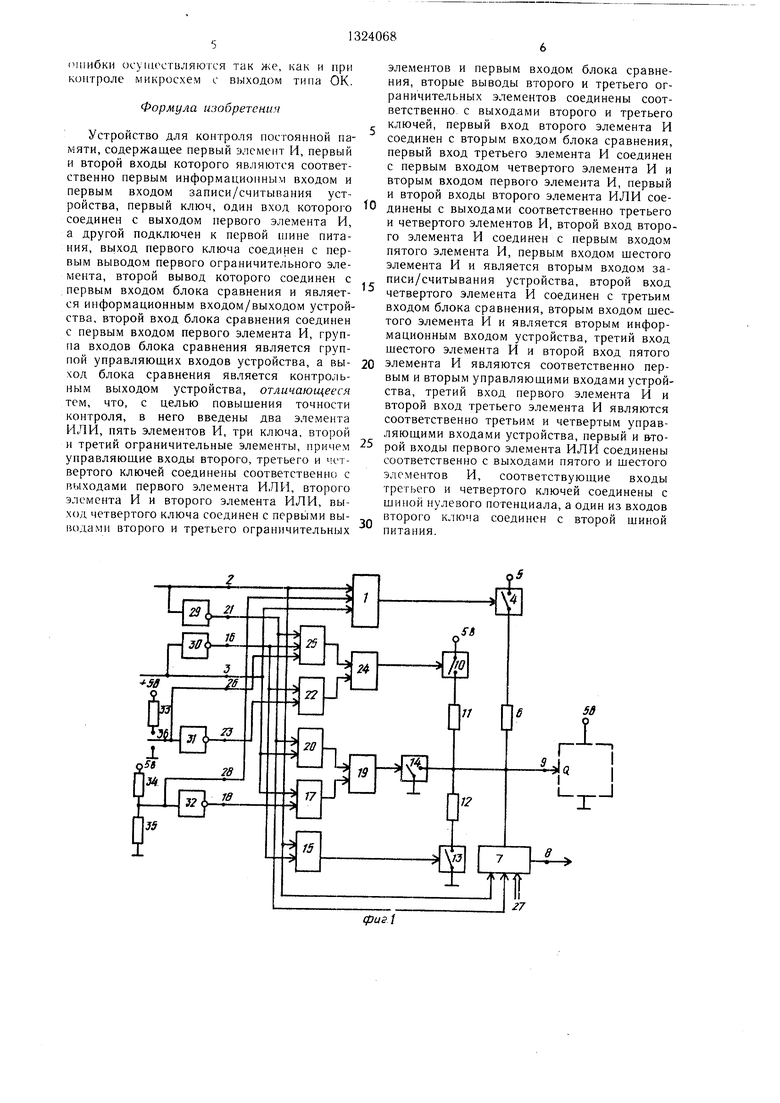

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 - таблица режимов работы устройства; на фиг. 3 и 4 - фрагменты схемы устройства, поясняющие организацию режимов контроля уровней сигналов соответственно «О и «1 для микросхем с выходом типа открытый коллектор (ОК); на фиг. 5 и 6 - фрагменты схемы устройства, поясняющие организацию режимов контроля уровней сигналов соответственно «О и «1 для микросхем с выходом типа три состояния (ЗС).

Устройство для контроля постоянной памяти содержит первый элемент И 1, первый информационный вход 2, первый вход 3 записи/считывания, первый ключ 4, первую шину 5 питания, первый ограничительный элемент б, блок 7 сравнения, контрольный выход 8, информационный вход/выход 9 устройства, второй ключ 10, второй 11 ц третий 12 ограничительные элементы, третий 13 и четвертый 14 ключи, второй элемент И 15, второй вход 16 записи/считывания, третий элемент И 17, четвертый управляющий вход 18, второй элемент ИЛИ 19, четвертый элемент И 20, второй информационный вход 21, пятый элемент И 22 второй управляющий вход 23, первый элемент ИЛИ 24, щестой элемент И 25, первый управляющий вход 26, группу 27 управляющих входов и третий управляющий вход 28.

На фиг. 1 также обозначены инверторы 29-32, резисторы 33-35, ключ 36 и вторая щина питания.

Инверторы 29-32, резисторы 33-35 и ключ 36 позволяют получить все требуемые входные сигналы при наличии только первого информационного входа и первого входа записи-считывания.

Устройство работает следующим образом.

Для того, чтобы микросхема постоянной памяти выполняла определенную функцию в каком-либо устройстве, в нее должна быть записана определенная информация. Для это го формируются импульсы программирования требуемой амплитуды и длительности которые подаются в режиме программирования на информационный вывод микросхемы. После программирования необходимо произвести контроль микросхемы, чтобы убедиться в правильности записанной информации, в соответствии уровней считанных сигналов требуемым величинам, в сохранности выходных каскадов микросхем, которые могут быть нарущены при программировании повыщенным напряжением.

0

Поскольку предлагаемое устройство предназначено для формирования импульсов программирования и для контроля микросхем после программирвания, то оно работает в двух режимах: «Формирование и «Контроль. В общем случае, эти режимы следуют один за другим, т.е. после записи кода в какой-либо разряд микросхемы производится контроль этого разряда. Если результаты контроля удовлетворительны, то производится запись кода в следующий разряд, а затем его контроль. Действия повторяются до тех пор, пока вся микросхема памяти (или требуемая ее часть) не будет запрограммирована и проконтролирована.

5 Если результаты контроля оказываются неудовлетворительными, то дальнейшее программирование этой микросхемы можно не продолжать, а саму микросхему следует забраковать.

В таблице на фиг. 2 указано состояние

0 управляющих входов и ключей для различных режимов работы устройства с различными типами микросхем в соответствии со схемой устройства, изображенной на фиг. 1. Эта таблица дает возможность определить

с состояние элементов устройства в различных ситуациях и в сжатом виде выражает принцип действия устройства.

При программировании и контроле микросхем, имеющих- выход типа ОК, на щине 23 устанавливают уровень «1, а на щине 26 -

0 уровень «О. При программировании и контроле микросхем, имеющий выход типа ЗС, на щине 23 устанавливают уровень «О, а на щине 26 - уровень «1. Это можно осуществить либо с помощью переключателя, как, например, показано на фиг. 1, либо

5 любым другим способом.

При программирвании и контроле мик- росхема памяти подключается своим информационным выводом к входу/выходу 9 устройства.

0 Режим формирования импульсов программирования.

В этом режиме на входе/выходе 9 устройства необходимо сформировать импульс программируюц-1,его напряжения, величи- г на которого зависит от записываемого кода числа («О или «1) и типа запоминающей микросхемы. При этом на щине 3 устройства устанавливается уровень «1, а на щине 16 - уровень «О, что соответствует режиму записи кода числа в запоминаю- 0 тую микросхему.

Перед началом работы устройства и до подачи программирующего нанряжения на шину 5 все элементы устройства устанавливаются в исходное состояние. При этом ключ 4 закрыт уровнем «О, поступающим 5 с шины 28 через элемент И 1, а ключ 14 открыт уровнем «1, поступающим с выхода элемента И 17 через элемент ИЛИ 19 (так как в данный момент на шипах 3 и 18 -

уровень «1). Таким образом, вход/выход 9 устройства оказывается подключенным к общей шине. Ключи 10 и 13 в этом режиме закрыты; так как на их управляющие входы поступают уровни «О соответственно с выхода элемента И 25 через элемент ИЛИ 24 и с выхода элемента И 15 (так как в данном режиме на щине 16 - уровень «О). При подаче на шину 5 соответствующего типу микросхемы памяти напряжения на шине 28 устанавливается уровень «1, а на шине 18 - уровень «О. При этом ключ 14 закрывается уровнем «О, поступающим на его управляющий вход с выхода элемента И 17 через элемент ИЛИ 19, отключая

10

управляющие входы поступают уровни «О соответственно с выхода элемента И 1 и с выхода элемента И 20 через элемент ИЛИ 19. Поскольку в устройстве режим контроля следует за режимом формирования и служит для проверки результата записи в данный разряд микросхемы памяти, то код числа, установившийся на шине 2 данных и шине 21 инверсных данных в режиме формирования, продолжает оставаться таким же в режиме контроля.

Рассмотрим работу устройства при контроле микросхем памяти с выходом типа ОК. При контроле кода «О открывается ключ 10 уровнем «1, поступающим на его

вход/выход 9 устройства от общей шины. 5 управляющий вход с выхода элемента И

На двух входах элемента И 1 устанавливается уровень «1, и состояние на выходе этого элемента (а следовательно, и состояние ключа 4) теперь зависит от уровня сигнала на его третьем входе (т.е. на щине 2). Если

22 через элемент ИЛИ 24, так как на шинах 16 и 23 - уровень «1 (см. таблицу на фиг. 2). При этом к входу/выходу 9 уст- рйства подключается ограничительный резистор 11, который задает предельный ток напо шине 2 данных поступает код числа, 20 грузки при считывании кода «О (фиг. 3). соответствующий уровню «1, то ключ 4 от-Сигнал с выхода микросхемы памяти через

шины

крывается и напряжение с шины 5 через ограничительный резистор 6 поступает на вход/выход 9 устройства. Если по шине данных 2 поступает код числа, соответствующий уровню «О, то ключ 4 закрыт уровнем «О, поступающим на его управляющий вход с выхода элемента И 1, а ключ 14 открыт уровнем «1, поступающим на его управляющий вход с выхода элемента И 20 через элемент ИЛИ 19 (так как на шинах 21 и 3 - уровень «1). При этом вход/выход 9 устройства подключен к общей шине. Таким образом, в зависимости от кода числа, поступающего по щине данных, на входе/выходе 9 устройства присутствует либо

25

вход/выход 9 устройства поступает на вход блока 7 сравнения, где он сравнивается с опорным напряжением, поступающим по щине 27 на другой вход блока 7 сравнения от источника опорного напряжения. На выходе 8 устройства формируется сигнал результата контроля. Если уровень сигнала, поступающего из микросхемы памяти, превышает уровень опорного напряжения, то на 30 выходе 8 устройства появляется сигнал ошибки нулевого уровня. При контроле кода «1 открыты ключ 10 (аналогично описанному) и ключ 13 уровнем «1, поступающим с выхода элемента И 15, так как на шинах 2 и 16 - уровень «1 (см. таблицу на

чаются ограничительные резисторы 11 и 12 (фиг. 4). Если токи утечки микросхемы памяти оказываются больше допустимых, то уровень сигнала С микросхемы меньше 40 опорного напряжения, что фиксируется блоком 7 сравнения, и на выходе 8 устройства появляется сигнал ошибки нулевого уровня.

нулевой уровень, либо соответствующий уро- 35 фиг. 2). При этом с помощью этих клю- вень программирующего напряжения. Дли-чей к входу/выходу 9 устройства подклютельность импульсов программирования, формируемых на входе/выходе 9 устройства, определяется длительностью сигналов, поступающих по шине 3 устройства.

Режим контроля.

В этом режиме к входу/выходу 9 устройства необходимо подключать соответствующие ограничительные резисторы, которые

задают предельные токи нагрузки для данно-Рассмотрим работу устройства при копт- го типа запоминающей микросхемы. При . роле микросхем памяти с выходом типа -. 2Q Yipn контроле кода «О открывается

ключ 10 уровнем «1, поступающим на его управляющий вход с выхода элемента И 25 через элемент ИЛИ 24, так как на щинах 16, 21 и 26 - уровень «1 (см. таблицу 50 на фиг. 2). При этом к входу/выходу 9 устройства подключается ограничительный резистор 11, который задает предельное значение тока нагрузки (фиг. 5). При контроле кода «1 отрывается ключ 13 (аналогично описанному) и с его помощью к

не 16 - уровень «1, что соответствует 55 входу/выходу 9 устройства подключается ог- режиму считывания информации из микро-раничительый резистор 12 (фиг. 6). Контсхемы памяти. Ключи 4 и 14 в этом ре-роль сигналов, поступающих с выхода микжиме оказываются закрытыми, так как на ихросхемы памяти, и формирование сигнала

этом производится оценка уровней сигналов, считанных из микросхемы памяти, и проверяется сохранность выходных каскадов микросхем, которые могут быть нарущены при программировании. Например, при формировании импульсов программирования для микросхем ТТЛ типа К556РТ4, К556РТ5.И др. требуется подавать по шине 5 напряжение 12,5 В.

В этом режиме на щине 3 устройства устанавливается уровень «О, а на ши0

управляющие входы поступают уровни «О соответственно с выхода элемента И 1 и с выхода элемента И 20 через элемент ИЛИ 19. Поскольку в устройстве режим контроля следует за режимом формирования и служит для проверки результата записи в данный разряд микросхемы памяти, то код числа, установившийся на шине 2 данных и шине 21 инверсных данных в режиме формирования, продолжает оставаться таким же в режиме контроля.

Рассмотрим работу устройства при контроле микросхем памяти с выходом типа ОК. При контроле кода «О открывается ключ 10 уровнем «1, поступающим на его

5 управляющий вход с выхода элемента И

управляющий вход с выхода элемента И

22 через элемент ИЛИ 24, так как на шинах 16 и 23 - уровень «1 (см. таблицу на фиг. 2). При этом к входу/выходу 9 уст- рйства подключается ограничительный резистор 11, который задает предельный ток на грузки при считывании кода «О (фиг. 3). Сигнал с выхода микросхемы памяти через

5

вход/выход 9 устройства поступает на вход блока 7 сравнения, где он сравнивается с опорным напряжением, поступающим по щине 27 на другой вход блока 7 сравнения от источника опорного напряжения. На выходе 8 устройства формируется сигнал результата контроля. Если уровень сигнала, поступающего из микросхемы памяти, превышает уровень опорного напряжения, то на 0 выходе 8 устройства появляется сигнал ошибки нулевого уровня. При контроле кода «1 открыты ключ 10 (аналогично описанному) и ключ 13 уровнем «1, поступающим с выхода элемента И 15, так как на шинах 2 и 16 - уровень «1 (см. таблицу на

чаются ограничительные резисторы 11 и 12 (фиг. 4). Если токи утечки микросхемы памяти оказываются больше допустимых, то уровень сигнала С микросхемы меньше опорного напряжения, что фиксируется блоком 7 сравнения, и на выходе 8 устройства появляется сигнал ошибки нулевого уровня.

фиг. 2). При этом с помощью этих клю- чей к входу/выходу 9 устройства подклюошибки осушестиляются так же, как и при контроле микросхем с выходом типа ОК.

Формула изобретения

Устройство для контроля постоянной памяти, содержащее первый элемент И, первый и второй входы которого являются соответственно первым информациопным входом и первым входом записи/считывания устройства, первый ключ, один вход которого соединен с выходом первого элемента И, а другой подключен к первой шине питания, выход первого ключа соединен с первым выводом первого ограничительного элемента, второй вывод которого соединен с первым входом блока сравнения и является информационным входом/выходом устройства, второй вход блока сравнения соединен с первым входом первого элемента И, группа входов блока сравнения является группой управляющих входов устройства, а вы- ход блока сравнения является контрольным выходом устройства, отличающееся тем, что, с целью повышения точности контроля, в него введены два элемента ИЛИ, пять элементов И, три ключа, второй и третий ограничительные элементы, причем управляющие входы второго, третьего и четвертого ключей соединены соответственно с выходами первого элемента ИЛИ, второго элемента И и второго элемента ИЛИ, выход четвертого ключа соединен с первыми вы- водами второго и третьего ограничительных

элементов и первым входом блока сравнения, вторые выводы второго и третьего ограничительных элементов соединены соответственно с выходами второго и третьего ключей, первый вход второго элемента И соединен с вторым входом блока сравнения, первый вход третьего элемента И соединен с первым входом четвертого элемента И и вторым входом первого элемента И, первый и второй входы второго элемента ИЛИ соединены с выходами соответственно третьего и четвертого элементов И, второй вход второго элемента И соединен с первым входом пятого элемента И, первым входом шестого элемента И и ЯЕ1ляется вторым входом записи/считывания устройства, второй вход четвертого элемента И соединен с третьим входом блока сравнения, вторым входом щес- того элемента И и является вторым информационным входом устройства, третий вход шестого элемента И и второй вход пятого элемента И являются соответственно первым и вторым управляющими входами устройства, третий вход первого элемента И и второй вход третьего элемента И являются соответственно третьим и четвертым управляющими входами устройства, первый и В ТО- рой входы первого элемента ИЛИ соединены соответственно с выходами пятого и шестого элементов И, соответствующие входы третьего и четвертого ключей соединены с щиной нулевого потенциала, а один из входов второго ключа соединен с второй шиной питания.

k/x

А7

/f/7///77

от 24

/77 /f

Ф(г. Ъ

иа 4

ff/rj г4

fjufrr.

/Jr

фиг в

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микросхем памяти (его варианты) | 1984 |

|

SU1166180A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ | 1991 |

|

RU2010363C1 |

| Программатор | 1986 |

|

SU1439677A1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Программатор | 1987 |

|

SU1654869A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

| Устройство для программирования микросхем памяти | 1986 |

|

SU1381592A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1990 |

|

RU2047918C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| Устройство для программирования микросхем памяти | 1981 |

|

SU1005183A1 |

изобретение относится к области вычислительной техники и может быть использовано для контроля правильности программирования микросхем постоянной памяти в программаторах. Целью изобретения является повышение точности контроля, что достигается за счет контроля и правильности занесения информации и сохранности выходных каскадов микросхем с выходом типа открытый коллектор и три состояния после воздействия серии программирующих импульсов повышенного напряжения. Устройство содержит четыре клю.ча, один из которых используется при программировании а три - при контроле, шесть элементов И, два элемента ИЛИ, блок сравнения, три ограничительных элемента. 6 ил. I сл со N5 О 05 00

i

MX

О/ТГ /5

фиг. 6

| Des | |||

| news, 1979, v | |||

| Скоропечатный станок для печатания со стеклянных пластинок | 1922 |

|

SU35A1 |

| Способ закалки пил | 1915 |

|

SU140A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Ручной программатор, модель MPV | |||

| Инструкция по эксплуатации | |||

| Швейцария, Лозанна, фирма Stolz AG, 1975, чертеж 01.24.60-701. | |||

Авторы

Даты

1987-07-15—Публикация

1984-12-18—Подача