выход счетчика соединен с входом дешифратора-шифратора, первый выход которого соединен с входом установки сметчика и входом останова генератора импульсов, второй и третий выходы дешифратора-шифратора соединены соответственно с первым входом триггера и вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом триггера, выходы первого элемента И, второго элемента ИЛИ, перво го элемента ИЛИ, прямой выход триггера и вход запуска блока соединены соответственно с первого по пятый бйходами блока управления.

.3. Устройство по П.1, о т л и мающееся тем, что блок анализа содержит схему сравнения, четыре элемента И и триггер, причем первый и второй входы блока соединены с первым и вторым входами схемы сравнения, прямой и инверсный выходы которой соединены С- первыми входами первого и второго элементов И, вторые входы которых соединены с третьим входом блока, четвертый вход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И, выходы третьего и четвертого элементов И соединены соответственно с первым и вторым выходами блока анализа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления квадратного корня | 1985 |

|

SU1254477A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Устройство для вычисления степенных функций | 1985 |

|

SU1282120A1 |

| Устройство для вычисления квадратного корня | 1979 |

|

SU924703A1 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU940155A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

Изобретение относится,к вычислительной технике и может быть использовано для аппаратной реализации операции вычисления квадратного корня и его обратной величины в вычисли- тельных и управляющих системах, в устройствах автоматики, телемеханики, контроля и т.д.

Известно устройство для извлечения квадратного корня, содержащее два сумматора, .три регистра, схему сравнения и блок управления LO

Недостатком этого устройств а является невозможность получения обратной величины квадратного корня, низкие функциональные возможности.

Наиболее близким по технической сущности к изобретению является устройство для вычисления элементарных функций,содержащее четыре сумматоравычитателя, четыре регистра, блок памяти , блок анализа знака и блок управ ления, причем выходытрех сумматороввычитателей соединены через соответствукэдие регистры со своими входами, вторые выходы первого и бторого регистров соединены с первым и вторым входами блока анализа, второй выхОд третьего регистра соединен с входди четвертого регистра, первый выход блока управления соединен с управляющими зходами первого-третьего регистров, второй зыход - с управляющим

входом четвертого регистра. Это устройство предназначено для вычисления либо квадратного корня, либо квадрата .аргумента 2.

Однако известное устройство не предназначено АЛЯ одновременного вычисления квадратного корня и его обратной величины, т.е.. ограниченные функциональные возможности.

Цель изобретения - расширение класса решаемых задач за счет возможности дополнительного вычисления обратной величины квадратного корня из числа.

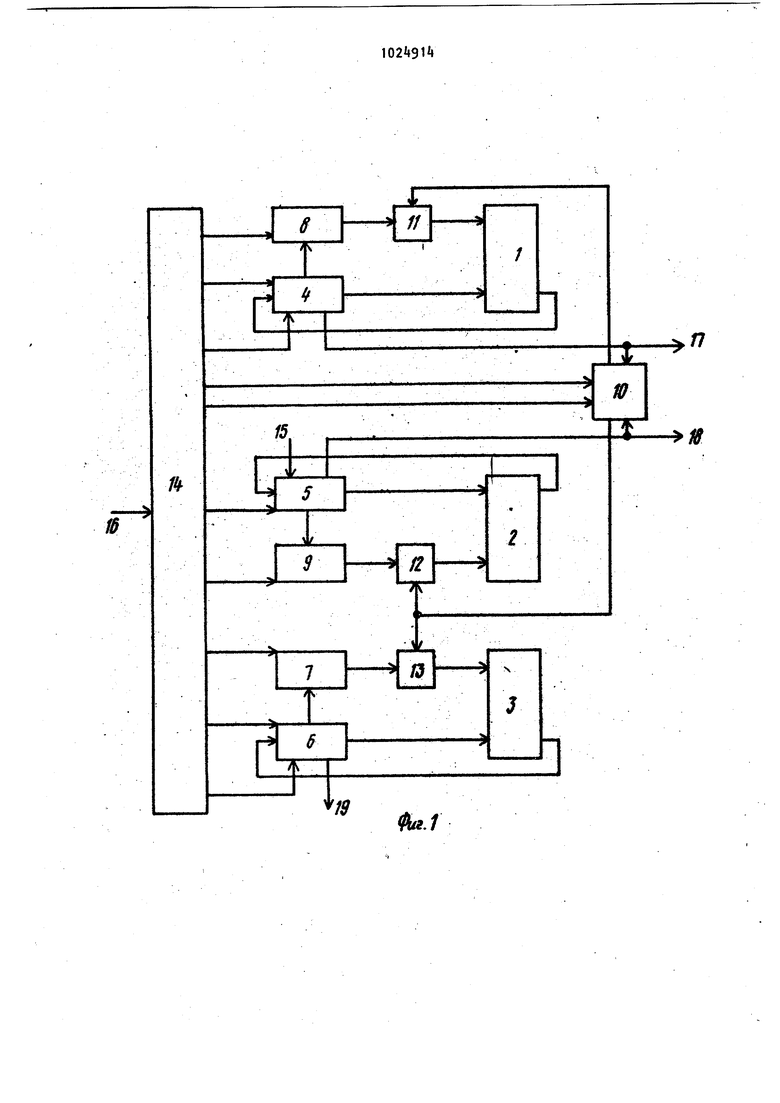

Поставленная цель достигается тем, что в устройство для вычисления элементарных функций, содержащее три сумматора, четыре регистра, блок анализа и блок управления, первый выход которого соедин1ен с тактовыми входами первого, второго и третьего регистров выходы младших разрядов которых соединены с первыми входами соответствующих сумматоров, выходы которых соединены с информационными входами соответствующих регистров, выходы разрядов первого и второго регистров соединены соответственно с первым и вторым входами блока анализа, второй выход блока управления соединен с управляющим Входом четвертого регистра, информационный вход которого соединен с выходом разрядов третьего регистра, введены пятый и шестой регистры и три элемента И, причем третий и четвертый выходы блока управления соединены соответственно с третьим и четвертым входами блока анализа, первый выход которого соединен с первым входом первого элемента И, второй вход и выход которого соединены соответствен но с выходом пятого регистра и вторым входом первого сумматора, управляющий вход и информационный вход пятого регистра соединены соответственно с вторым выходом блока управления и выходом разрядов первого регистра, вход установки которого соединен с пятым выходом блока управления и входом ус-« тановки треуьёго регистра, второй выход блока управления соединен с управляющим входом шестого регистра, информационный вход и выход которого соеДи нены соответственно с выходами разрядом второго регистра и первым входом второго эт емента И, второй вход которого соединен с четвертым выходом блока анализа и первым входом третьего элемента И, второй вход которого соединен с выходом четвертого регистра, выходы второго и третьего элементов И соединены с вторыми входами соответствующих сумматоров. , Кроме того, блок управления содержит.генератор импульсов, элемент задержки ,.счетчик, дешифратор-шифратор триггер, два элемента И и два элемента ИЛИ, причем вход запуска блока соединен с. первым входом первого 3neмента ИЛИ и через элемент задержки с входом запуска генератора импульсов, выход которого соединен со счетным входом счетчика и первыми входами пер вого и второго элементов/И, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, выходы первого и второго элементов И соединены с входами второго элемента ИЛИ, выход счетчика соединен с входом дешифратора-шифратора, первый выход которого соединен с входом установки, счетчика и входом останова генератора импульсов, второй и третий выходы дешифратора-шифратора соединены соответственно с первым входом триггера и вторым входом первого элемента ИЛИ, выход которого соединен с вторым входом триггера, выходы первого элемента И, второго элемента ИЛИ, первого элемента ИЛИ, прямой выход триггера и вход запуска блока соединены соответственно с первого по пятый выходами блока управления. При этом блок анализа содержит схему сравнения, четыре элемента И и триггер, причем первый и второй входы блока срединены с первым и вторым входами схемы сравнения, прямой и инверсный выходы которой соединены с первыми входами первого и второго элементов И, вторые входы которых соединены с третьим входом блока, четвертый вход которого соединен с первыми входами третьего и четвертого элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами триггера, первый и второй входы которого соединены с выходами соответственно первого и второго элементов И, выходы третьего и четвертого элементов И соединены соответствен но с первым и вторым выходами блока анализа. На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - структурная схема блока анализа; на фиг.З - структурная схема блока управления. Устройство для вычисления элементарных функции содержит сумматоры 1-3, регистры k-B, блок 10 анализа, элементы И 11-13, блок И управления, ВХ.ОДЫ 15 и 16 и выходы 17 19 устройС1;ва. Блок 10 анализа (фиг.2) содержит схему 20 сравнения, триггер 21, элементы И 22-25, входы 26-29 и выходы 30 и 31. Блок 1 управления (фиг.З) содержит генератор 32 импульсов, работающий в старт-стопном режиме, счетчик 33, дешифратор-шифратор 3, триггер 35 элементы И 3$ и 37 элементы ИЛИ 38 и 39, элемент 0 задержки, вход 1 запуска и .выходы . Вычисление квадратного корня и его обратной величины производится по алгоритму, содержащему разностные рекуррентные соотношения V-fei2..2..q. Г jf Хс-х, x,-x-4j l , V, , 3 , где ,...,п - порядковый номер итерации;п - число разрядов аргумента х; 5102 ы , .-% К П ()- коэффициент коррекции j-л 1-О результата. Соотношение Z: реализуется в сумма торе 1 и регистрах 4 и 8, соотноше ние х; - в сумматоре 2 и регистрах 5 и 9, соотношение у:- в сумматоре 3 и регистрах 7 и 9. Знамение цифры д; определяется в блоке 10 анализа, каждое из соотношений вычисляется последовательно в каждой итерации, причем все соотношения вычисляются одновременно. Вычисление указанных функций осуществляется следующим образом. Первоначально в регистр 5 заносится по входу 15 аргумент X и подается стартовый импульс на вход 16. Последний устанавливает в регистр значение коэффициента l/K CpaBHoe 0,), в регистр 6 - значение единицы. Значения в регистрах -6 соответственно повторяются в регистрах 7-9. По стартовому импульсу, а затем по импульсам конца итерации в блоке 10 анализа определяется значение цифры Qi, которое запоминается триггером 21 Затем включается генератор 32 импульсов в блоке И управления, на втором выходе которого появляются в каждой итерации импульсы сдвига {один импульс сдвига для первой итерации, два импульса для второй и т.д.). Содержания регистров 7-9 сдвигаются. Затем импульс начала итерации, соответствующий последнему импульсу сдвиг переводит триггер 35 в блоке 1 управления в нулевое состояние и с первого выхода блока 14 управления подаются импульсы продвижения, которые продвигают содержания регистров А-6 и на соответствующие входы сумматоров 1-3 В этот момент времени на блок 10 анализа с четвертого выхода блока 1 управления поступает импульс бланка, при помощи которого значения цифр д- и 9 передаются для управления элементами И 11-13. Содержания регистров 73 подаются на вторые входы сумматоров 1-3 при открытых элементах И 11-13, причем одновременно могут быть открыты либо элемент И 11, либо эле мент И 12-13. Результаты суммирования G ВЫХОДОВ сумматоров 1-3 передаются младшими разрядами вперед и освобождающиеся при продвижении информации старшие разряды регистров - и продвигаются к их началу (в сторону младших разрядов). Последний импульс сдвига соответствует импульсу конца итерации. Очередная j-я итерация закончена, триггер 35 в блоке Т управления переводится в-единичное состояние и с второго выхода блока. И выдается последовательность импульсов сдвига для следующей (j+l)- итерации, После выполнения п итераций в регистрах -Ъ находится значение квадратного корня, в регистре 6 - значение ero обратной величины. Время вычисления двух указанных функ1 ий для последовательного принципа работы (последовательные одноразрядные сумматоры и регистры сдвига) равно в тактах Т n(n + nn-il2illv где и - число дополнительных защитных разрядов для компенсации погрешности усечения чисел при их сдвиге за пределы п-разрядной сетки. Время вычисления двух указанных функций для параллельного принципа работы (параллельные сумматоры и матричные сдвйгатели-) равно в тактах Т 2п. Погрешность вычисления в общем случае при использовании дополнительных m разрядов в регистрах устройства всегда меньше единицы последнего п-го двоичного разряда. По сравнению с известным предлагаемое устройство обеспечивает расширенные функциональные возможности, так как обеспечивает одновременное вычисление квадратного корня и его обратной величины, Благодаря большому быстродействию применение предлагаемого устройства позволяет повысить производительность вычисления, особенно при большой частоте обращения к данным операциям.

ь

п

ь

J/

11

1:

/

N

Йй./

25

flOMMK

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1983-06-23—Публикация

1981-04-20—Подача