триггер 7 и начинается передача содержимого реверсивных накопителей группы 5 через соответствующие элементы И группы 6 и первый элемент ИЛИ 3 на счетчик 4. Передача осуществляется с помощью тактовых импульсов, при этом коды в накопителях группы 5 уменьшаются. После того, как содержимое всех накопителей группы 5 будет передано на счетчик 4, на выходе первого элемента И 8 появится единичный сигнал, который через второй элемент

Изобретение относится к автоматике и вычислительной технике и может использоваться для пос троения устройств передачи и переработки дискретной информации.

Цель изобретения - повышение бы- .стродействия устройства.

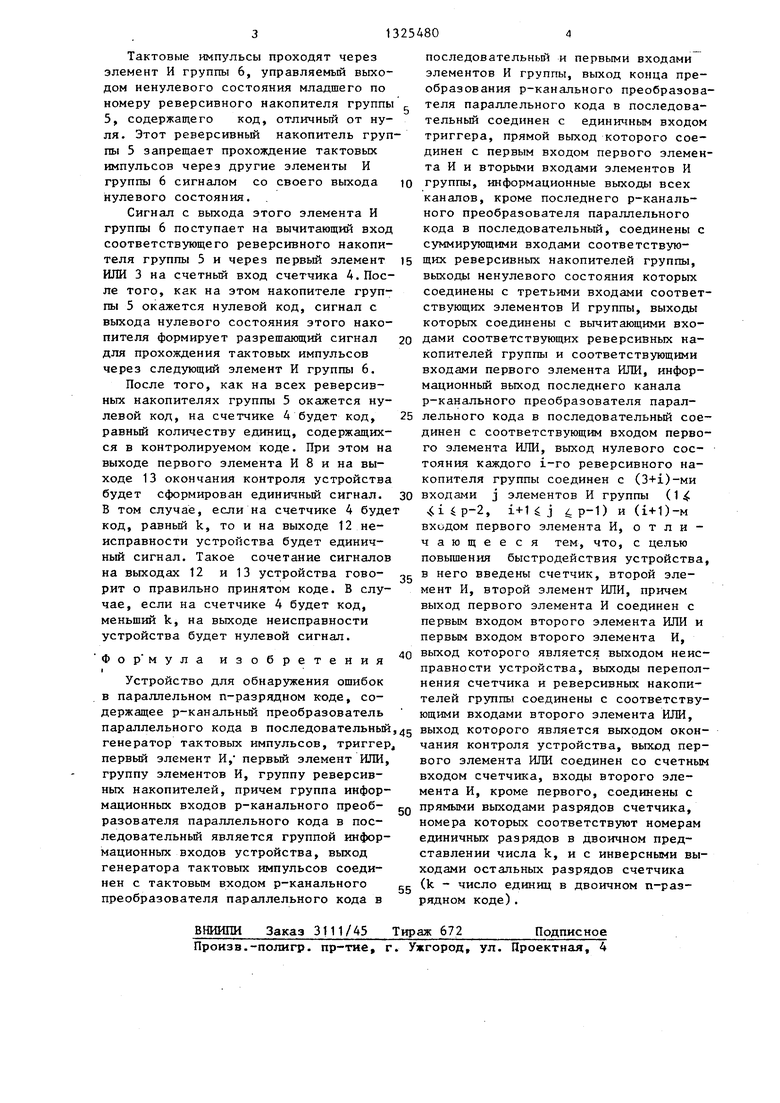

На чертеже приведена функциональная схема устройства для обнаружения ошибок в параллельном п-разрядном коде.

Устройство содержит генератор 1 тактовых импульсов, р-канальный преобразователь 2 параллельного кода в последовательный, первый элемент ИЛИ 3, счетчик 4, группу 5 реверсивных накопителей, группу 6 элементов И, триггер 7, первый элемент ИВ, второ элемент ИЛИ 9, второй элемент И 10, группу 11 информационных входов устройства, выход 12 неисправности устройства, выход 13 окончания контроля устройства.

На выходах переполнения счетчика 4 и реверсивных накопителей группы 5 единичный сигнал формируется при наличии в счетчике 4 или реверсивных накопителях группы 5 кода (k+D, где k количество единиц в двоичном п-разрядНом коде.

Устройство работает следующим образом.

В исходном состоянии счетчик 4, реверсивные накопители группы 5 и триггер 7 находятся в нулевом состоянии. В р-канапьный преобразователь 2

ИЛИ 9 пройдет на выход 13 окончания контроля устройства. Если при этом на счетчике окажется код, равный k - числу единиц в контролируемом коде, то на выходе 12 неисправности устройства через второй элемент И 10 также появится единичный сигнал, говорящий о правильном приеме кода. Наличие нулевого сигнала на выходе 12 устройства при единичном сигнале на выходе 13 устройства говорит о неправильном приеме кода. 1 ил.

параллельного кода в последовательный записан контролируемьй код.

По окончании преобразования сигнал с выхода конца преобразователя р-ка- нального преобразователя 2 параллельного кода в последовательный устанавливает в единичное состояние триггер 7, и после этого до конца контроля на информационных выходах всех каналов преобразователя 2 присутствуют только нулевые сигналы. К концу преобразования на счетчике 4 и в реверсивных накопителях группы 5 оказываются коды, равные количестве единиц, поступивших по каждому из каналов.

Если на счетчике 4 или в одном из реверсивных накопителей группы 5 окажется код, больший чем k, на выходе переполнения соответствующего узла будет единичный сигнал и на выходе 13 окончания контроля устройства появится единичный сигнал. При этом на выходе 12 неисправности устройства будет нулевой сигнал. Такое сочетание сигналов на выходах 12 и 13 устройства означает, что количество единиц в контролируемом коде больше разрешенного.

В том случае, когда по окончании преобразования ни в одном из каналов р-канального преобразователя 2 параллельного кода в последовательный не окажется более k единиц, но хотя бы в одном из реверсивных накопителей группы 5 будет код, отличный от нуля начинается подсчет единиц на счетчике 4.

Тактовые импульсы проходят через элемент И группы 6, управляемый выходом ненулевого состояния младшего по номеру реверсивного накопителя группы 5, содержащего код, отличный от нуля. Этот реверсивный накопитель группы 5 запрещает прохождение тактовых импульсов через другие элементы И группы 6 сигналом со своего выхода нулевого состояния.

Сигнал с выхода этого элемента И группы 6 поступает на вычитающий вход соответствующего реверсивного накопителя группы 5 и через первый элемент ИЛИ 3 на счетный вход счетчика 4. После того, как на этом накопителе группы 5 окажется нулевой код, сигнал с выхода нулевого состояния этого накопителя формирует разрешающий сигнал для прохождения тактовых импульсов через следующий элемент И группы 6.

После того, как на всех реверсивных накопителях группы 5 окажется нулевой код, на счетчике 4 будет код, равный количеству единиц, содержащихся в контролируемом коде. При этом на выходе первого элемента И 8 и на выходе 13 окончания контроля устройства будет сформирован единичный сигнал. В том случае, если на счетчике 4 буде код, равный k, то и на выходе 12 неисправности устройства будет единичный сигнал. Такое сочетание сигналов на выходах 12 и 13 устройства гово- рит о правильно принятом коде. В случае, если на счетчике 4 будет код, меньщий k, на выходе неисправности устройства будет нулевой сигнал.

Фор мула изобретения I

Устройство для обнаружения ошибок

в параллельном п-разрядном коде, содержащее р-канальный преобразователь параллельного кода в последовательный генератор тактовых импульсов, триггер первый элемент И, первьй элемент ИЛИ, группу элементов И, группу реверсивных накопителей, причем группа информационных входов р-канального преоб- разователя параллельного кода в последовательный является группой информационных входов устройства, выход генератора тактовых импульсов соединен с тактовьм входом р-канального преобразователя параллельного кода в

ВНИИПИ Заказ 3111/45 Тираж 672Подписное

Произв.-полигр. пр-тяе, г. Ужгород, ул. Проектная, 4

последовательный и первыми входами элементов И группы, выход конца преобразования р-канального преобразователя параллельного кода в последовательный соединен с единичным входом триггера, прямой выход которого соединен с первым входом первого элемента И и вторыми входами элементов И группы, информационные выходы всех каналов, кроме последнего р-канального преобразователя параллельного кода в последовательный, соединены с суммирующими входами соответствующих реверсивных накопителей группы, выходы ненулевого состояния которых соединены с третьими входами соответствующих элементов И группы, выходы которых соединены с вычитающими входами соответствующих реверсивных накопителей группы и соответствующими входами первого элемента ИЛИ, информационный выход последнего канала р-канального преобразователя параллельного кода в последовательный соединен с соответствующим входом первого элемента ИЛИ, выход нулевого состояния каждого i-ro реверсивного накопителя группы соединен с (3+1)-ми входами j элементов И группы (1 4 14р-2, 1+1 j 4 р-1) и (i+1)-M входом первого элемента И, отличающее ся тем, что, с целью повышения быстродействия устройства в него введены счетчик, второй элемент И, второй элемент ИЛИ, причем выход первого элемента И соединен с первым входом второго элемента ИЛИ и первым входом второго элемента И, выход которого является выходом неисправности устройства, выходы переполнения счетчика и реверсивных накопителей группы соединены с соответствующими входами второго элемента ИЛИ, выход которого является выходом окончания контроля устройства, выход первого элемента ИЛИ соединен со счетным входом счетчика, входы второго элемента И, кроме первого, соединены с прямыми выходами разрядов счетчика, номера которых соответствуют номерам единичных разрядов в двоичном представлении числа k, и с инверсными выходами остальных разрядов счетчика (k - число единиц в двоичном п-разрядном коде).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1986 |

|

SU1401461A1 |

| Пороговый элемент | 1984 |

|

SU1277370A1 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Устройство для преобразования двоичного кода по модулю К | 1987 |

|

SU1587641A1 |

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения устройств передачи и переработки дискр ет- ной информации. Цель изобретения - по- вьшение быстродействия устройства. По информационным входам устройств 12 Ю группы 11 в р-канальный преобразователь 2 параллельного кода в последовательный записывается контролируемый код. Преобразование осуществляется с помощью сигналов генератора 1 тактовых импульсов. Количество единиц, содержащихся в каждом из каналов преобразователя 2, кроме последнего, подсчитывается реверсивными накопителями группы 5, а количество единиц в последнем канале преобразователя 2 - счетчиком 4 через первый элемент ИЛИ 3. По окончании преобразования уста- навливается в единичное состояние .13 с $ сл

Авторы

Даты

1987-07-23—Публикация

1986-03-06—Подача