127

5 параллельного кода в последовательный, реверсивных накопителей 6 1...б-(р-1), группу р-1 элементов И 7, триггера 8 и элемента ИШ 9 обеспечивается предварительный подсчет числа единичных логических сигналов в группах входов с помощью реверсивных накопителей и последующий их пересчет в счетный блок 2, что исключает необходимость последова

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации.

Цель изобретения - noBbmjeHHe быст родействия за счет предварительного подсчета количества единичных сигналов на группах входов устройства, а также расширение функциональных возможностей за счет обеспечения реализации пороговых функций с отрицатель ; ными весами .

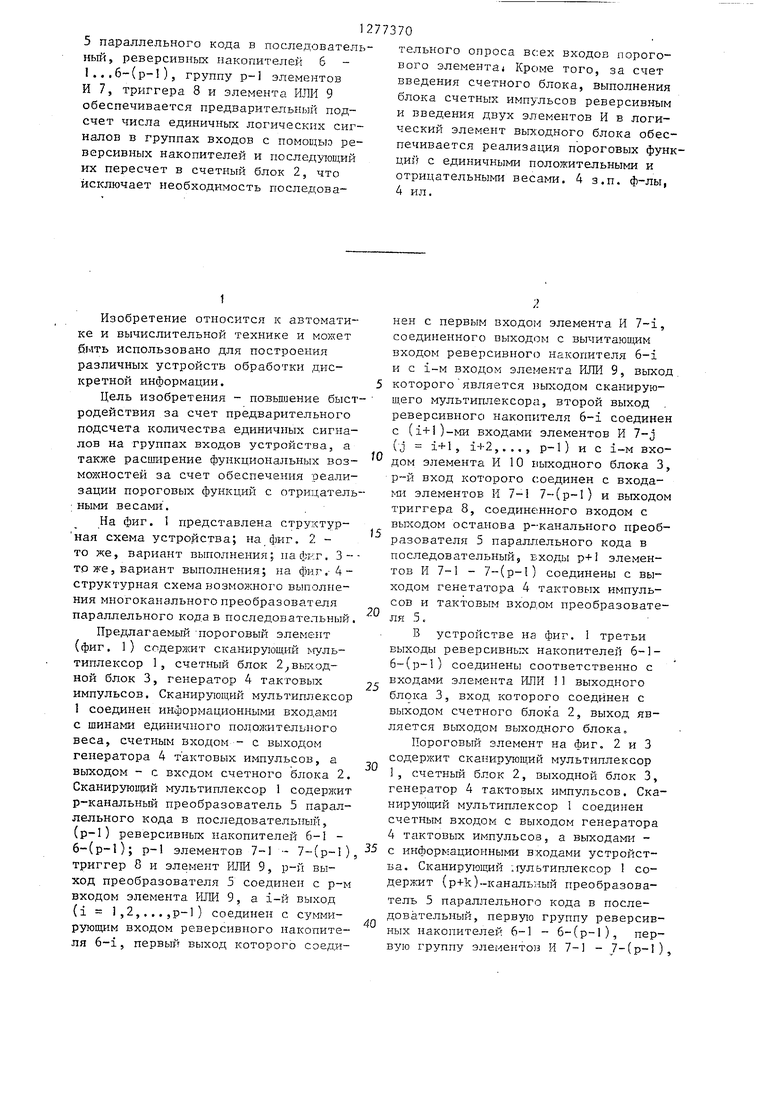

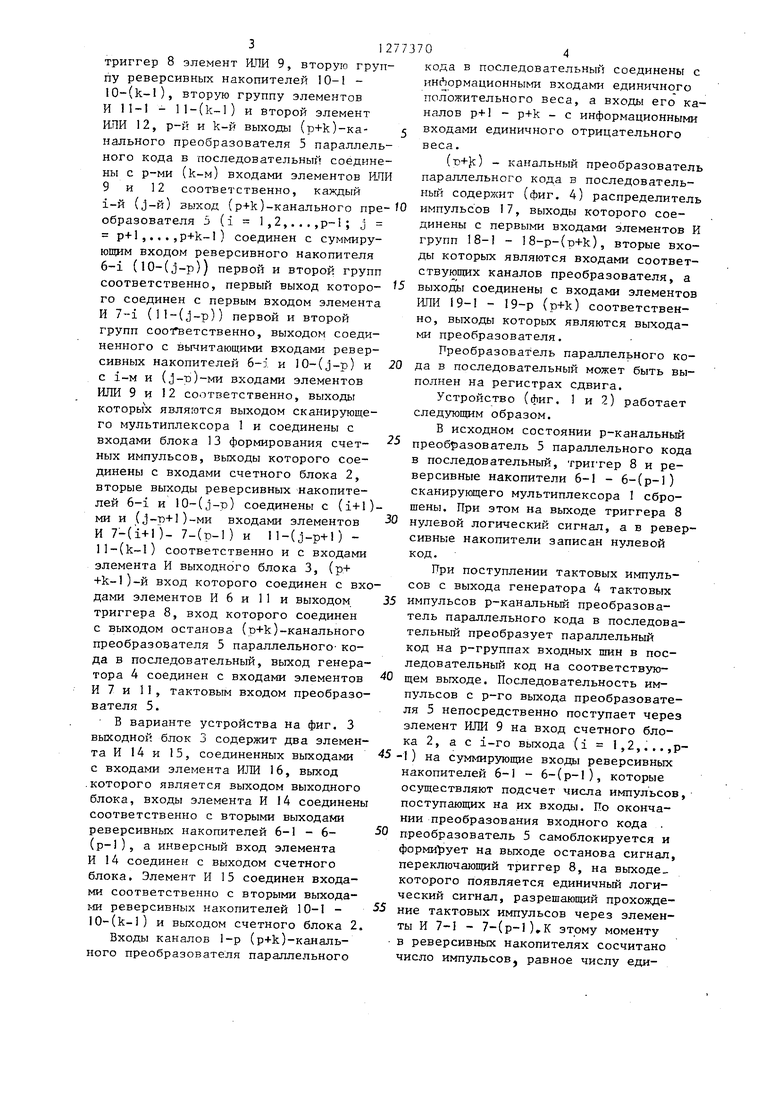

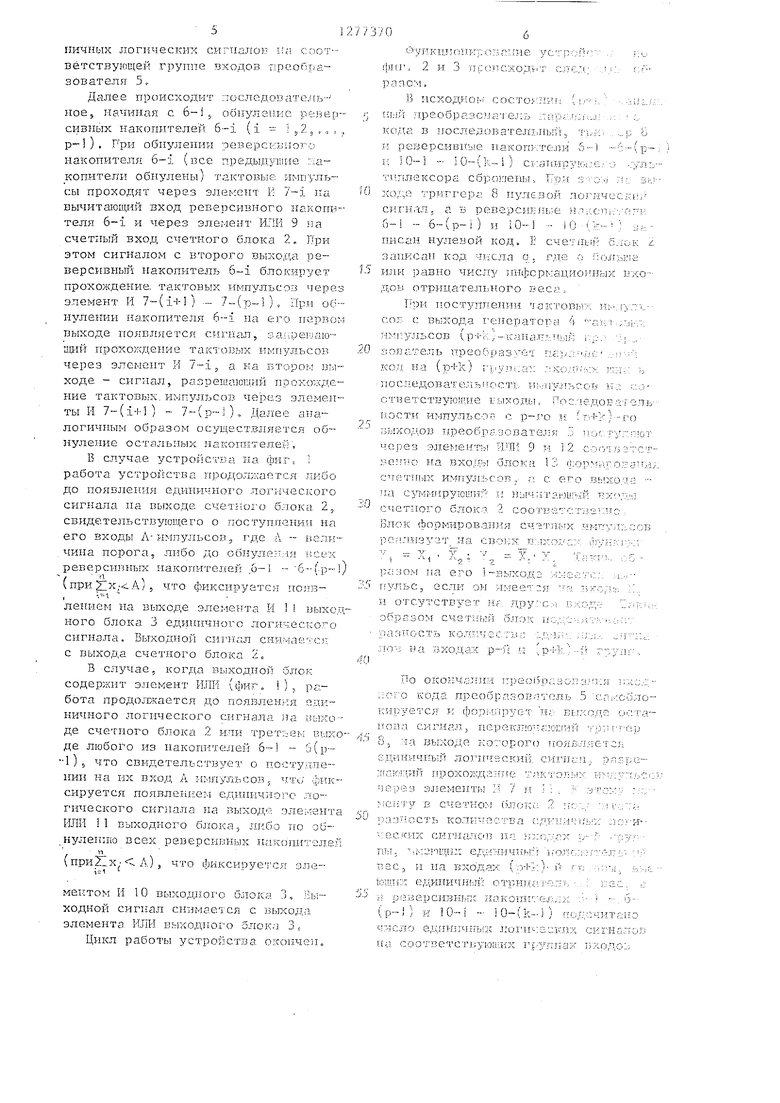

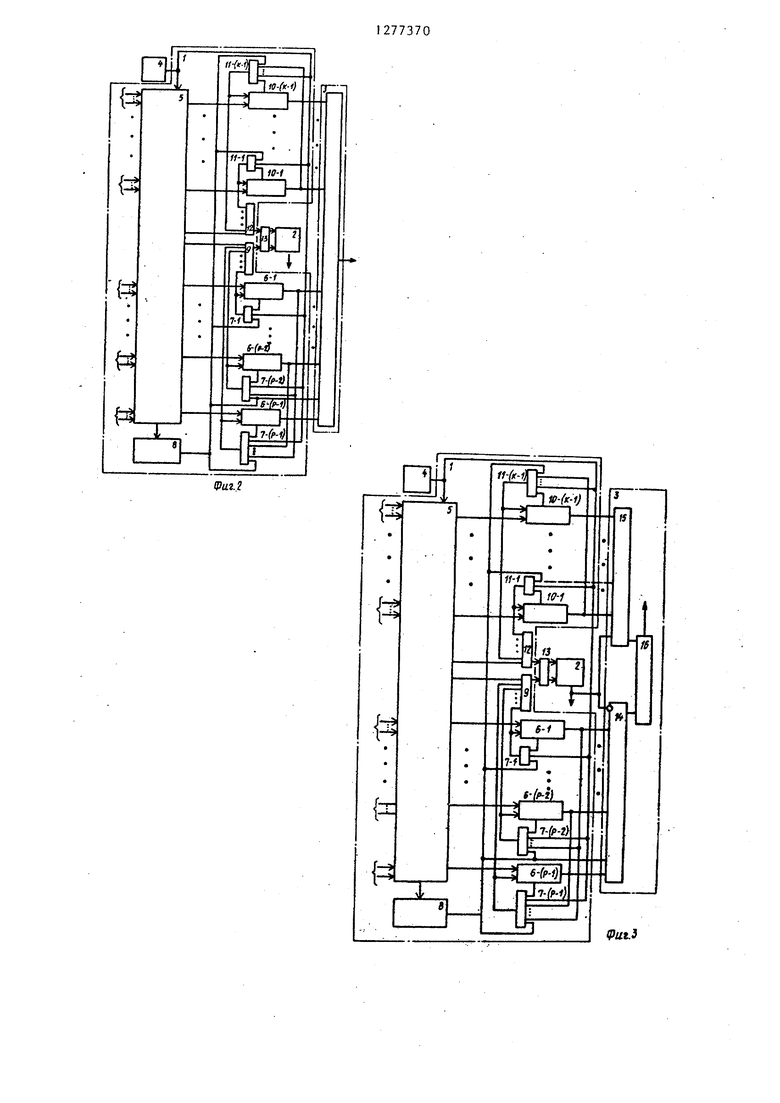

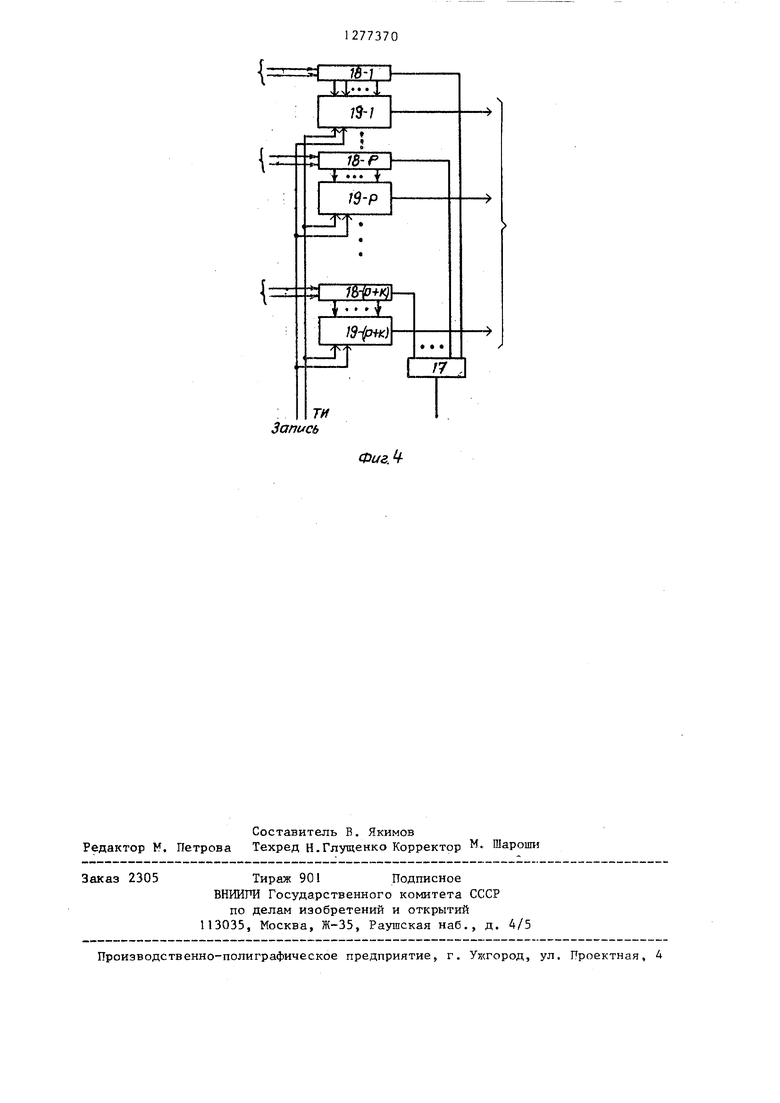

На фиг. I представлена структур- ная схема устройства; на фиг. 2 - то же, вариант выполнения; нафнг. 3то же, вариант выполнения; на фиг,-4- структурная схема возможного выполнения многоканального преобразователя параллельного кода в последовательный

Предлагаемый пороговый элемент (фиг. 1) содерлшт сканиругощий -гуль- типлексор 1, счетный блок 2 выходной блок 3, генератор 4 тактовых импульсов. Сканирующий мультиплексор 1 соединен информационными входами с шинами единичного положительного веса, счетным входом - с выходом генератора 4 тактовых импульсов, а выходом - с входом счетного блока 2. Сканирующий гультиплексор 1 содержит р-канальный преобразователь 5 параллельного кода в последовательный, (р-1) реверсивных накопителей 6-1 - 6-(р-1); р-1 элементов 7-1 - 7-(р-1) триггер 8 и элемент ИЛИ 9, р-й выход преобразователя 5 соединен с р-м входом элемента ИЛИ 9, а 1-й выход (1 ,2,...,р-1) соединен с сумми

рующим входом реверсивного накопителя 6-i, первый выход которого соеди370

тельного опроса вс:ех входов порогового элемента Кроме того, за счет введения счетного блока, выполнения блока счетных импульсов реверсивным и введения двух элементов И в логический элемент вьгеодного блока обеспечивается реализация пороговых функций с единичными положительными и отрицательными весами, 4 з.п. ф-лы, 4 ил.

О

5

5

5 ,,

0

0

нен с первым входом элемента И 7-1, соединенного выходом с вычитающим входом реверсивного накопителя 6-1 и с 1-м входом элемента ИЛИ 9, выход, которого является выходом сканирующего мультиплексора, второй выход реверсивного накопителя 6-1 соединен с (1+1)-ми входами элементов И 7-j (j i+1, i+2,..., р-1) и с i-M входом элемента И 10 выходного блока 3, вход которого (соединен с входами элементов И 7-1 7-(р-1) и выходом триггера 8, соединенного входом с выходом останова р-канального преобразователя 5 параллельного кода в последовательный, р+1 элементов И 7-1 - 7-(р-1) соединены с выходом генетатора 4 тактовых импульсов и тактовым входом преобразователя 5,

В устройстве на фиг. 1 третьи выходы реверсивных накопителей 6-1- 6-(р-1) соединены соответственно с входами элемента ИЛИ 11 выходного блока 3, вход которого соединен с выходом счетного блока 2, выход является выходом выходного блока.

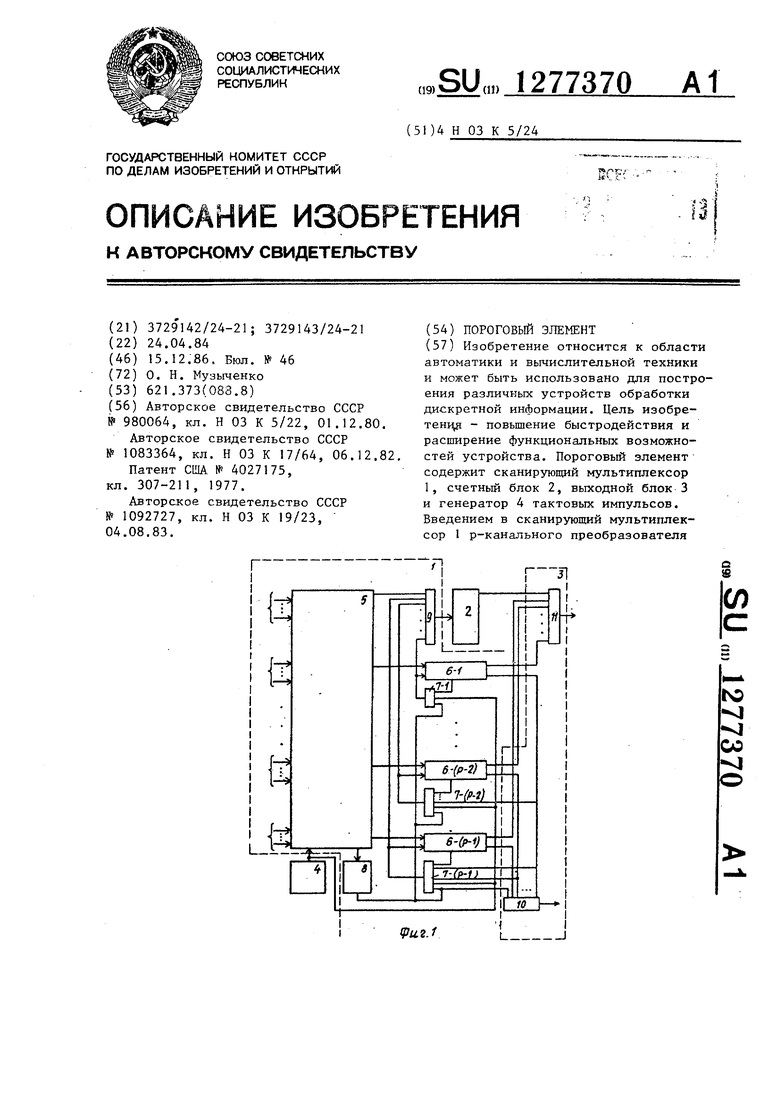

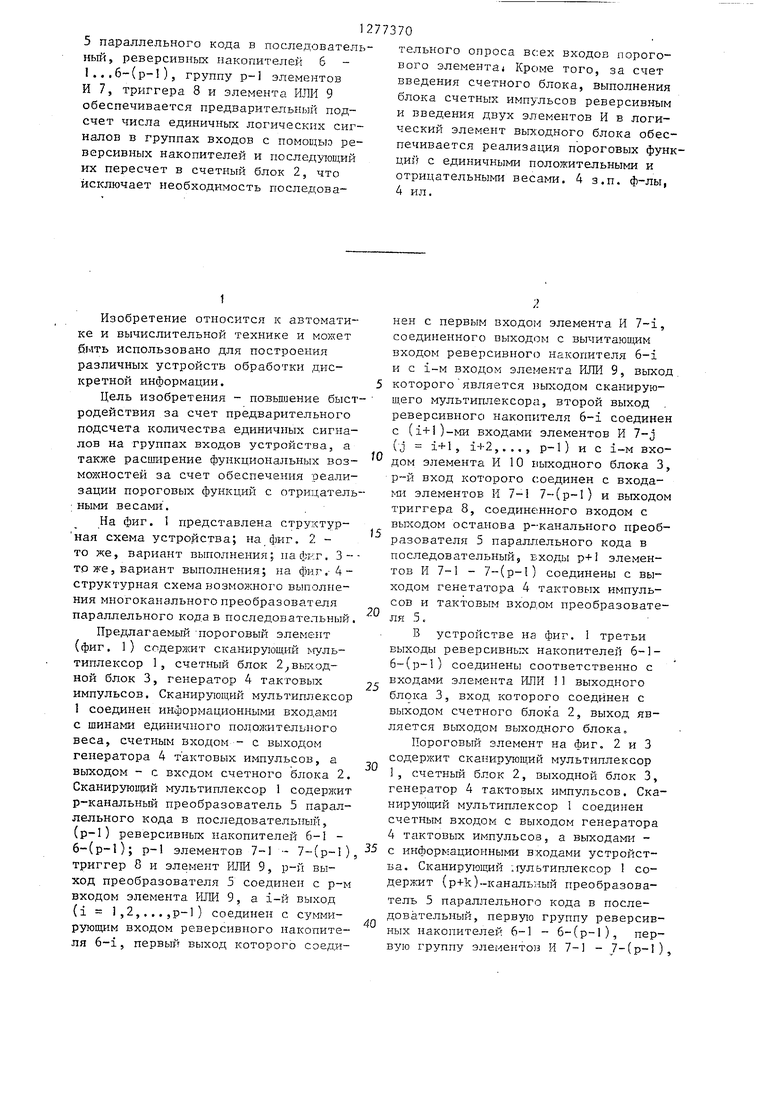

Пороговый элемент на фиг. 2 и 3 содержит сканирующий мультиплексор 1, счетный блок 2, выходной блок 3, генератор 4 тактовых импульсов. Сканирующий мультиплексор 1 соединен счетным входом с выходом генератора 4 тактовых импульсов, а выходами - с информационными входами устройства. Cкaниpyю ПJ й ;гулбтиплексор 1 содержит (p+k)-канальный преобразователь 5 параллельного кода в последовательный, первую группу реверсивных накопителей 6-1 - б-(р-1), первую группу элементов И 7-1 - 7(),

триггер 8 элемент ИЛИ 9, вторую группу реверсивных накопителей 10-1 - lO-(k-l), вторую группу элементов И 11-1 - ll-(k-) и второй элемент ИПИ 12, р-й и k-й выходь (p+k)-канального преобразователя 5 параллельного кода в последовательный соединены с р-ми (k-м) входами элементов ИЛИ 9 и 12 соответственно, каждый

15

i-й (j-й) выход (p+k)-кaнaльнoгo пре- О импульсов 17, выходы которого сое- образователя 3 (1 1,2,...,р-1; j р+1,...,p+k-I) соединен с суммирующим входом реверсивного накопителя 6-i (lO-(j-p}) первой и второй групп соответственно, первый выход которого соединен с первым входом элемента И 7--i (n-(j-p)) первой и второй групп соответственно, выходом соединенного с вьмитающими входами реверсивных накопителей 6-1 и lO-(j-p) и с i-M и (j-p)-MH входами элементов ИЛИ 9 и 12 соответственно, выходы которых являются выходом сканирующего мультиплексора 1 и соединены с входами блока 13 формирования счетных импульсов, выходы которого соединены с входами счетного блока 2, вторые выходы реверсивных накопителей 6-i и lO-(j-p) соединены с (i+l)- ми и (j-p+1 )-ми входами элементов - И 7-(i-n )- 7-(р-1) и ll-(j-p+l) - ll-(k-l) соответственно и с входами элемента И выходного блока 3, (р+ +k-l)-й вход которого соединен с вхо20

25

динены с первыми входами эл ементов групп 18-1 - 18-p-(p+k), вторые вхо ды которых являются входами соответ ствующих каналов преобразователя, а выходы соединены с входами элементо ИЛИ 19-1 - 19-р (p+k) соответственно, выходы которых являются выходами преобразователя.

Преобразователь параллельного ко да в последовательный может быть вы полнен на регистрах сдвига.

Устройство (фиг. 1 и 2) работает следующим образом.

В исходном состоянии р-канальный преоб азователь 5 параллельного кода в последовательный, триггер 8 и реверсивные накопители 6-1 - 6-(р-1) сканируицего мультиплексора 1 сброшены. При этом на выходе триггера 8 нулевой логический сигнал, а в ревер сивные накопители записан нулевой код.

При поступлении тактовых импульсов с выхода генератора 4 тактовых 35 импульсов р-канальный преобразователь параллельного кода в последова- тельньй преобразует параллельный код на р-группах входных шин в последовательный код на соответствую- 40 щем выходе. Последовательность импульсов с р-го выхода преобразователя 5 непосредственно поступает через элемент ИЛИ 9 на вход счетного блока 2, ас i-ro выхода (1 1,2,...,р 5 -1) на суммирующие входы реверсивных накопителей 6-1 - 6-(р-1), которые осуществляют подсчет числа импульсов поступающих на их входы. По окончании преобразования входного кода . 50 преобразователь 5 самоблокируется и форми зует на выходе останова сигнал, переключающий триггер 8, на выходе которого появляется единичный логический сигнал, разрещающий прохожде- 55 ние тактовых импульсов через элементы И 7-1 - 7-(р-1)К зтрму моменту в реверсивных накопителях сосчитано число импульсовJ равное числу едидани элементов И 6 и 11 и выходом триггера 8, вход которого соединен с выходом останова (p+k)-канального преобразователя 5 параллельного- кода в последовательный, выход генератора 4 соединен с входами элементов И 7 и 11, тактовым входом преобразователя 5.

В варианте устройства на фиг. 3 выходной блок 3 содержит два элемента И 1 4 и 1 5 , соединенных выходами с входами элемента ИЛИ 16, выход .которого является выходом выходного блока, входы элемента И 14 соединены соответственно с вторыми выходами реверсивных накопителей 6-1 - 6- (р-1), а инверсный вход элемента И 14 соединен с выходом счетного блока. Элемент И 15 соединен входами соответственно с вторыми выходами реверсивных накопителей 10-1 - lO-(k-l) и выходом счетного блока 2.

Входы каналов -р (p+k)-кaнaль- ного преобразователя параллельного

кода в последовательный соединены с инЛормационными входами единичного положительного веса, а входы его каналов р+1 - p+k - с информационными входами единичного отрицательного веса.

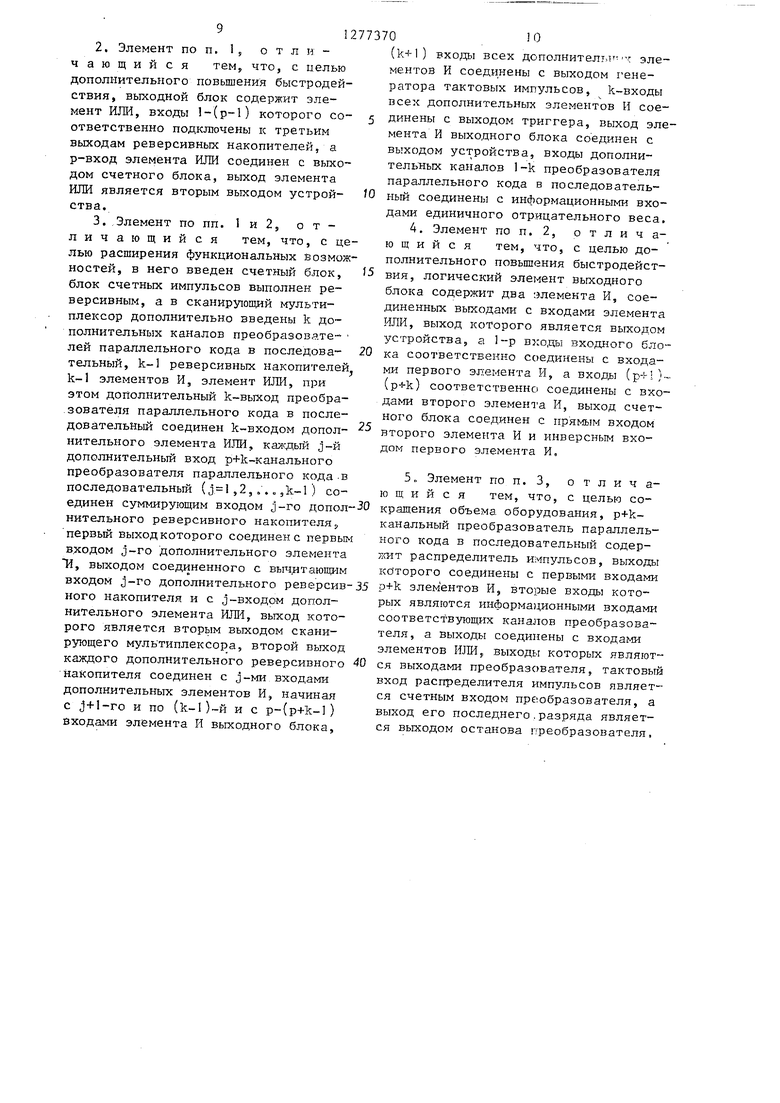

(т)+}с) - канальный преобразователь параллельного кода в последователь- пьй содержит (фиг. 4) распределитель

15

О импульсов 17, выходы которого сое- -

20

25

динены с первыми входами эл ементов И групп 18-1 - 18-p-(p+k), вторые входы которых являются входами соответствующих каналов преобразователя, а выходы соединены с входами элементов ИЛИ 19-1 - 19-р (p+k) соответственно, выходы которых являются выходами преобразователя.

Преобразователь параллельного кода в последовательный может быть выполнен на регистрах сдвига.

Устройство (фиг. 1 и 2) работает следующим образом.

В исходном состоянии р-канальный преоб азователь 5 параллельного кода в последовательный, триггер 8 и реверсивные накопители 6-1 - 6-(р-1) сканируицего мультиплексора 1 сброшены. При этом на выходе триггера 8 нулевой логический сигнал, а в реверсивные накопители записан нулевой код.

При поступлении тактовых импульсов с выхода генератора 4 тактовых 5 импульсов р-канальный преобразователь параллельного кода в последова- тельньй преобразует параллельный код на р-группах входных шин в последовательный код на соответствую- 0 щем выходе. Последовательность импульсов с р-го выхода преобразователя 5 непосредственно поступает через элемент ИЛИ 9 на вход счетного блока 2, ас i-ro выхода (1 1,2,...,р- 5 -1) на суммирующие входы реверсивных накопителей 6-1 - 6-(р-1), которые осуществляют подсчет числа импульсов, поступающих на их входы. По окончании преобразования входного кода . 0 преобразователь 5 самоблокируется и форми зует на выходе останова сигнал, переключающий триггер 8, на выходе которого появляется единичный логический сигнал, разрещающий прохожде- 5 ние тактовых импульсов через элементы И 7-1 - 7-(р-1)К зтрму моменту в реверсивных накопителях сосчитано число импульсовJ равное числу едимичных логических сигиалок i;;i соответствующей njiynne входов -преопр - 3 сват ел я 5,Далее происходит последоватоль-- HOGj начиная с б-, обнуление сизных накопителей 6-1 (i 1,2.,,,,, р-1 ) , Гри обнулении реверскиногс накопителя (все предыдущие накопители обнулены) тактотзые импульсы проходят через элемент И 7-i на вычитающий вход реверсивного накопителя 6-i и через элемент ИЛИ 9 lia счетный вход счетного блока 2. При этом сигналом с второго выхода ре- версивньш накопитель блокирует нрохождение. тактовьк импульсов через элемент И 7-(i+l ) - 7--(p-l), При обнулении иаконителя 6-i на его нерве; выходе появляется сигнал, saiipepjaio™ щий прохождение тактовых импульсов через элемент И 7-i, а на второг.; вгл- ходе - сигнал, разрешазощий прохопде- ние тактовых. имп:/льсов через элементы И 7(i+i) - 7--{р -0 Далее аналогичным образом осуществляется обнуление остальных накопителей,

В случае устройства на фиг, 1 работа устройства продолжается либо до появления единичног о ло1 1-1ческого сигнала на вьжодв ечетно1 о б.юка 2, сви7детельствующего о поступлении на его входы Л-HMnyJH-jCOB э т де Л -- lieai-i- чина порога, либо до обнуле;1:1я всех реверсивных накопителей о-1 - 6--.p / 1

(, при 21X ,-с А / 5 ч т о фик СИР у а т с я по я 3 - I

лением на выходе элемента И 1 выхоного блока 3 единичного логического снгнала. Выходной си.гнал сни;- ае -с:.я- с выхода счетного блока 2,

В случае, когда выходной блок содержит элемент ИЛИ (фиг. ), работа продоо скается до появлеН Гя единичного логического сигнала на выходе счетного блока 2 третьем де любого из н аконителей 6-1 - 5(р- 1) 5 что свидетельствует о постз 1тле- нии на их вход А Ii пyльcoв5 чти сируется появлением едипичног с ло-- гнческово сигнала на выходе элеь-ент ИЛН 11 выходного блока, либо по об- нулен;1ю всех реверсивных наусопителе

(при21х; А,) , что Фикси1:)уе ; ся эле-

меитом И 10 выходного блока 3, Нь;- ходной сигнал снимается с выхода элемента ИЛИ вьгходног о блока 3, Цикл работы устройства окон-чеи.

73706

йункн.г;они1:овапие устр-;; :: . г.и

1ИГ, 2 и 3 ТТ ;г;ЛСлОД5.Т .5,:, а а о . Л,

В исходнот- еосто;- :;1И11 ( .л;.;../;:

преобразсва |-ель :vapa,r/:fi.j; :: ;, кода в последователиплй; ТЬ ;-:;. .-р о и реверсивные накопители S) .( и 10-i - iO--(k-) ст-:ат1,.:е; „) .:ул:;:- типлексора ебр Я гепы. Гри s vo-.j yu. зь

I ходе триггера 8 пулевой логичес;: с, сиг-нал, а в реверси1;ньш лксал- /ег:- 6-i - 6-() и iO--l - iO (-i ; jfc- нисан нулевой код. Е сче-лгый б-;ик z записан код числа а. где о ;;оль;:1е

шн paBiio числу 1нформадионнь Х кло- ,Г|, О в ci т р и д а т е л ij н о г о в е с а.

npps поетуппегпп- ч актовых H;.. f.oB с геператора 4 vriA : .;j;;.v импульсов I,р-1-ь;.;- 1санаЛ;л: : 1Й ivp. .:...,0 аова.тель иреобразуо г nii j-;- ii.f: ,:; : кол на (p-i-k) rijynuax лхоиг-:.:;--: j-rn: ъ поспедователь тос ь гл-пульсов кл стветству Опчге выходы , По следов aieniiПОСТИ ИМПУЛЬСОО с р-ГО и

i.

БЬ ходов иреоЬрс.зователУ j нос т -угпют

че|5ез элементы ЯШ1 9 T-I 12 COO IB TCT- ве пк на входы бхюка 13 а;орми1 о: э и-ь счетных имгп)ьсов, а с его выхо/ла - иа е-уммгфуюии:- п выч:1Та1ои:;-.;й

- - сч;етиого блока 2 соотЕе ; ет;зе л:10

Блок формирования счетн:о х им гул::.сов реализует на в::1;; о.ва: ш ун.- . г: -:; i - м Z - 1 а-ам., ло - i5a;iONi п,а его 1-вь|Ход2 i:-;eevi:;. :i,.,, пульс, если он и уее тпя ;. ,::; 3, и отсутствует Hf. дру.: с.- вход ..: образом счетиг,1й блок ио, ::,.;-; -- .:;Х . разность количесгв;- . VBi .. , :j:;i.-. ,л1-л:.,.

.)-.; на входах и .v+ti -i t rnyiir , f У

По окончатгии гтт еобразопа-ауя вх;.:,:;- хог-о кода. преобразов;вгель 5 сгичсбло- кируется и форм;п:)ует н;- вь.:;чоде cii:viVH нова сигнал. riepeKJ JioxaJOLfvn r грх :р;Ч 1

8, ча выходе которого появляется Дl-пiичнь;й лот ический. сигпсл рязр г- лшю дий прохождение . т- : ;;;у;т.осз перез элементы П 7 и Г: . - ::гго:-:;.- :.зл :чС:Гг г Е с- -;етгГо:- (хпотс;; 2 п;: :. : i i...;-;;.;

разность кол1-в;ества едквизвь;:: :ес. сиг налс В иа .ч::х зру/- пы- еди:г1ичН 1гг 1гп,г;г.;;з.: гел ;. ; . вес, и на входах /п-ь)-й -в зг,;, .з-.х. 01цих единичньгй отрИ1лаг-з.лв ; . ;

- и реверсивньп; накопителя; ;: . - iV- (р-1) и Ш-i - .i) под;;читйно ч;чсло единич гь ;к ло1 ис:езких си:т1а.яов на соответст1;ую11;их группах 5ходо:;

/

СДИПИ чИого iVOJ O,.,;; re. (.:;,

тельного; ijiioa,Далее в яз груп;, jicu.

телек б-i - 6-vp :) и 10-1 - :. ::.- параллель} - :;.,.,-:;;.,1,.г: г;осле,:,сио . ij;., iJOG ooHyjitiii-i;:; ;ii:ii-.0 THTeriei-;. npif зт::-

импульсь с выАОдов злемеиаов ID iH 9 i: 12 поступают на входы блока 13 фор.л;

розания с;четпьп1 Яг-гпульсов, но ; ..

Л(Ь.;ХОД iic- ITpOAiJ,-:. ; i. riOKi;:. ОД)йа ;:3 ЧД;

с ОЯ У-:Ю Ui-t/i Ь О|. ..j /pV jjYbi Vt ;чиуЛ :vCt. ).

дут ИиС L ула J у j С; ОП йГ1;Гь ;,,. ;. .

элеменч Ilflfi у пди 12 и с/юк ij форД .- рованкя CMGTHi.: и,п:ульсов да c: M:iL ОукИДиЙ или БЫЧИТаиИТГЙ ЕХОдЫ C4t; V:-;C

го 6j o:;:a 2 соотве с I sebiic,, ; ото;п- ; ; . ИИ подсчет,

--- pd-OC;ia jlpu,L,.O-LJ Kcici4 C i Д, v-O:i

ле.,1,т;; Всех piibepCHBiibjx; --1с1ь:оп;;лч;ле;- ) фикси:;у 1 с ас. iaettiieM едлто -;

глемекта I ; :лодь10 о блока, Резул, J работа ;;ро,должается до :y::-::i г--й БЬДСС-Д iv .:.Д;, ;::i-:- ro преДс;р. пока все накопители 6-1 - 6- о5ргзо;;йтеля тгараллйльпо о кода в

(р- I ) не об}1ул(и ись и на ньжолк. Лто . лосдедоБательи::, :: Д; . .р i

яого блока 2 кулевок логическ .-ш , -С-,.;:р,инен с cyi.:: u;pyi, .:;Д.- .ч j.-ro

.11реверс:.йног.; г :: vi- ус,л - i: L.:: :i--i: ,::. j

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Пороговый элемент | 1985 |

|

SU1297220A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Пороговое устройство (его варианты) | 1984 |

|

SU1352449A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Устройство для обнаружения ошибок в равновесном коде К из @ | 1987 |

|

SU1564731A1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано для построения различных устройств обработки дискретной информации. Цель изобре- тенця - повышение быстродействия и расширение функциональных возможностей устройства. Пороговый элемент содержит сканирующий мультиплексор 1, счетный блок 2, выходной блок 3 и генератор 4 тактовых импульсов. Введением в сканирующий мультиплексор 1 р-канального преобразователя (Л с

.Ц;. фиксдруются с...;-и; :: о 1я-л:;;ЯИ1 /яя. . ..

мeJ lтa iн И выходного блока;, что ззызпг- - K;:V. .-jrc i-го ,,.:о:,;

вао С поязлениа едпяичяого догкческо ля cce;i;-;HSAi с д-мк Бходахи оле

го сигнала на его элементамея /ов И,, яачияая с (i-;-l)ro п по

ИЛИ, СЕидетеллствукщего об окончании(p--l;.д п с сос ; :- етст- -о:И Ь;: )

работы доро;чзя;:го эле1; н;а; Еляодно; яяиД.:.:-;- я,ло..,:Ял/ ( -ясчоулого Уя;.я1.

ctirHa,Jf С;;;д: аь я;,,. :j я.яхода яетнос о - р--зхсяр эле,-;ея а . .йь;хс цяого cjfc-яа

блока , -сооляяи-я с зхсяя.,:.. а.се:; э. . .я ,, :

Ция,) pauoi t: яяс „/jjjor . яс; ;.: :;.: я-.-ядя. : яяд сс -ч:л1 с;.

.я - ЯЯе11..,,.,;. , с ЛХ.:.ЯОЯ ;,Я: УПЯ; У 0-гояый 3j o --;enT оосспечивает повь-яяяяя - яяля. Сч.дн я ./я лЯ:. ,: гс;я. :1 Я ,, яxcяJ ;

:;:Ь иТ 1Ср Я;1с Я;;};; :- пг,Я-.:;:,заяя :я.. i-. .1.,.-Я „-;Я-я.;а,яг ,;л ; . : а: -. . и i . ; . .,-;-;,,; я; о я:я:д,-::яя; с--: -, еду/ь.-я-ялля j .- -.;-,v. .-,.-л Я:я яойр, ; ::я. ; , .;. : . :; ., .,

|-ЯЯ.1:;Я. 0.,Я,,;рС;,..л ;: . ЯаКОЯ;-. rSJt-i i :лI...:..:.,. ,.; р- Я . . .. ;;. 1,ЯЯ, IP Я1Я р;Яя:1 1яяясдуя;дзго пк я.,..яС 1ата У с че Я: ; ;: - Я.-УЯ я-, яаяяя/. , тя: яоя- я пяс: ецо

я-j .лядояа 1Я;.):1;:я:.. j олрюса ьсиз: яд :, бдсяга сся;Рся-;я. : я :1С:яо.:я; .Я: i / ПС;;. ояовяго элсс- с.ята :.ЯТБЯ 2.Элемент по п. 1, отличающийся тем, что, с целью дополнительного новьшения быстродействия, выходной блок содержит элемент ИЛИ, входы 1-(р-1) которого соответственно подключены к третьим выходам реверсивных накопителей, а р-вход элемента ИЛИ соединен с выходом счетного блока, выход элемента ИЛИ является вторым выходом устройства,

20

ностей, в него введен счетный блок, блок счетных импульсов выполнен реверсивным, а в сканирующий мультиплексор дополнительно введены k дополнительных каналов преобразователей параллельного кода в последовательный, k-1 реверсивных накопителей k-1 элементов И, элемент ИЛИ, при этом дополнительный k-вьгход преобразователя параллельного кода в последовательный соединен k-входом допол- нительного элемента ИЛИ, каиодый j-й дополнительный вход p+k-канального преобразователя параллельного кода-в последовательный (j l ,2, ... , .) со-30

127737010

(k-f-1) входа всех дополнител1, элементов И соединены с выходом генератора тактовых импульсов, k-входы всех дополнительных элементов И соединены с выходом триггера, выход элемента И выходного блока соединен с выходом устройства, входы дополнительных канапов 1-k преобразователя параллельного кода в последовательный соединены с информационными входами единичного отрицательного веса, 4, Элемент по п. 2, отличающийся тем, что, с целью дополнительного повышения быстродействия, логический элемент выходного блока содержит два элемента И, соединенных выходами с входами элемента ИЛИ, выход которого является выходом устройства, а 1-р вко.цы входного блока соответствекно соединены с входами первого элемента И, а входл (р-:- )- (p+k) соответственно соединены с входами второго элемента И, выход счетного блока соединен с прямым входом второго элемента И и инверсным входам первого элемента И,

J5

5 ,. Элемент по п. 3, ю щ и и с я тем, что.

о т л и ч а- с целью СОкрашения объема оборудования, p+k- канальный преобразователь параллельного кода в последовательный содер- лшт распределитель импульсов, выходы которого соединены с первыми входами

единен суммирующим входом j-ro дополнительного реверсивного накопителя,, первый выход которого соединен с первым входом j-ro дополнительного элемента И, выходом соединенного с вычитающим входом J-ro дополнительного реверсив-35 P+k элементов И, вторые входы кото- ного накопителя и с j-входом допол- рых являются информа1дионными входами

соответствующих каналов преобразователя, а выходы соединены с входами элементов ИЛИ, выходы которых являют- 40

нительного элемента ИЛИ, выход которого является вторым выходом сканирующего мультиплексора, второй выход каждого дополнительного реверсивного накопителя соединен с j-ми входами дополнительных элементов И, начиная с j+1-го и по (k-l)-й и с p-(p+ k- ) входами элемента И выходного блока.

ся выходами преобразователя, тактовый вход распредехсителя импульсов является счетным входом преобразователя, а выход его последнего.разряда является выходом останова преобразователя.

5 ,. Элемент по п. 3, ю щ и и с я тем, что.

о т л и ч а- с целью СОкрашения объема оборудования, p+k- канальный преобразователь параллельного кода в последовательный содер- лшт распределитель импульсов, выходы которого соединены с первыми входами

P+k элементов И, вторые входы кото- рых являются информа1дионными входами

соответствующих каналов преобразователя, а выходы соединены с входами элементов ИЛИ, выходы которых являют-

ся выходами преобразователя, тактовый вход распредехсителя импульсов является счетным входом преобразователя, а выход его последнего.разряда является выходом останова преобразователя.

lpia.2

IPUt.S

ФигЛ

| Пороговый логический элемент | 1980 |

|

SU980064A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пороговый элемент | 1982 |

|

SU1083364A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Пороговый элемент | 1982 |

|

SU1092727A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-12-15—Публикация

1984-04-24—Подача