СП

оэ

со

мпульсов, триггер 3, элементы ИЛИ 5, 1, счетный блок 6, реверсивные накопители 7, группу 8 элементов И и элементы И 9, 10. Благодаря введению

полусумматоров 4 и элемента ИЛИ 12 быстродействие устройства повышается до 30% по сравнению с прототипом. 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля равновесного кода К из @ | 1987 |

|

SU1559411A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1647871A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Устройство для контроля равновесного кода | 1987 |

|

SU1580563A1 |

| Пороговый элемент | 1986 |

|

SU1387185A2 |

| Устройство для подсчета числа единиц двоичного кода | 1987 |

|

SU1569995A1 |

| Устройство для контроля двоичного кода по модулю К | 1990 |

|

SU1737736A1 |

| Пороговый элемент | 1985 |

|

SU1297219A1 |

| Устройство для контроля количества единиц двоичного кода по модулю К | 1983 |

|

SU1357960A1 |

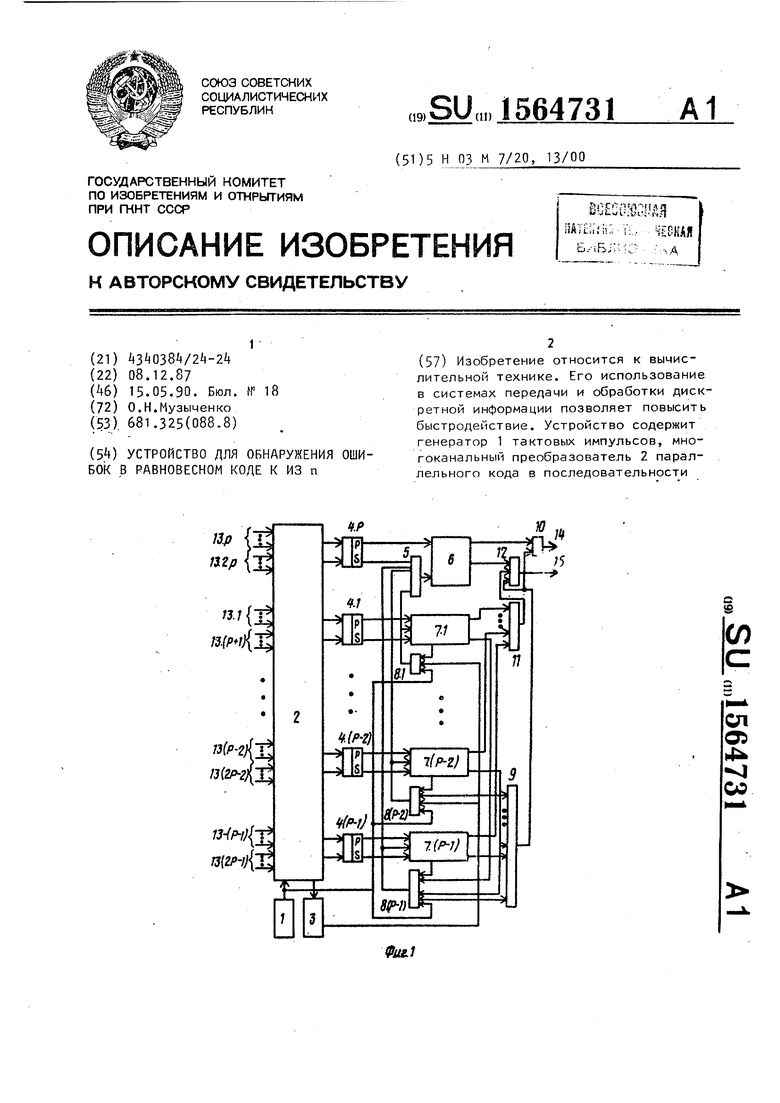

Изобретение относится к вычислительной технике. Его использование в системах передачи и обработки дискретной информации позволяет повысить быстродействие. Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательности импульсов, триггер 3, элементы ИЛИ 5,11, счетный блок 6, реверсивные накопители 7, группу 8 элементов И и элементы И 9,10. Благодаря введению полусумматоров 4 и элемента 12 ИЛИ быстродействие устройства повышается до 30% по сравнению с прототипом. 2 ил.

Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи и обработки дискретной информации. Цель изобретения - повышение быстродействия.

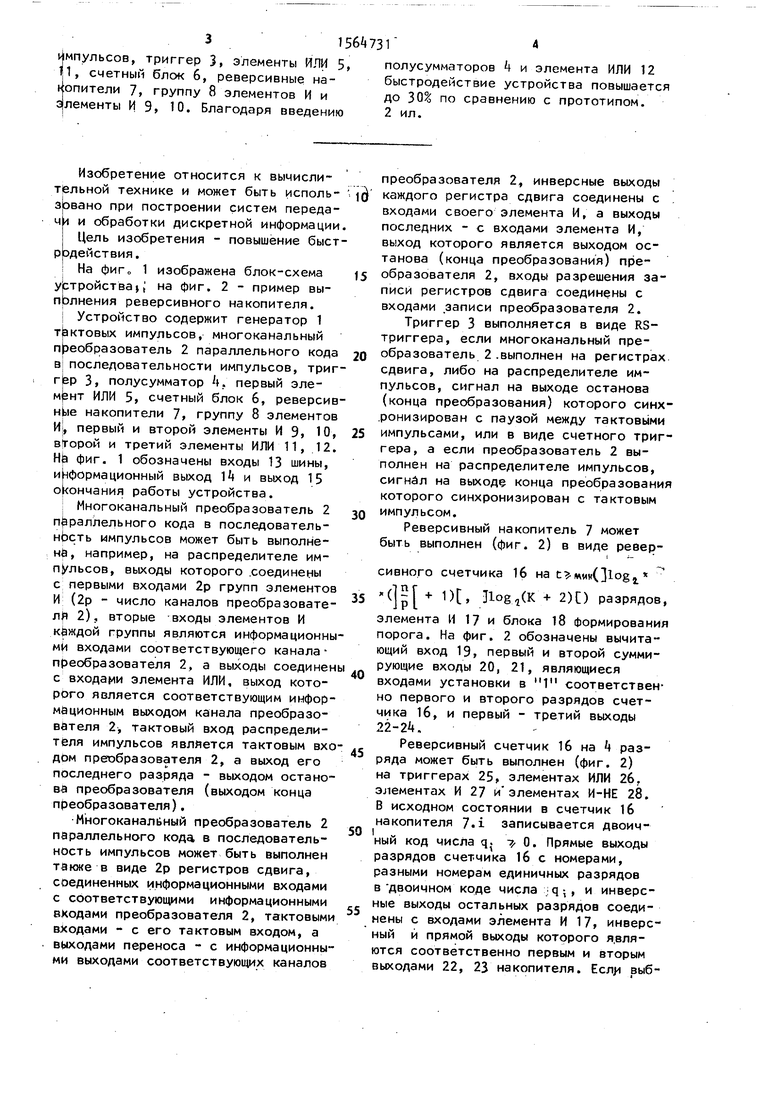

На фиго 1 изображена блок-схема устройства и на Фиг. 2 - пример выполнения реверсивного накопителя.

Устройство содержит генератор 1 тактовых импульсов, многоканальный преобразователь 2 параллельного кода в последовательности импульсов, rfep 3, полусумматор А. первый элемент ИЛИ 5, счетный блок 6, реверсивные накопители 7, группу 8 элементов И, первый и второй элементы И 9 Ю, второй и третий элементы ИЛИ 11, 12. На фиг. 1 обозначены входы 13 шины, информационный выход 1 и выход 15 окончания работы устройства.

Многоканальный преобразователь 2 параллельного кода в последователь- нЬсть импульсов может быть выполнена, например, на распределителе импульсов, выходы которого соединены с первыми входами 2р групп элементов И (2р - число каналов преобразователи 2), вторые входы элементов И каждой группы являются информационными входами соответствующего канала- преобразователя 2, а выходы соединен с входами элемента ИЛИ, выход которого является соответствующим информационным выходом канала преобразователя 2, тактовый вход распределителя импульсов является тактовым входим преобразователя 2, а выход его последнего разряда - выходом останова преобразователя (выходом конца преобразователя).

Многоканальный преобразователь 2 параллельного кода в последовательность импульсов может быть выполнен также в виде 2р регистров сдвига, соединенных информационными входами с соответствующими информационными входами преобразователя 2, тактовыми входами - с его тактовым входом, а выходами переноса - с информационными выходами соответствующих каналов

5

0

5

0

5

0

5

0 i

преобразователя 2, инверсные выходы каждого регистра сдвига соединены с входами своего элемента И, а выходы последних - с входами элемента И, выход которого является выходом останова (конца преобразования) преобразователя 2, входы разрешения записи регистров сдвига соединены с входами записи преобразователя 2.

Триггер 3 выполняется в виде RS- триггера, если многоканальный преобразователь 2 .выполнен на регистрах сдвига, либо на распределителе импульсов, сигнал на выходе останова (конца преобразования) которого синхронизирован с паузой между тактовыми импульсами, или в виде счетного триггера, а если преобразователь 2 выполнен на распределителе импульсов, сигнал на выходе конца преобразования которого синхронизирован с тактовым импульсом.

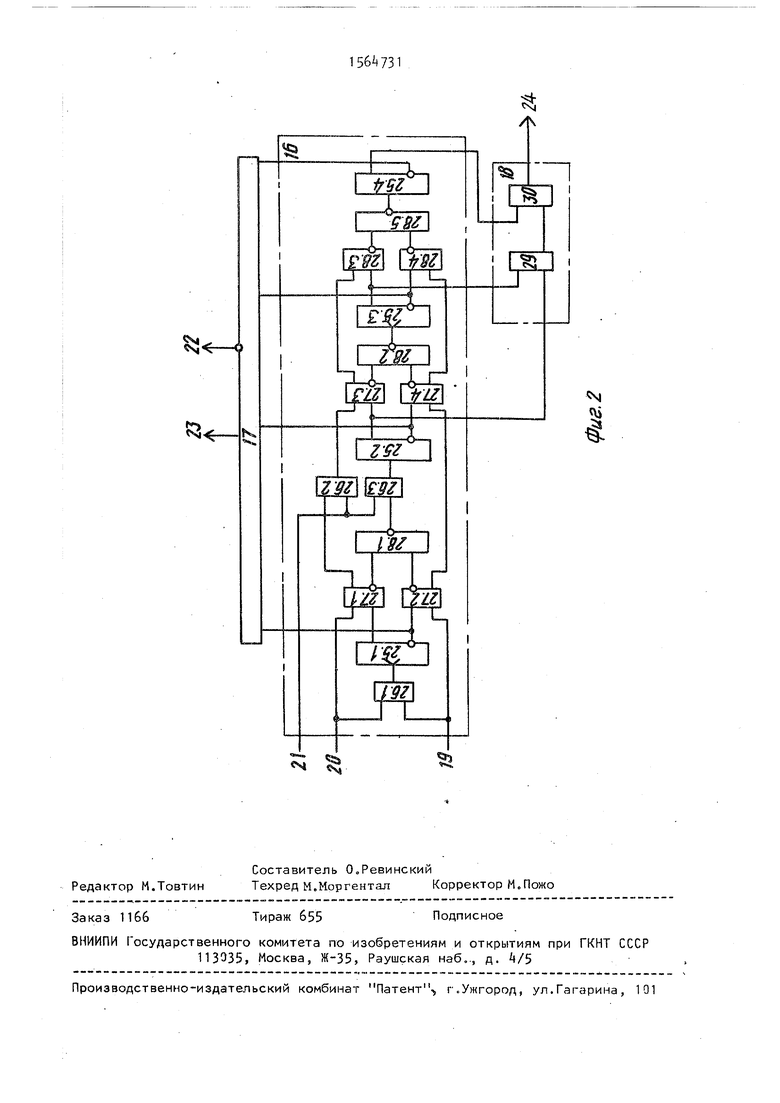

Реверсивный накопитель 7 может быть выполнен (фиг. 2) в виде реверсивного счетчика 16 на (1о§г

(Ш + 1)t 3logi(K + 2)C) РазРяДов. элемента И 17 и блока 18 формирования порога. На фиг. 2 обозначены вычитающий вход 19, первый и второй суммирующие входы 20, 21, являющиеся входами установки в 1м соответственно первого и второго разрядов счетчика 16, и первый - третий выходы 22-24.

Реверсивный счетчик 16 на h разряда может быть выполнен (фиг. 2) на триггерах 25, элементах ИЛИ 26, элементах И 27 и элементах И-НЕ 28. В исходном состоянии в счетчик 16 накопителя 7.1 записывается двоич5

ный код числа q. / 0. Прямые выходы разрядов счетчика 16 с номерами, разными номерам единичных разрядов в двоичном коде числа q;, и инверсные выходы остальных разрядов соединены с входами элемента И 17, инверсный и прямой выходы которого являются соответственно первым и вторым выходами 22, 23 накопителя. Ecryi выбрано число 1 2 - (К + 1). то третьим выходом 2k является прямой выход старшего разряда сметчика 16. Во всех других случаях прямые выходы счетчика 16 соединены с входами блока 18, реализующего порога q. + К + 1, На фиг. 2 показано выполнение этого блока на элементе ИЛИ 29 и элементе И 30 Для случая , , К 11.8 общем случае блок 18 может быть выполнен следующим образом.

Пусть двоичное представление а имеет вид

и

И

ы

Ь 2

ll-Ч

Пусть о(, о .. . d e-i О а 1. Входы блока, начиная с е-го и до g-ro (соответствующие выходы разрядов счетчика 16), такие, что

О

о( е - ol а - I ft

соединены с входами элемента И, выход которого, а также входы блока, начиная с (g + 1)-го и до h-ro, такие, ЧТО o/d + 7 ... о( -h 0.

а t,+1 1, соединены с входами элемента ИЛИ, выход которого,а также входы блока, начиная с (h + 1)-го и до m-го, такие, что о( +1 г ... /„, 1, а 0, О, соединены с входами элемента И, выход которого, а также входы блока, начиная с (т + 1)-го и кончая входом с номером S, такие, что о/т., о( т+ ... 0. a o(s+1 1, соединены с входами элемента ИЛИ, и так далее до объединения всех входов блока 18 Формирования порога (выходов счетчика 16). В частном случае а 2Р блок 18 формирования порога выполняется в виде элемента ИЛИ, соединенного входами с входами блока от (р + 1)-го и до U-ro. В частном

случае

€(. с(г

о/р, 0, а

р р-м:

of ц

1, блок формирования порога выполняется в виде элемента И, соединенного входами с входами блока от р-го и до U-ro. При а блок формирования порога выполняется в виде линии связи с его го входа на выход.

Счетный блок 6 выполняется в виде, аналогичном накопителю 7, с заменой реверсивного счетчика 16 на суммирующий счетчик и исключением инверсного выхода элемента И 17 при этом прямой выход элемента И 17 и выход

блока 18 являются первым и вторым выходами счетного блока 6, в который в исходном состоянии записывается 5 код q 77 0.

В схеме устройства (фиг. 1) можно заменить соединение выхода первого элемента И 9 с прямым входом второго

Ю элемента И 10 на соединение выхода второго элемента ИЛИ 11 с инверсным входом второго элемента И 10.

Устройство функционирует следующим образом.

15 В исходном состоянии многоканальный преобразователь 2 параллельного кода в последовательность импульсов, счетный блок 6, реверсивные накопители 7 и триггер 3 сброшены. При

20 этом на выходе триггера 3 нулевой сигнал, блокирующий прохождение тактовых импульсов через элементы И 8. В накопитель 7-i в исходном состоянии записан код числа q . , а в счет25 ный блок 6 - код числа q . При выполнении многоканального преобразователя 2 на регистрах сдвига, входной код с входных информационных шин 13 записан в эти регистры сдвига.

30 При поступлении тактовых импульсов с выхода генератора 1 тактовых импульсов на тактовый вход многоканального преобразователя 2 последний преобразует количество единичных сигналов, поданных на группу входных информационных шин 13.1 (входы 1-го канала преобразователя 2) в соответствующее количество импульсов на выходе 1-го информационного канала.

Импульсы с 1-го и (р + 1)-го выходов многоканального преобразователя 2 поступают на входы полусумматора k.l. Если импульс поступает на один его вход, это вызывает импульс

45 на его выходе суммы, соединенном с первым счетным входом реверсивного накопителя 7.1 (при 1 р), и через элемент ИЛИ 5 с первым суммирующим входом счетного блока 6 (при 1 р).

50 к содержимому которых при этом прибавляется единица. Если импульсы поступают на оба входа полусумматора

35

40

5

7156

Если за время работы многоканального преобразователя 2 на входы поступит не менее К+1 импульсов, то на втором выходе счетного блока 6 форми- руется единичный сигнал, поступающий через элемент ИЛИ 12 на выход 15 окончания работы устройства, свидетельствуя об окончании цикла работы устройства, с первого выхода счетного блока 6 на выход элемента И 10, являющийся информационным выходом 14 устройства, снимается нулевой сигнал. Если за время работы многоканального преобразователя 2 в счетном бло- ке 6 не будет накоплено более К импульсов, то работа продолжается а описанном выше порядке до опроса всех входных информационных шин, для чего потребуется п/2рС тактов. При этом по окончании работы многоканального преобразователя 2 он самоблокируется и далее импульсов на информационных выходах каналов не формирует. При этом на его выходе конца преобразова- ния появляется единичный импульс, переключающий триггер 3 (в паузу между тактовыми импульсами), на выходе которого появляется единичный сигнал, разрешающий прохождение тактовых им- пульсов через элемент И 8,

Дал-ее происходит процесс последовательного пересчета содержимого реверсивных накопителей 7 в счетный блок 6. Пусть 7.Ј наименьший номер накопителя, в который записан код, отличный от qr, т.е. за время работы многоканального преобразователя 2 на его суммирующие входы поступили пульсы. При этом на первом выходе реверсивного накопителя }. т - единичный сигнал, а на втором, соединенном с входами элементов 8.(г+ 1) - - 8.(р - 1) И - нулевой, запрещающий прохождение тактовых импульсов на их выходы.

Таким образом, на всех входах элемента 8.г И единичные сигналы и тактовые импульсы проходят через него на вычитающий вход реверсивного на- копителя 7 г, от содержимого которого при этом каждый раз вычитается единица, и через элемент ИЛИ 5 на первый суммирующий вход счетного блока 6, к содержимому которого при этом прибавляется единица. Работа продолжается таким образом до возвра щения реверсивного накопителя 7. г в исходное состояние. При этом на ег

первом выходе появляется нулевой сигнал, запрещающий прохождение тактовых импульсов на выход элемента 8.г И, а на втором выходе - единичный сигнал, разрешающий прохождение тактовых импульсов на выходы элементов 8.(г+ 1) И - 8.(ю - 1). Далее аналогичным образом осуществляется пересчет содержимого накопителей 7.(г+ 1) - 7. (р 1) в счетный блок 6.

Если

ги

момент времени в счетчике счетного блока 6 окажется записан код числа q + К + 1, где q - код числа начального состояния счетчика блока 6. При этом на втором выходе счетного блока 6 появится единичный сигнал, поступающий через элемент ИЛИ 12 на выход 15 окончания работы устройства, свидетельствуя об окончании цикла работы, а с первого выхода счетного блока 6 поступает нулевой сигнал (результат контроля) на элемент И 10, вызывая нулевой сигнал на выходе 1 устройства.

1

Если X х Ј К, то по окончании

пересчета содержимого всех реверсивных накопителей 7 в счетный блок 6 на их вторых выходах оказываются единичные сигналы, свидетельствующие об их возвращении в исходное состояние, что вызывает единичный сигнал на выходе элемента И 9, поступающий через элемент ИЛИ 12 на выход 15 v окончания контроля устройства, свидетельствуя об окончании цикла работы. При этом с первого выхода счетного

блока 6 на элемент И 10 поступает

iп

нулевой сигнал, если .х.К, и

«- п единичный сигнал, если %. - К.

При .поступлении на входы некоторого полусумматора k„ К + 1 или К + + 2 импульсов, в счетчике реверсивного накопителя 7Л оказывается записан код соответствующего числа, что вызывает единичный сигнал на его третьем выходе, поступающий через элементы ИЛИ 11 и 12 на выход 15 окончания работы устройства, свидетельствуя об окончании цикла работы. При этом с выхода элемента И 10 на информационный выход 14 устройства поступает нулевой сигнал, поскольку

на его входе, соединенном с выходом элемента И 9 - нулевой сигнал.

Таким образом, на выходе К устройства формируется выходной единичный сигнал, только если во входном коде ровно К единичных сигналов.

Устройство для обнаружения ошибок в реверсивном коде К из п обеспечивает повышение быстродействия до 30% по сравнению с прототипом.

Формула изобретения

Устройство для обнаружения ошибок в равновесном коде К из п, содержащее многоканальный преобразователь параллельного кода в последовательности импульсов, 2р групп (р 2, 3, ...) информационных входов которого являются соответствующими входами устройства, генератор тактовых импульсов, выход которого подключен к первым входам первого - (р - 1)-го элементов И группы и тактовому входу многоканального преобразователя параллельного кода в последовательности импульсов, выход окончания преобразования которого соединен с входом триггера, выход которого подключен к первому входу первого элемента И и вторым входам первого - (р - 1)-го элементов И группы, выходы которых соединены с вычитающими входами одноименных реверсивных накопителей и соответствующими входами первого элемента ИЛИ, выход которого подключен к первому входу счетного блока, первый выход которого соединен с первым входом второго элемен

5

0

5

0

5

0

та И, первой выход 1-го реверсивного накопителя (i 1,р -Г) соединен с (i + 2)-м входом 1-го элемента И группы, второй выход 1-го реверсивного накопителя подключен к (i + + 1)-му входу первого элемента И и (i + 2)-му входу (i + 1)-го - (p-l)-rc элементов И группы, выход первого элемента И подключен к-второму входу второго элемента И, выход которого является информационным выходом устройства, третьи выходы всех реверсивных накопителей подключены к соответствующим входам второго элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия, в устройство введены третий элемент ИЛИ и первый - р-й полусумматоры, j-й и (р + J)-и информационные выходы (j 1,р) многоканального преобразователя параллельного кода в последовательности импульсов соединены соответственно с первым и вторым входами j-ro полусумматора, выходы суммы и пгреноса 1-го полусумматора (i 1,р - 1) подключены соответственно к первому и второму суммирующим входам 1-го реверсивного накопителя, выходы суммы и переноса р-го полусумматора соединены соответственно с р-м входом первого элемента ИЛИ и вторым входом счетного блока, второй выход которого и выход второго элемента ИЛИ подключены к первому и второму входам третьего элемента ИЛИ, третий вход которого подключен к выходу первого элемента И, выход третьего элемента ИЛИ является выходом окончания работы устройства.

Редактор М.Товтин

Составитель (КРевинский

Техред М.МоргенталКорректор М.Пожо

Заказ 1166

Тираж 655

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. V5

Производственно-издательский комбинат Патент - г.Ужгород, ул.Гагарина, 191

ч«

I

Подписное

Авторы

Даты

1990-05-15—Публикация

1987-12-08—Подача