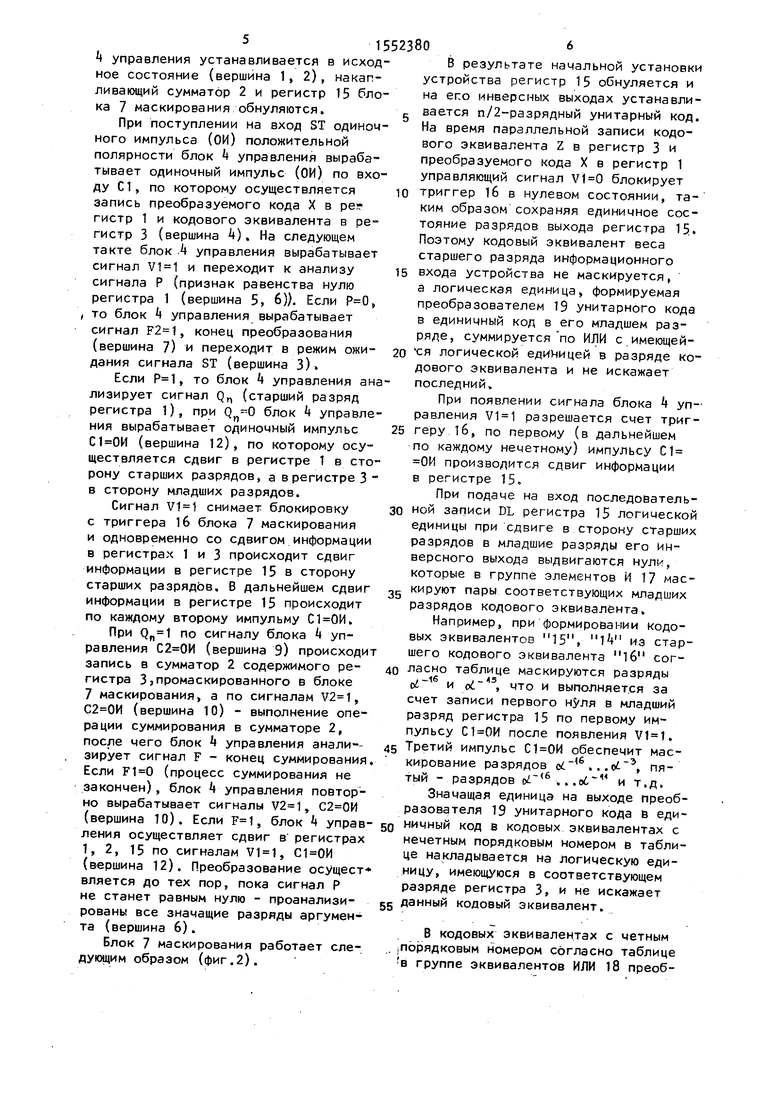

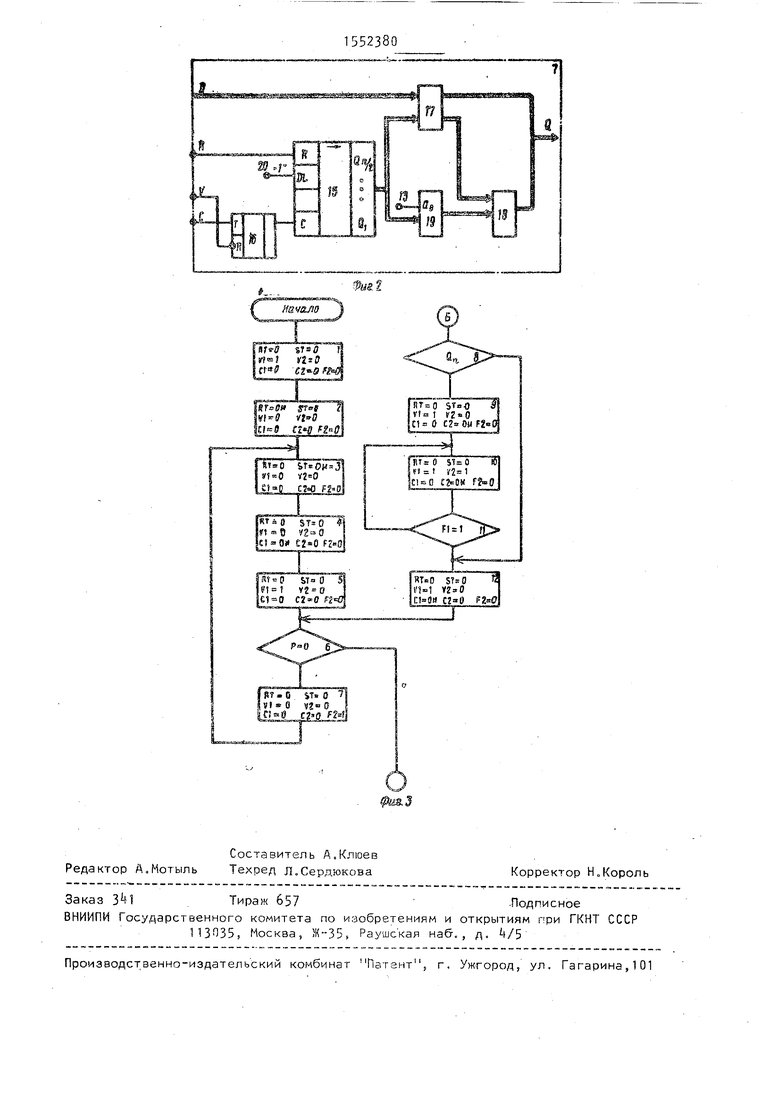

жит сдвигающий регистр 15, триггер 16, группу элементов И 17, группу элементов ИЛИ 18, преобразователь 19 унитарного кода в единичный код, вход 20 единичного потенциала преобразователя .

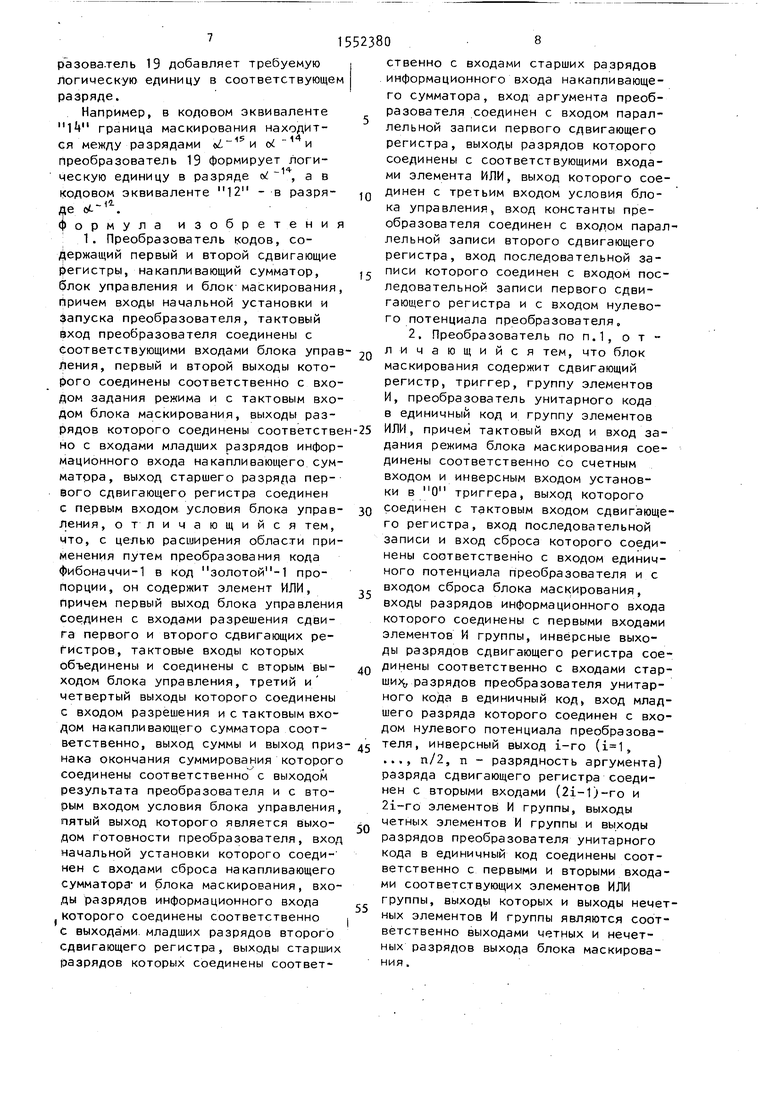

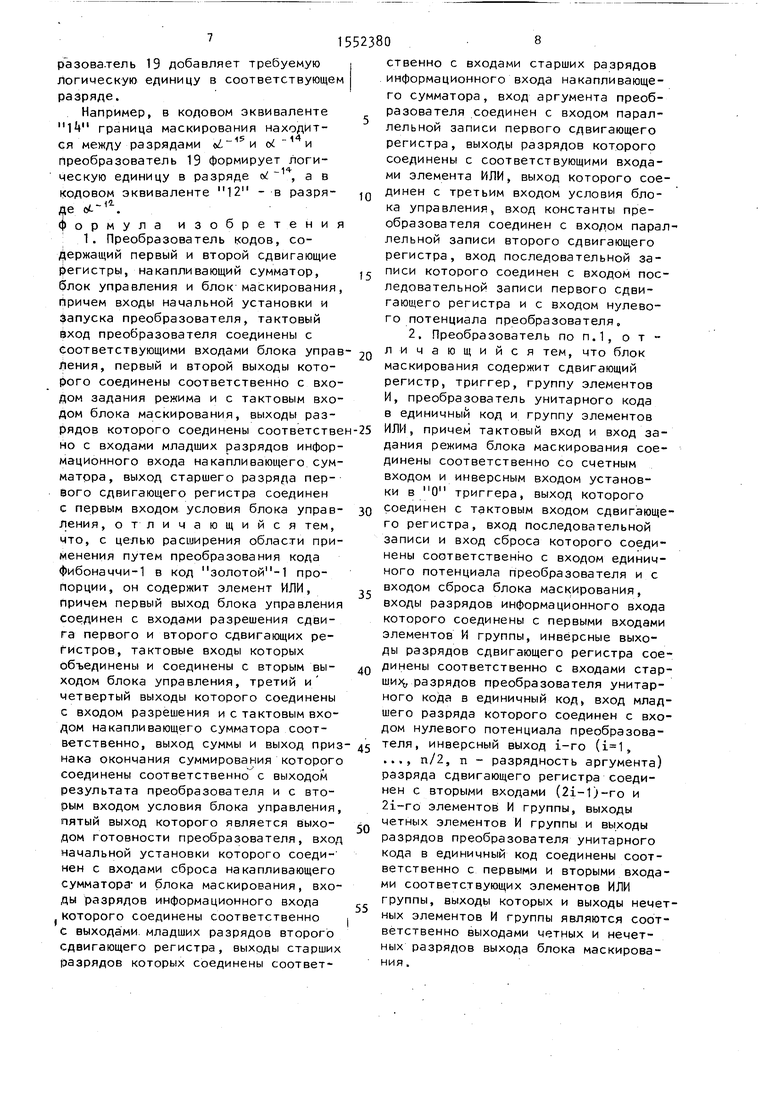

В диаграмме алгоритма (фиг.З) использованы следующие обозначения: КГ, ST, FT - соответственно входы начальной установки, запуска и тактового блока k управления; V1, С1, V2, С2, F2 - соответственно с первого по пятый выходы блока управления; Оп, П, Р - соответственно с первого по третий входы условия блока 4 управления.

I

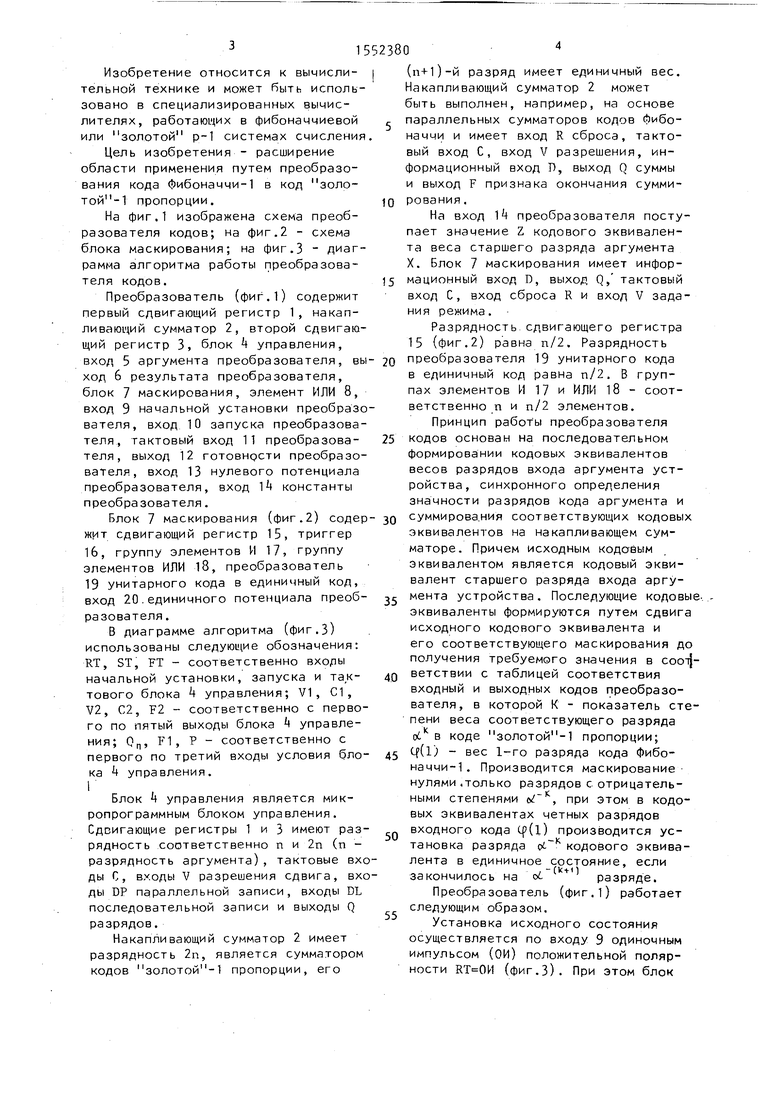

Блок управления является микропрограммным блоком управления. Сдвигающие регистры 1 и 3 имеют разрядность соответственно п и 2п (п - разрядность аргумента), тактовые входы С, V разрешения сдвига, входы DP параллельной записи, входы DL последовательной записи и выходы Q разрядов.

Накапливающий сумматор 2 имеет разрядность 2п, является сумматором кодов золотой - пропорции, его

5

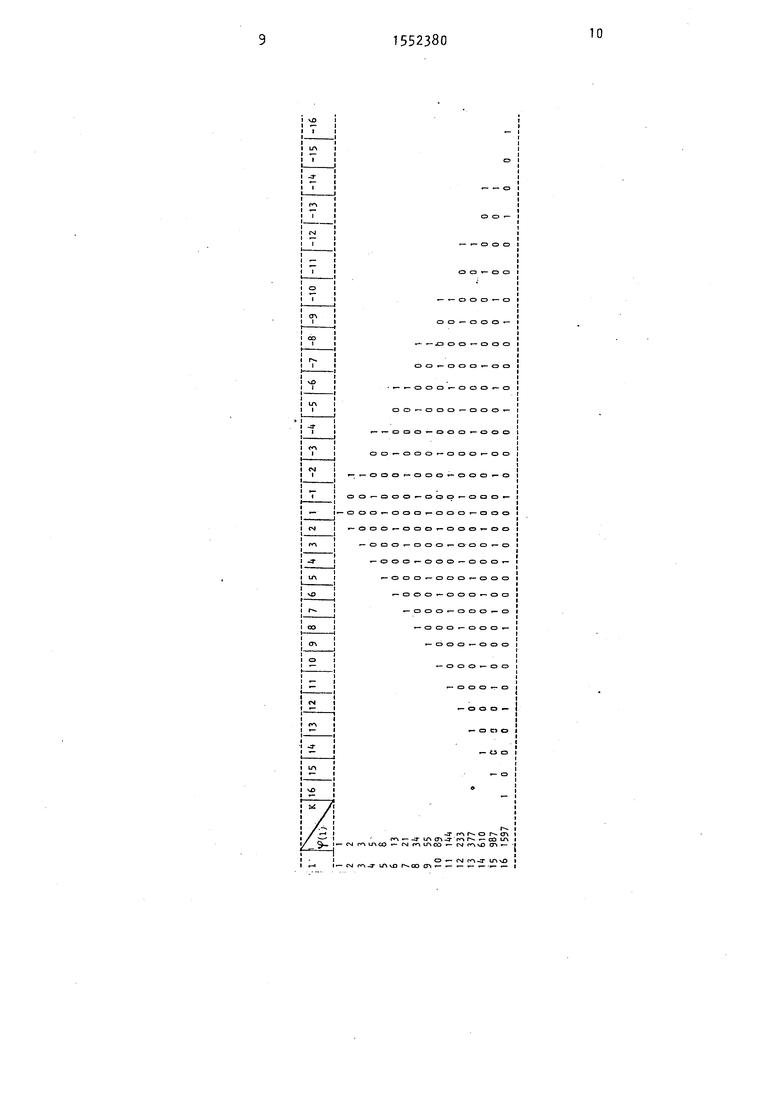

эквивалентов на накапливающем сумматоре. Причем исходным кодовым эквивалентом является кодовый эквивалент старшего разряда входа аргумента устройства. Последующие кодовые эквиваленты формируются путем сдвига исходного кодового эквивалента и его соответствующего маскирования до получения требуемого значения в cooij- ветствии с таблицей соответствия входный и выходных кодов преобразователя, в которой К - показатель степени веса соответствующего разряда oi в коде золотой - пропорции; 5 ц(1) - вес 1-го разряда кода фибо- наччи-1. Производится маскирование нулями .только разрядов с отрицательными степенями &Г, при этом в кодо0

вых эквивалентах четных разрядов входного кода Ц(1) производится установка разряда ot кодового эквивалента в единичное состояние, если

. - (V-K)

закончилось на х разряде.

Преобразователь (фиг.1) работает следующим образом.

Установка исходного состояния осуществляется по входу 9 одиночным импульсом (ОН) положительной полярности (фиг.З). При этом блок

51552380

k управления устанавливается в исходное состояние (вершина 1, 2), накапливающий сумматор 2 и регистр 15 блока 7 маскирования обнуляются.

При поступлении на вход ST одиночного импульса (ОИ) положительной полярности блок А управления вырабатывает одиночный импульс (ОИ) по входу С1, по которому осуществляется запись преобразуемого кода X в регистр 1 и кодового эквивалента в регистр 3 (вершина ), На следующем такте блок 4 управления вырабатывает сигнал и переходит к анализу сигнала Р (признак равенства нулю регистра 1 (вершина 5, 6)). Если , то блок 4 управления вырабатывает сигнал , конец преобразования

10

В результате начальной установки устройства регистр 15 обнуляется и на его инверсных выходах устанавливается n/2-разрядный унитарный код. На время параллельной записи кодового эквивалента Z в регистр 3 и преобразуемого кода X в регистр 1 управляющий сигнал блокирует триггер 16 в нулевом состоянии, таким образом сохраняя единичное состояние разрядов выхода регистра 15. Поэтому кодовый эквивалент веса старшего разряда информационного 15 входа устройства не маскируется, а логическая единица, формируемая преобразователем 19 унитарного кода в единичный код в его младшем разряде, суммируется по ИЛИ с имеющей(вершина 7) и переходит в режим ожи- 20 ся логической единицей в разряде кодания сигнала ST (вершина 3).

Если , то блок А управления анализирует сигнал Qn (старший разряд

дового эквивалента и не искажает последний.

При появлении сигнала блока Ц управления разрешается счет тригния вырабатывает одиночный импульс 25 геру 16, по первому (в дальнейшем (вершина 12), по которому осу- по каждому нечетному) импульсу С1

регистра 1), при блок управлеществляется сдвиг в регистре 1 в сторону старших разрядов, а в регистре 3 в сторону младших разрядов.

Сигнал снимает блокировку с триггера 16 блока 7 маскирования и одновременно со сдвигом информации в регистрах 1 и 3 происходит сдвиг информации в регистре 15 в сторону старших разрядив. В дальнейшем сдвиг информации в регистре 15 происходит по каждому второму импульму .

При по сигналу блока 4 управления (вершина 9) происходит запись в сумматор 2 содержимого регистра 3,промаскированного в блоке 7 маскирования, а по сигналам , (вершина 10) - выполнение операции суммирования в сумматоре 2, после чего блок 4 управления анализирует сигнал F - конец суммирования. Если (процесс суммирования не закончен), блок Ь управления повторно вырабатывает сигналы ,

ОИ производится сдвиг информации в регистре 15.

При подаме на вход последователь30 записи DL регистра 15 логической единицы при сдвиге в сторону старших разрядов в младшие разояды его инверсного выхода выдвигаются нули, которые в группе элементов И 17 мас35 кируют пары соответствующих младших разрядов кодового эквивалента.

Например, при формировании кодовых эквивалентов 15

1V

из старшего кодового эквивалента 16 сог- 40 ласно таблице маскируются разряды U и , что и выполняется за счет записи первого нуля в младший разряд регистра 15 по первому импульсу после появления . 45 Третий импульс обеспечит маскирование разрядов .. . , пятый - разрядов ex. 6 .. . и т.д. Значащая единица на выходе преобразователя 19 унитарного кода в еди(вершина 10). Если , блок 4 управ- 50 ничный код в кодовых эквивалентах с ления осуществляет сдвиг в регистрах нечетным порядковым номером в таблице накладывается на логическую единицу, имеющуюся в соответствующем разряде регистра 3, и не искажает 55 данный кодовый эквивалент.

1, 2, 15 по сигналам , (вершина 12). Преобразование осущест вляется до тех пор, пока сигнал Р не станет равным нулю - проанализированы все значащие разряды аргумента (вершина 6).

Блок 7 маскирования работает следующим образом (фиг.2).

В кодовых эквивалентах с четным ,порядковым номером согласно таблице в группе эквивалентов ИЛИ 18 преоб

В результате начальной установки устройства регистр 15 обнуляется и на его инверсных выходах устанавливается n/2-разрядный унитарный код. На время параллельной записи кодового эквивалента Z в регистр 3 и преобразуемого кода X в регистр 1 управляющий сигнал блокирует триггер 16 в нулевом состоянии, таким образом сохраняя единичное состояние разрядов выхода регистра 15. Поэтому кодовый эквивалент веса старшего разряда информационного 5 входа устройства не маскируется, а логическая единица, формируемая преобразователем 19 унитарного кода в единичный код в его младшем разряде, суммируется по ИЛИ с имеющей ОИ производится сдвиг информации в регистре 15.

При подаме на вход последовательн й записи DL регистра 15 логической единицы при сдвиге в сторону старших разрядов в младшие разояды его инверсного выхода выдвигаются нули, которые в группе элементов И 17 маскируют пары соответствующих младших разрядов кодового эквивалента.

Например, при формировании кодовых эквивалентов 15

1V

из старшего кодового эквивалента 16 сог- ласно таблице маскируются разряды U и , что и выполняется за счет записи первого нуля в младший разряд регистра 15 по первому импульсу после появления . Третий импульс обеспечит маскирование разрядов .. . , пятый - разрядов ex. 6 .. . и т.д. Значащая единица на выходе преобВ кодовых эквивалентах с четным ,порядковым номером согласно таблице в группе эквивалентов ИЛИ 18 преоб

разова.тель 19 добавляет требуемую логическую единицу в соответствующем разряде.

Например, в кодовом эквиваленте IV граница маскирования находит.с 4 4

ся между разрядами ei и о(. и преобразователь 19 формирует логическую единицу в разряде , а в кодовом эквиваленте 12 - в разряде - . Формула изобретения

1. Преобразователь кодов, содержащий первый и второй сдвигающие регистры, накапливающий сумматор, блок управления и блок маскирования, причем входы начальной установки и запуска преобразователя, тактовый вход преобразователя соединены с соответствующими входами блока управ ления, первый и второй выходы которого соединены соответственно с входом задания режима и с тактовым входом блока маскирования, выходы разрядов которого соединены соответстве но с входами младших разрядов информационного входа накапливающего сумматора, выход старшего разряда первого сдвигающего регистра соединен с первым входом условия блока управления, отличающийся тем, что, с целью расширения области применения путем преобразования кода фибоначчи-1 в код золотой -1 пропорции, он содержит элемент ИЛИ, причем первый выход блока управления соединен с входами разрешения сдвига первого и второго сдвигающих регистров, тактовые входы которых объединены и соединены с вторым выходом блока управления, третий и четвертый выходы которого соединены с входом разрешения и с тактовым входом накапливающего сумматора соответственно, выход суммы и выход приз нака окончания суммирования которого соединены соответственно с выходом результата преобразователя и с вторым входом условия блока управления, пятый выход которого является выходом готовности преобразователя, вход начальной установки которого соединен с входами сброса накапливающего сумматора1 и блока маскирования, входы разрядов информационного входа которого соединены соответственно с выходами младших разрядов второго сдвигающего регистра, выходы старших разрядов которых соединены соответ

0

5

0 25 45

30

35

40

50

55

ственно с входами старших разрядов информационного входа накапливающего сумматора, вход аргумента преобразователя соединен с входом параллельной записи первого сдвигающего регистра, выходы разрядов которого соединены с соответствующими входами элемента ИЛИ, выход которого соединен с третьим входом условия блока управления, вход константы преобразователя соединен с входом параллельной записи второго сдвигающего регистра, вход последовательной записи которого соединен с входом последовательной записи первого сдвигающего регистра и с входом нулевого потенциала преобразователя.

2. Преобразователь по п.1, о т - личающийся тем, что блок маскирования содержит сдвигающий регистр, триггер, группу элементов И, преобразователь унитарного кода в единичный код и группу элементов ИЛИ, причем тактовый вход и вход задания режима блока маскирования соединены соответственно со счетным входом и инверсным входом установки в О триггера, выход которого соединен с тактовым входом сдвигающего регистра, вход последовательной записи и вход сброса которого соединены соответственно с входом единичного потенциала преобразователя и с входом сброса блока маскирования, входы разрядов информационного входа которого соединены с первыми входами элементов И группы, инверсные выходы разрядов сдвигающего регистра соединены соответственно с входами стар- ших разрядов преобразователя унитарного кода в единичный код, вход младшего разряда которого соединен с входом нулевого потенциала преобразователя, инверсный выход 1-го (, ..., n/2, n - разрядность аргумента) разряда сдвигающего регистра соединен с вторыми входами (21-1;-го и 21-го элементов И группы, выходы четных элементов И группы и выходы разрядов преобразователя унитарного кода в единичный код соединены соответственно с первыми и вторыми входами соответствующих элементов ИЛИ группы, выходы которых и выходы нечетных элементов И группы являются соответственно выходами четных и нечетных разрядов выхода блока маскирования .

- VЈ О4 Ю - CO ЧЛ Isj - ОО 1Л jJ ГО - Л OD - -J VA -С-ЧО Л ч(Г--OJ VD J О -J i

| название | год | авторы | номер документа |

|---|---|---|---|

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1984 |

|

SU1266008A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| "Преобразователь кода Фибоначчи-1 в код "золотой"-1 пропорции" | 1988 |

|

SU1649671A1 |

| Преобразователь кодов | 1987 |

|

SU1450112A1 |

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1977 |

|

SU744546A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1982 |

|

SU1048469A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

Изобретение относится к вычислительной технике и позволяет расширить область применения преобразователя кодов путем преобразования кода Фибоначчи-1 в код "золотой"-1 пропорции. Преобразователь кодов содержит сдвигающие регистры 1 и 3, накапливающий сумматор 2, блок 4 управления, блок 7 маскирования и элемент ИЛИ 8 с соответствующими связями. Кодовые эквиваленты формируются согласно таблице кодовых эквивалентов путем сдвига старшего кодового эквивалента в сторону младших разрядов и маскирования при этом соответствующих разрядов. 1 з.п. ф-лы, 3 ил., 1 табл.

о о о -

-о о о -

0-000 -

о о - о о о -

000-«000 -

-«ООСЭ--ООСЭ-

О-«OOCD- СЭОСЭ-

00--ООО- ОСЭО-000-000- О О О -

-«ооо- ооо-«ооо-

О-( О О - О О О ооо- сэоо-«о о- сзо

-ооо- ооо- ооо- о

о--ооо- ооо- ооо -

ОО-«ООО- ООО- ОО

ооо- ооо- ооо - -

-О О О - ООО- О О О-ООО--ООО- - ОСЭ- ОСЭО- ОО 000- ООСУ- -- О О О - О О О - О О О - -

О О - О О

ооо--01

ogЈsssi

| Преобразователь кодов | 1976 |

|

SU662933A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-23—Публикация

1988-07-11—Подача