(54) ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Устройство для решения интегральных уравнений Фредгольма второго порядка | 1985 |

|

SU1295413A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

| Устройство для суммирования одноразрядных приращений | 1985 |

|

SU1251072A1 |

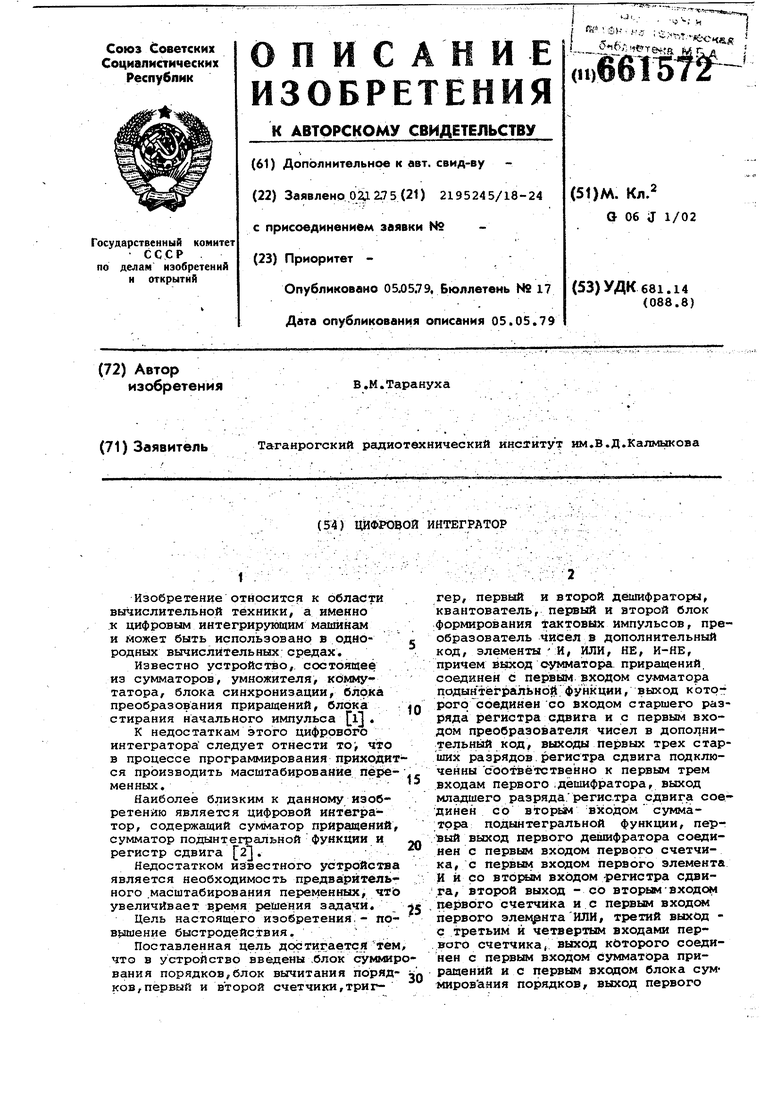

. , Г : - : Изобретение относится к области вычислительной техники, а именно к цифровым интегрирующим машинам и может быть использовано в однородных вычислительных средах. Известно устройство, состоящее из сумматоров, умножителя, комму татора, блока синхронизации, блока преобразования приращений, блока стирания начального импульса l . К недостаткам этого цифрового интегратора следует отнести то; что в процессе программирования приходи ся производить масштабирование пере менных. Наиболее близким к данному изобретению является цифровой интегратор, содержащий сумматор приращений сумматор подынтегральной -функции и регистр сдвига 2. Недостатком известного устройотв является необходимость предваритель ного .масштабирования переменных, чт увеличивает время решения задачи. Цель настоящего изобретения - по в лшение быстродействия. Поставленная цель дрбтигается те что в устройство введены .блок сумми вания порядков,блок вычитания поряд ков,первый и второй счетчики,триг., .:.., . :. -V 2 ; . гер, первый и второй дешифраторы, квантователь, первый и второй блок формирования тактовых импульсов, преобразователь чисел в дополнительный код, элементы И, ИЛИ, НЕ, И-НЕ, причем выход сумматора приращений соединен с первым входом сумматора подынтёграяьнойфункции, выход которогосоединен со входом старшего разряда регистра сдвига и с первым входом преобразователя чисел в дoпo нительный код, выходы первых трех старших разрядов регистра сдвига подключенны Соответственно к первым трем входам первого дешифратора, выход младшего разрядарегистра сдвига соединен со BTOpbW входом сумматора подынтегральной функции, первый выход первого дешифратора соединен с первым входом первого счетчика, с первым входом первого элемента И И со зторам входом -регистра сдвига, второй выход - со вторым-входом первого счетчИка и с первым входсж первого элементаИЛИ, третий выход с третьим и четвертым входами первого счетчика, выход которого соединен с первым входом сумматора приращенИй и с первым входом блока суммирования порядков, выэсод первого

элемента ИЛИ соединен с третьим входом регистра сдвига и со вторым входом первого элемента И, выход которого подключен к четвертому входу регистра сдвига, выход блока суммирования порядков соединен с первым входом блока вычитания порядков, первый и второй выходы которого подключены соответственно к первому и второму вхС1дам второго счетчика, третий выход блока вычитания порядков соединен с первым входом второго де- 10 шифратора, выход которого соединен с первым входом квантователя, четвертый выход.блока вычитания порядков соединен с первым входом перво-. го блока формирования тактовых им- 15 пульсов, выход которого соединен со входом элемента НЕ, с первыми входами второго и третьего элементов И и со вторым входом квантователя, выход элемента НЕ соединен с первыми входа-gg ми четвертого и пятого элемента И, выход второго блока формирования тактовых импульсов соединен с третьим и четвертым входами второго счетчика, выход которого соединен с первым и вторым входами триггера, первый выход триггера соединен со вторыми входами второго и пятого элементов И, второй выход триггера соединен с первым входом второго блока формирования тактовых импульсов, пятый выход 30 блокавычитания порядков соединен с третьим входом квантователя, первый выход которого соединен со вторым входом блока вычитания порядков, выход элемента И-ЯЕ соединен с тре- 35 тьими входами второго и пятого элементов И, со вторыми входами третьего и четвертого элементов И и с четвёртым входом квантЬватёл:я, пятьой вход которого соединен с выхо- 40 дом преобразователя чисел в дополнительный код, выходы второго и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, вь1- g ход кОто)6го соединен со вторым входом сумматора приращений и со вторым входом первого элемента ИЛИ, В1 1з{Оды Третьего и пятого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, которОРО ТтОдкййчён k шестому входу квантователя, N входов сумматора приращений, второй вход блока суммирования порядков, первый вход элемента И-НЕ и второй 55 входпреобразователя чисел в дополнительный код являются информационными входами устройства, второй йЬ1хОД квантователя является информационным выходом устройства, тре- ед тий вход сумматора приращений, третий и Четвертый входы преобразов&Тё ля 1Исел в дополнительный код; второй и третий входы элемента И-НЕ, TpeTSW входы третьего и четвертого

элементов И, четвертые входы третьего и пятого элементов И, седьмой восьмой и девятый входы квантователя, третий вход триггера, второй вход первого, второй и третий входы второго блоков вьделения тактовых импульсОв, третий входблОк суммирования порядков, третий и четвертый входы блока вычитания порядко являются управляющими входами устройства.

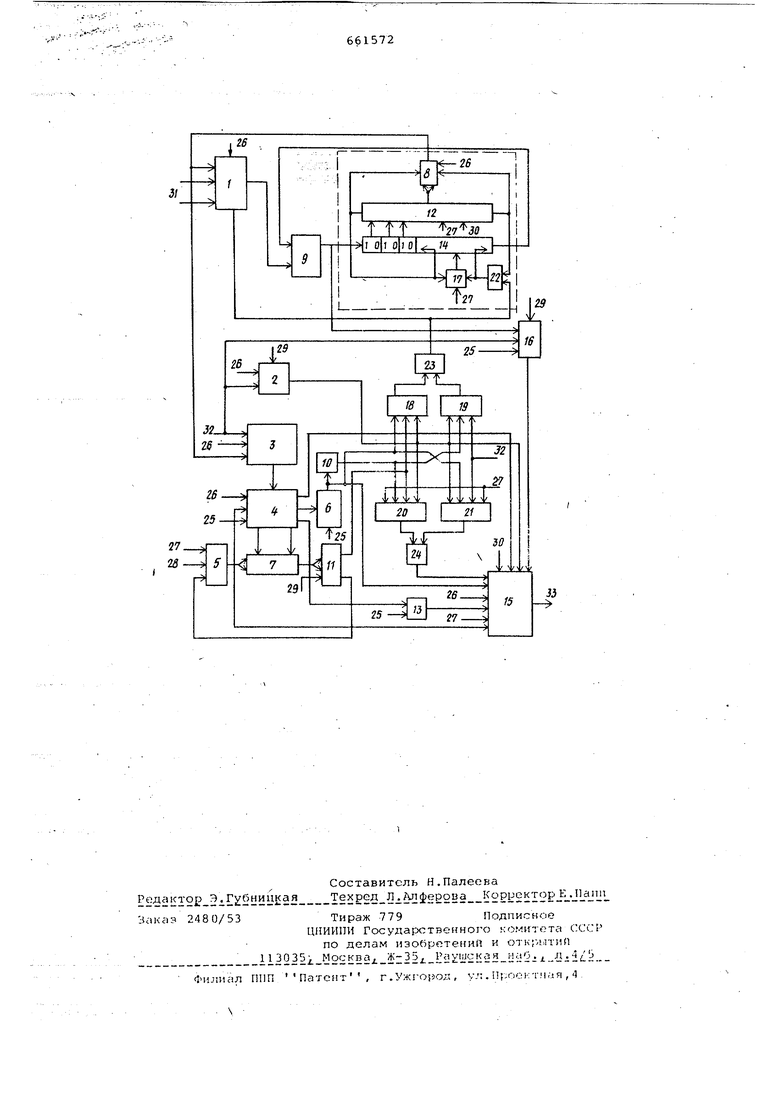

На чертеже приведена блок-схема цифрового интегратора. Цифровой интегратор содержит сумматор 1 приращений, элемент И-НЕ 2, блок 3 суммирования порядков, блок 4 вычитания порядков, блоки 5, 6 выделения тактовых импульсов, счетчики 7, 8, сумматор 9 подынтегральной функции, эле мент НЕ 10, триггер,11, дешифраторы 12, 13, регистр 14 сдвига, квантователь 15, преобразователь 16 чисел в дополнительный код, элементы И 17, 18, 19, 20, 21, элементы ИЛИ 22, 23, 24, управляющие входы 5, 26, 27, 28 29, 30, информационные входы 31, 32, информационный выход 33 устройства.

Устройство работает следующим образом.

На управляющий вход 26 сумматора 1, на входы элемента И-НЕ 2, блоков 3, 4, квантователя 15, счетчика 8 поступает из устройства управления сигнал выделения кода приращения. На информационные входы 31 поступают коды приращений с выходов цифровых интеграторов, на вход 32 поступает код приращений переменной интегри7 рования. При этом начинается подготО витальный этап.операции интегриро- вания. Счетчик 8 и квантователь 15 переходят из режима хранения в режим ввдачи порядков. В сумматоре 1 вычитается разность порядков

;Н

) В блоках 3 и

1(К(-1)

4 вычисляется сумма порядков ук(-11 (-i+i) и разность поряд«° (ili-i)(UiV ) соответственно,,

где: .jj.j. - порядок подынтегральной функции в к-том интеграторе на(1-1)-м шаге интегрирования.

- порядок подынтегральП

ной функции на i -м шаге интегрирования.

пН п ..,;.1)- порядок йодыятеграль ной ФУНКЦИИ на (i+l)-M

шаге интегрирования. Поек порядок остатка приращения к-го интегратора на i -м шаге.

В элементе 2 анализируются единичные и нулевые разряды порядка приращения ) до знакового разряда. При наличии в порядке единиц и нулей.элементом 2 вырабатывается си нал разрешения, который поступает на входы элементов И 18, 19, 20, 21 и квантователя 15 и длится до окончания интегрирования, а при наличии только единиц вырабатывается сигнал запрета. По знаковому разряду входного приращения из устройства управления подается сигнал выделения знакового разряда приращения на вход 25 блока 6, дешифратора 13, блока 4, преобразователя 16. По этому сигналу перезаписывается из блок 4 в Счетчик 7 вычисленная разность порядков. В блоке 6 анализируется знак разности порядков и в зависимости от него вырабатываются сигналы для управления элементами И 18, 19, 20, 21. Дешифратором 13 вырабатывается сигнал для управления квантователем 15, если модуль разности порядков Н . . гг Н (Пук (i-i) (i-i-1) вен нулю. Кроме того, если знаковый разряд входного приращения переменной интегрирования отрицательный, вкл(очается преобразователь 16, если положительный, преобразователь кода не используется. Одновременно по знаковому разряду входного приращения сни мается сигнал на выделение кода приращения и из устройства подается потенциал работы по входу 28 на блок 5, при этом начинается операция интегрирования, и когда знак разности порядков (nyK(i-i) +П7Х K(i + i)-По5к1 положительный, блоком 6 выдается сигнал, который подготавливает элемент И18 и открывает элемент 21, ра нее подготовленный потенциалом выделения остатка по входу 32 (потенциал выделения остатка поступает из устройства управления в начале операции интегрирования и длится до выделения знакового разряда выходного приращения) . Через элемент И 21 тактовые импульсы поступают на вход квантователя 15, в котором осуществляется продвижение младшими разрядами вперед мантиссы остатка и суммирование ее с нулевыми раэрядами до поступления мантиссы приращения. Одновремен но по потенциалу работы открывается блок 5, подготовленный сигнал с нулевого выхода триггера 11 поступает на блок 5.Через открытый блок 5 тактовые импульсы поступают со -входа 27 на счетный вхоД счетчика 7. В счетчике вычитаются тактовые импульсы до записи в нем нулевого кода. В момент записи в счетчике 7 нулевого кода с выхода послед него выдается сигнал, по которому переключается триггер 11 в единичное состояние. Потенциал с единичного выхода триггера 11 подается на элементы И 18, 19, т.к. элемент 19 , а элемент 18 открыт сигналом поступающим с выхода блока 6, то по потенциалу, поступающему с единичного выхода триггера 11, элементом И 18, вьщается сигнал, обеспечивающий сдвиг вправо кода мантиссы подынтегральной функции в регистре 14 и одновременно разрешающий суммирование входных приращений в сумматоре 1. Сдвиг мантиссы подынтегральной функции в регистре 14 осуществляется следующим образом. По сигналу, поступающему из выхода элемента И 18 настраивается регистр 14 на сдвиг информации вправо и одновременно открывается элемент И 17, через который тактовые импульсы поступают на синхронизирующий вход регистра 14, который переходит из режима хранения в режим Ъыдачи мантиссы подынтегральной функции. Мантисса с выхода регистра 14 и суммарныйпоток приращений, приведённый к младшему разряду подынтегральной функции из выхода сумматора 1 поступает на входы сумматора 9, в котором вычисляется новое значение мантиссы подынтегральной функции М у ц { Мук(-1) t-Z i S ду к Вычисленная мантисса перезаписывается в регистре 14 и одновременно поступает через преобразователь 16 на информационный вход квантователя 15 с задержкой на 2.aK(l-i) -. относительно мантиссы остатка преобразователе 16 произведению присваивается знак приращения переменной интегрирования. В квантователе 15 мантисса приращения суммируется с мантиссой остатка. В случае, когда знак разности порядков отрицательный, блок 6 совместно с элементом НЕ 10 вырабатывает сигнал, по которому подготавливается элемент И 19 и открывается элемент И 20, подготовленный потенциалом выделения остатка по входу 27, Далее вычисления проводятся как и в случае положительного знака разности порядков до записи в счетчике 7 нулевого кода. В этот момент триггер 11 переключается в единичное состояние сигналом, поступающим с выхода счетчика 7. Потенциал с единичного выхода этого триггера открывает элемент И 19, через него тактовые импульсы поступают на вход квантователя 15, который переходит из режима хранения в режим продвижения мантиссы остатка. Мантисса остатка при этом задерживается на )(Uir-Пosк тактов относительно мантиссы подынтеральной функции. В квантователе 15 осуществляетя суммирование мантисс остатка и ычисленного приращения. По окончанию процесса суммирования снимаетя потенциал выделения остатка (по

входу 32). OflHOBpeMejiHO из устройства управления поступает потенциал

нормализации на вход 30 дешифратора 12 и квантователя 15. Нормализация мантиссы подынтегральной фунКцйй осуществляется следукадим образом. В дешифраторе 12 анализируются два знаковых и о)дин старший разряд мантиссы. Если знаковые разряды не совпадают, то дешифратором 12 вырабатывается сигнал на нормализацию вправо. Этот сигнал одновре Шнн6 поступает науправлявдие входы счетчика 8, регистра 14, элемента И 17. При.этом настраивается счётчик 8 на суммирование импульсов, а Jpeгиcтp 14 - на сдвиг кодамантиссы подынтегральной Функции вправо. С выхода дешифратора 12 ввдается тактов ый импульс на счетный вход счетчика. 8, а с выхода, элемента И 17 на вход синхронизации регистра 14. Тем самьом регистр переходит из режима хранения в режим продвижения информации вправо на один такт, в счетчике 8 к порядку прибавляется единица. После сдвига на один такт мантиссы в дешифраторе 12 анализи: руются знаковые разряды и при сов паде:ний з накъвых раз рядов с нимается сигнал нормализации. При этом регистр 14 и счетчик 8 переходят а режим хранения информации.

Если в результате анализа бка ; ШйШё7ЧТ0 в- рёх дтар1ийх 15а;эрядах

(из которых два знаковые) ШйтИесзЫ : все нули или единицы, то дешифратором 12 вырабатйваетсйййгйгал ИИ нор-

малйзацию влево; т Ш йгИ1ПЙ5ет -

---

8, регистра 14, элемента И 17. При этом настраивается счетчик 8 йа вычитание тактовых импульсов и регистр 14 на сдвиг кода; май йесы подынтегральной функции влево. С выхода дешифратора 12 вьщаюТсГ rfSRtOвые импульсы на вход счетчика 8.и с выхода элемента И 17 на синхронизирующий вход регистра 14. Тем самым

- 1 ср|- пё хШй ШрёЖй-|й

в режим продвижения инфЬрМШйй влево, а в счетчике 8 из пЪрадкавычитаются единицы. Псюлё каждого такта

в дешифраторе 1Га1ШШэ1Й У15 51 -д1« знаковых и один старший разряд йдса щ Щ54рн 3 щ |р15 е1 щ

разрядасо jHaKOBbTMH снимается по,, тенциалн|5риали ац;ийГ При 6 й

1 шШйГ1Ш1 граШЬс 1етея

в квантователе 15 аналогично нормализации мантиссы подынтегральной функции в дешифраторе 12 и регистре 14. По окончанию норйайЖзаи йййантйеей подынтегральной функций и приращения интегратора из усТрЬйстваТпр1Ш1ейия |10Ступаёт б ёнЦиШ ;ввдёления° йращения на вход 26 квантователя 15,

на входы элемента И-НЕ 2, блоков 3, 4, счетчика 8, сумматора 1.

Начинается следующий шаг интегрирования. Для выделения остатка приращения сдвигается на один такт влево нормализованная мантисса приращения. При этом стирается старший разряд приращения, а оставшаяся частявляется остатком приращения. В связи с этим при формировании входных приращений весовые разряды приращений имеют порядки на единицу меньше.

Изобретение позволит автоматически согласовать работу ьцифровых интеграторов, повысить скорость вычисления, значительно сократить аппаратурные затраты.

Формула изобретения Цифровой интегратор, содержащий сумматор приращений , сумматор подынтегральной функции и регистр сдвига, о тличающийс я тем, что, с целью повышения быстродействия в него введены блок суммирования , порядков, блок вычитания порядков, первый и второй счетчики, триггер, первый и второй дешифраторы, квантователь, первый и второй блок формирования тактовых импульсов, преобразователь чисел в дополнительный код, элементы И, ИЛИ, НЕ, И-НЕ, причем выход сумматора приращений соединен с первым входом сумматора подынтегральной функции, выход к.оторбго соединен со входом старшего

.разряда регистра сдвига и спервым входом преобразователя чисел в дополнительный код, выходы первых трех c SpiioiJc разрядов регистра сдви1 а подключены соответственно к первы трем входам первого дешифратора, выход младшего разряда регистра сдвига соединен со вторым входом сумматора подынтегрёшьной функции, первый выход первого- дешифратора соединен с первым входом первого счетчика, с первым уходом первого элемента И и со вторым входом регистра сдвига,Второй выход - со вторым входом первого счетчика и с первым входом первого элемента ИЛИ, третий выход - с третьим и четвертым входами первого счёГчика, выход которого сое Дйнён « Первым входЬм сумматора приращений и с первым входом блока суммирования порядков, выход первого элемента ИЛИ соединен с треТгбйм входом регистра сдвига и со StOptw входом первого элемента И, выход которого подключен к четвертому входу регистра сдвига, выход блока суммирования порядков соединен с первым входом блока вычитания порядков, первый и второй выходы которого подключены соответственно к первому и второму входам второго счетчика, третий выход блока вычит-анй я порядков соединен с первым

(ВХОДОМ второго дешифратора, выход

которого соединен с первым входом квантователя, четвертый выход блока вычитания порядков соединен с первым входом первого блока формирования тдктовых импульсов, выход которого соединен со входом элемента НЕ, с первыми входами второго и третьего элементов И и со вторым входом квантователя, выход элемента НЕ соединен с первыми входами четвертого и пятого элемента И, выход второго блока формирования тактовых импульсов соединен с третьим и четверть входами второго счетчика, выход которого соединен с первым и вторым входами триггера, первый выход триггера соединен со вторыми входами второго и пятого элементов И, второй выход триггера соединен с первым входом второго блока формирования тактовых импульсов, пятый выход блока вычитания порядков соединен с третьим входом квантователя, первый выход которого соединен со вторым входом блока вычитания порядков, выход элемента И-НЕ соединен с третьим входами второго и пятого элементов И, со вторыми входами третьего и четвертого элементов И и с четвертым входом квантователя, пятый вход которого соединен с выходом преобразователя чисел в дополнительный код, выходы второго и четвертого элементов Исоединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен со

вторым входом сумматора приращений и со вторым входом первого элемента ИЛИ, выходы третьего и пятого элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход которого подключен к шестому ВХ9ДУ квантователя, Я входов сумматора приращений, второй вход блока суммирования порядков, первый вход элемента И-НЕ и второй вход преобразователя чисел в дополнительный код являются информационными входами устройства, второй выход квантователя является информационHjjM выходом устройства, третий вход сумматора приращения, третий и четвертый входы преобразователя чисел в дополнительный код, второй и третий входы элемента И-НЕ, третьи входы третьего и четвертого элементов И, четвертые входы третьего и пятого элементов И, седьмой, восьмой

0 и девятый входы квантователя, третий вход триггера, второй вход первого, второй и третий входы второго блоков вьщеления тактовых импульсов, третий вход блока суммирования по5рядков, третий и четвертый входы блока вь1читания порядков являются, управляющими входами устройства.

Источники информации, принятые во внимание при экспертизе

0

3t

Авторы

Даты

1979-05-05—Публикация

1975-12-02—Подача