Изобретение относится к вычислительной технике и может быть использовано для построений высокопроизводительных процессоров или систем с магистральной организацией.

Цель изобретения - повьшение быстродействия .

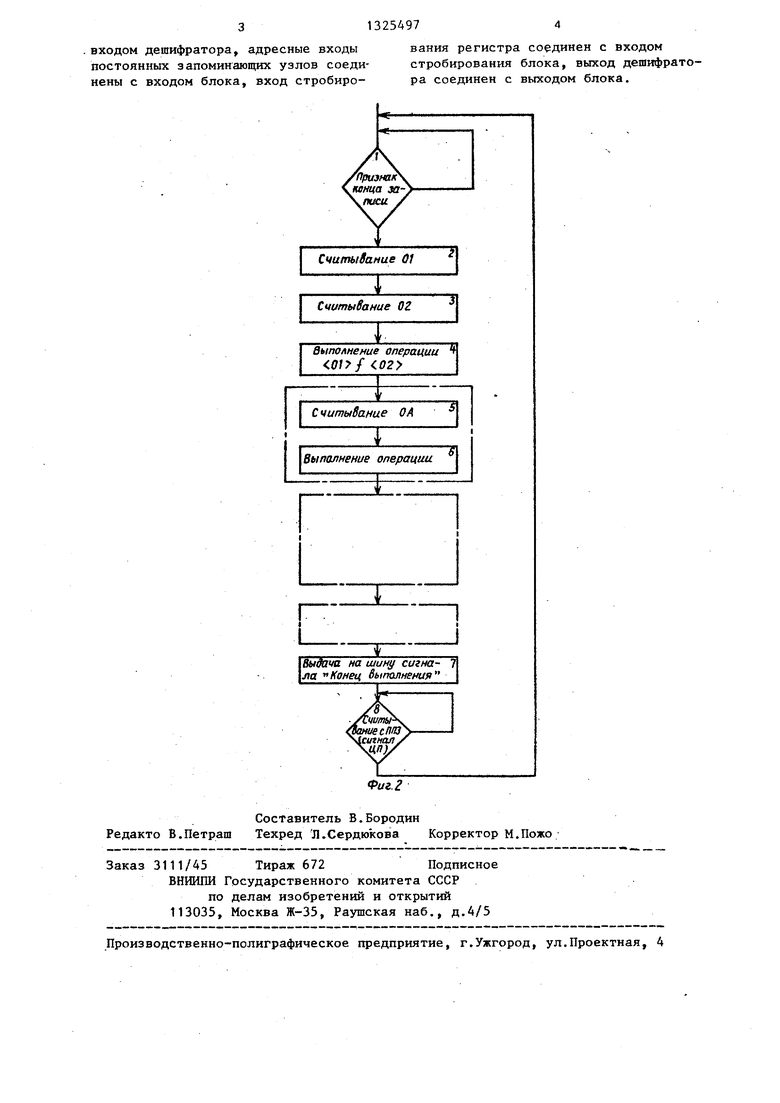

На фиг,1 приведена функциональная схема устройства; на фиг.2 - блок- схема алгоритма обмена.

Устройство содержит блок 1 дешифрации номера регистра, блок 2 регистров и блок 3 вывода информации. Блок 1 содержит п постоянных запоми- нающих узлов 4...4, шифратор 5, регистр 6 и дешифратор 7, блок 2 регистров - к регистров 8 ...8|, блок 3- KOMMytaTop 9.

Устройство работает следующим об- разом.

Центральный процессор 10 осуществляет сегментацию памяти, вычисляет адреса операндов, а вспомогательный процессор 11 выполняет сложные математические операции. Когда централь- ньй процессор 10 встречает команду, ориентирующую операцию для вспомогательного процессора 11, он определя- ет операнды, необходимые вспомогательному процессору 11, и осуществляет их загрузку в регистры 8,..8

блока 2,

i.Загрузка данных в блок 2 происхо-

дит следующим образом. Центральный процессор 10 выставляет на шину 12 адреса адрес одного из регистров 8 блока 2, одновременно вырабатывается сигнал стробирования адреса по шине 13 управления, и по этому сигналу двоичный код номера регистра, полученый на выходе шифратора 5, заносится в регистр 6. На выходе дешифратора 7 появляется сигнал выборки регистра блока 2. Одновременно на шину 14 данных выставляются данные. При появлении сигнала стробирования данных на шине 13 данные заносятся в .выбранный сигнал. Аналогичным образом происхо- дит занесение последз ощих операндов в регистры блока 2. Регистры В,...З блока 2 могут использоваться для передачи вспомогательному процессору 1 служебной информации, такой как номер подпрограммы-функции, адрес, с которого необходимо начать выполнение подпрограммы, адрес результата операции и т.д.

0

5

g

0 5 Q

5

После подготовки данных центральный процессор 10 передает управление вспомогательному процессору 11. Получив управление, вспомогательный процессор 11 начинает выполнять заданную подпрограмму и считьшает данные с регистров 8...8 блока 2.

Считывание данных осуществляется следующим образом. На адресных входах коммутатора 9 устанавливается информация, служащая управляющими сигналами для него. Коммутатор 9 открывается по необходимым входам, и данные с соответствующего регистра 8 поступают на его выход и далее на входы вспомогательного процессора 11.

После окончания выполнения подпрограммы вспомогательный процессор 11 вьщает сообщение центральному процессору 10 об .окончании работы.

Ф о р м ула изобретения

1.Устройство обмена данными, содержащее блок регистров, блок вывода информации, выход блока регистров соединен с информационньм входом блока вывода информации, выход которого является выходом устройства, вход стробирования данных блока регистров является входом стробирования данных устройства, информационный вход блока регистров является информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия, в него введен блок дешифрации номера регистра, причем выход блока дешифрации номера регистра соединен с входом выборки блока регистров, вход блока дешифрации номера регистров является первым адресным входом устройства, вход стробирования блока дешифрации номера регистра является входом стробирования адреса устройства, адресный вход блока выхода информации является вторым адресным входом устройства.

2.Устройство по п.1, о т л и ч а- ю щ е е с я тем, что блок дешифрации номера регистра содержит п постоянных запоминающих узлов, шифратор, регистр и дешифратор, причем выходы с первого по п-й постоянных запоминающих узлов соединены с входами шифратора, выход которого соединен с информационным входом регистра, выход которого соединен с информационным

входом дешифратора, адресные входы постоянных запоминающих узлов соединены с входом блока, вход стробирования регистра соединен с входом стробирования блока, выход дешифратора соединен с выходом блока.

Считывание 02

выполнение операции 0nf 02

Считывание О А

I Выт

L

Выполнение операции

Г

L.

на шину сигна- 7 ло Конец 6ытлнеии1

Редакто В.Петраш

Составитель В.Бородин

Техред Л.Сердюкова Корректор М.Пожо

Заказ 3111/45 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена данными | 1989 |

|

SU1615731A2 |

| Устройство обмена данными | 1989 |

|

SU1697083A2 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Процессор | 1984 |

|

SU1247884A1 |

| Устройство для решения нелинейных краевых задач | 1987 |

|

SU1683028A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Мультиплексный канал | 1978 |

|

SU744540A2 |

| Устройство для поиска информации на ленточном носителе | 1984 |

|

SU1208564A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

Изобретение относится к вычислительной технике и может ис/J пользойано для построения высокопро- изводительных процессоров или систем с магистральной организацией. Цель изобретения - повьшение быстродействия , Устройство содержит блок 1 дешифрации номера регистра, блок 2 регистров, блок 3 вывода информации. В процессе обмена центральный процессор 10 заносит данные для вспомогательного процессора 11 в блок 2 регистров, оттуда они считываются вспомогательным процессором 11 через блок 3 вывода информации. 1 з.п. ф-Л1 2 ил.

| Шаговый конвейер | 1988 |

|

SU1565790A1 |

| Балашов Е.П | |||

| и др | |||

| Микро-и мини- ЭВМ | |||

| - Л.: Энергоатомиздат, 1984, стр.108-111. | |||

Авторы

Даты

1987-07-23—Публикация

1986-03-18—Подача