сл

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена данными | 1989 |

|

SU1615731A2 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство обмена данными | 1986 |

|

SU1325497A1 |

| Устройство для сопряжения процессора с устройствами вывода | 1984 |

|

SU1206788A1 |

| Устройство для связи процессора с запоминающим устройством | 1983 |

|

SU1083196A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Дисплейный процессор | 1981 |

|

SU1292031A1 |

| Устройство для сопряжения ЭВМ с внешним абонентом | 1988 |

|

SU1594553A1 |

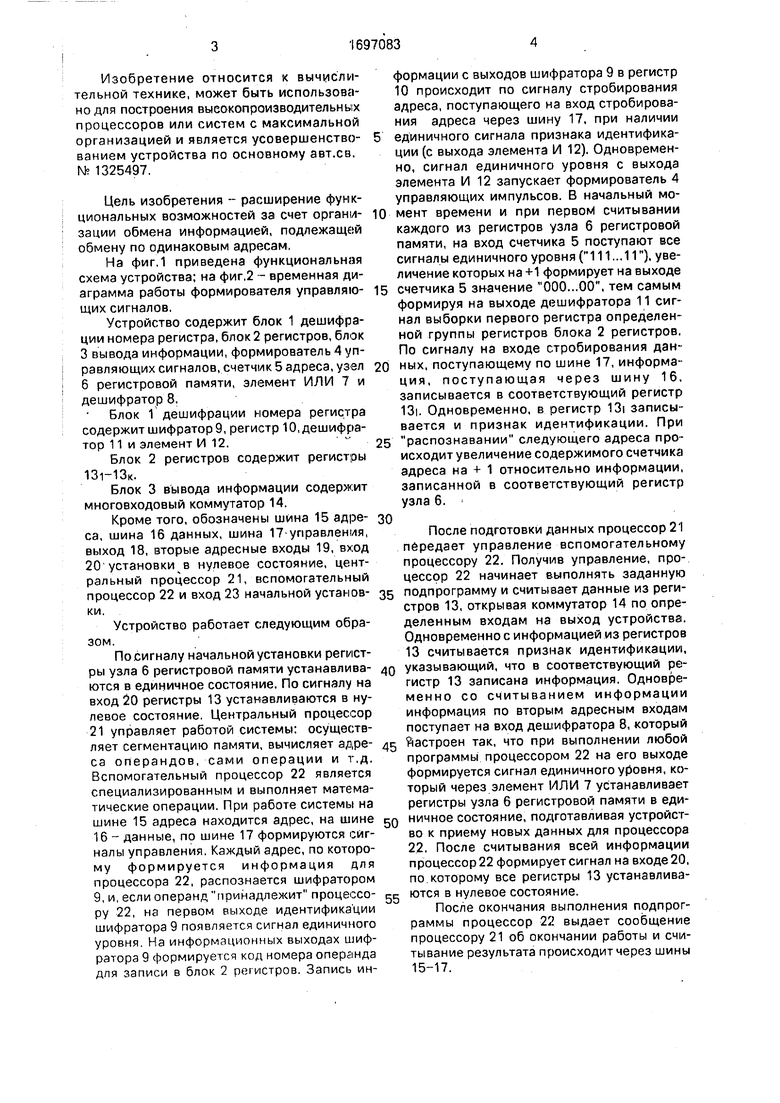

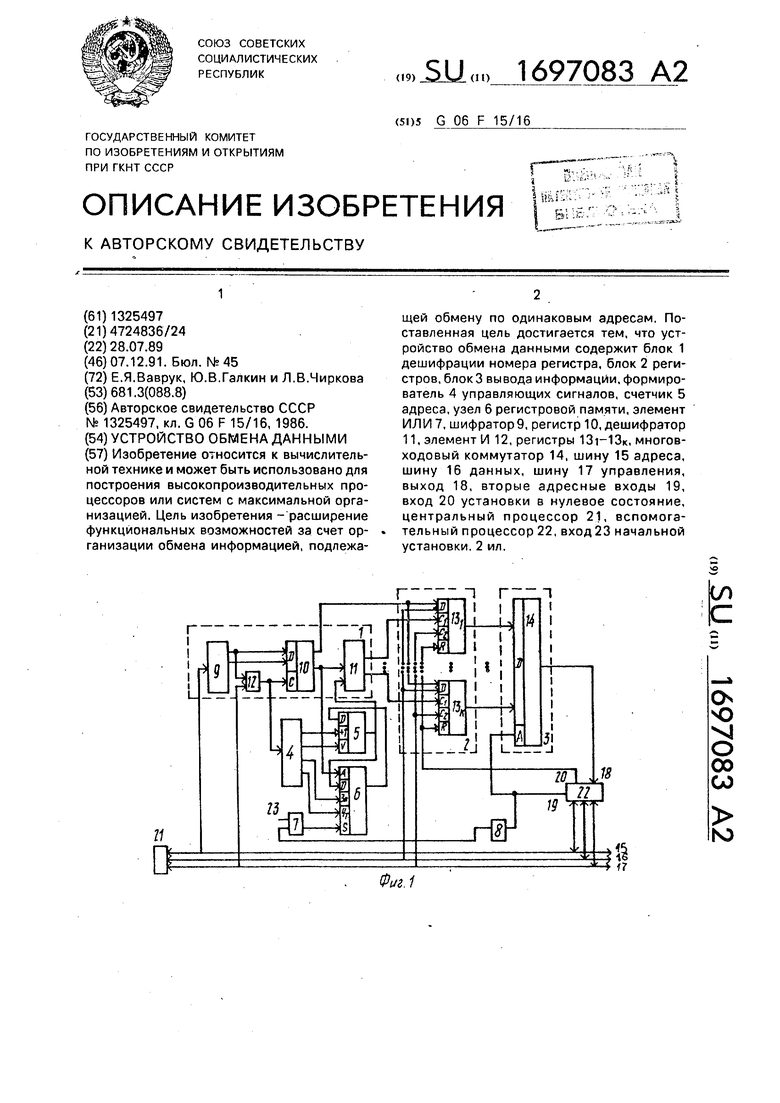

Изобретение от носится к вычислительной технике и может быть использовано для построения высокопроизводительных процессоров или систем с максимальной организацией. Цель изобретения - расширение функциональных возможностей за счет организации обмена информацией, подлежащей обмену по одинаковым адресам. Поставленная цель достигается тем, что устройство обмена данными содержит блок 1 дешифрации номера регистра, блок 2 регистров, блок 3 вывода информации, формирователь 4 управляющих сигналов, счетчик 5 адреса, узел 6 регистровой памяти, элемент ИЛИ 7, шифраторЭ, регистр 10, дешифратор 11, элемент И 12, регистры 131-13к, многов- ходовый коммутатор 14, шину 15 адреса, шину 16 данных, шину 17 управления, выход 18, вторые адресные входы 19, вход 20 установки в нулевое состояние, центральный процессор 21, вспомогательный процессор 22, вход 23 начальной установки.2 ил.

21

о ю VI о

00

со

N)

Изобретение относится к вычислительной технике, может быть использовано для построения высокопроизводительных процессоров или систем с максимальной организацией и является усовершенствованием устройства по основному авт.св. № 1325497.

Цель изобретения - расширение функциональных возможностей за счет организации обмена информацией, подлежащей обмену по одинаковым адресам,

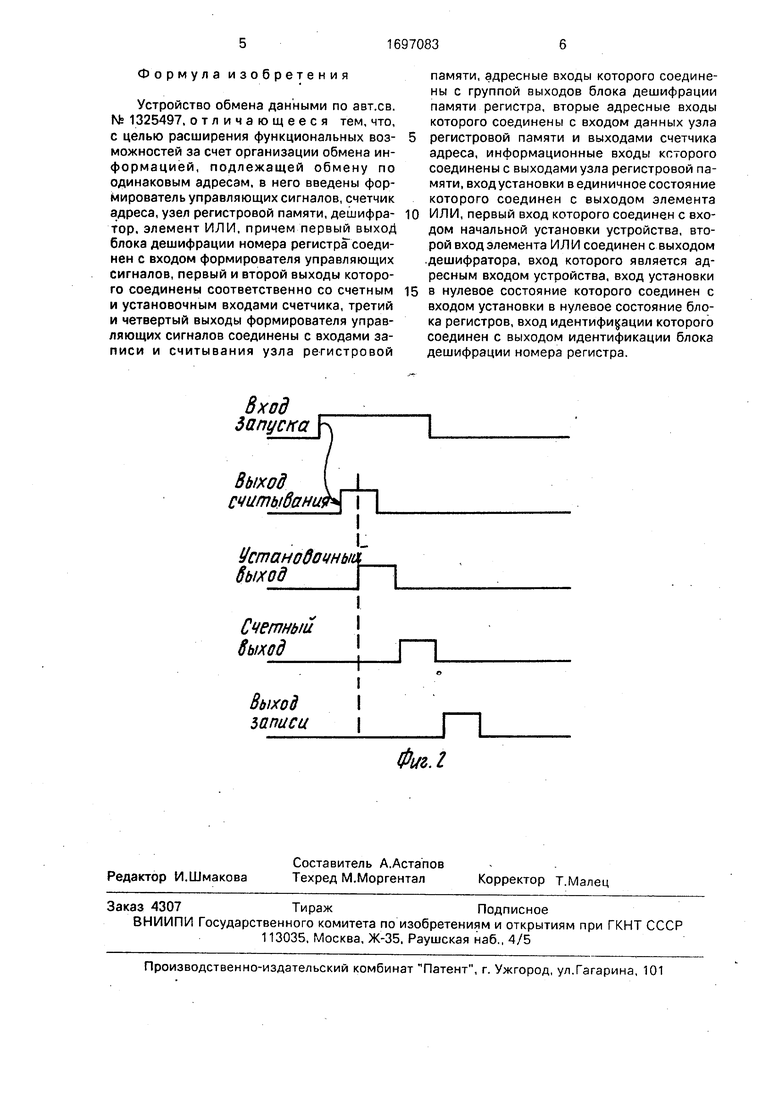

На фиг.1 приведена функциональная схема устройства; на фиг,2 - временная диаграмма работы формирователя управляющих сигналов.

Устройство содержит блок 1 дешифрации номера регистра, блок2 регистров, блок 3 вывода информации, формирователь 4 управляющих сигналов,счетчик 5 адреса,узел 6 регистровой памяти, элемент ИЛИ 7 и дешифратор 8.

Блок 1 дешифрации номера регистра содержит шифратор 9, регистр 10, дешифратор 11 и элемент И 12.

Блок 2 регистров содержит регистры

13i-13K.

Блок 3 вывода информации содержит многовходовый коммутатор 14.

Кроме того, обозначены шина 15 адреса, шина 16 данных, шина 17 управления, выход 18, вторые адресные входы 19, вход

20установки в нулевое состояние, центральный процессор 21, вспомогательный процессор 22 и вход 23 начальной установки.

Устройство работает следующим образом.

По сигналу начальной установки регистры узла 6 регистровой памяти устанавливаются в единичное состояние. По сигналу на вход 20 регистры 13 устанавливаются в нулевое состояние. Центральный процессор

21управляет работой системы: осуществляет сегментацию памяти, вычисляет адреса операндов, сами операции и т.д. Вспомогательный процессор 22 является специализированным и выполняет математические операции. При работе системы на шине 15 адреса находится адрес, на шине 16 - данные, по шине 17 формируются сигналы управления. Каждый адрес, по которому формируется информация для процессора 22, распознается шифратором 9, и, если операнд принадлежит процессору 22, на первом выходе идентификации шифратора 9 появляется сигнал единичного уровня. На информационных выходах шифратора 9 формируется код номера операнда для записи в блок 2 регистров. Запись информации с выходов шифратора 9 в регистр 10 происходит по сигналу стробирования адреса, поступающего на вход стробирования адреса через шину 17, при наличии

единичного сигнала признака идентификации (с выхода элемента И 12). Одновременно, сигнал единичного уровня с выхода элемента И 12 запускает формирователь 4 управляющих импульсов. В начальный мо0 мент времени и при первом считывании каждого из регистров узла 6 регистровой памяти, на вход счетчика 5 поступают все сигналы единичного уровня (111...11), увеличение которых на +1 формирует на выходе

5 счетчика 5 значение 000...00, тем самым формируя на выходе дешифратора 11 сигнал выборки первого регистра определенной группы регистров блока 2 регистров. По сигналу на входе стробирования дан0 ных, поступающему по шине 17, информация, поступающая через шину 16, записывается в соответствующий регистр 13|. Одновременно, в регистр 13i записывается и признак идентификации. При

5 распознавании следующего адреса происходит увеличение содержимого счетчика адреса на + 1 относительно информации, записанной в соответствующий регистр узла 6.

0

После подготовки данных процессор 21

передает управление вспомогательному процессору 22. Получив управление, процессор 22 начинает выполнять заданную

5 подпрограмму и считывает данные из регистров 13, открывая коммутатор 14 по определенным входам на выход устройства. Одновременно с информацией из регистров 13 считывается признак идентификации,

0 указывающий, что в соответствующий регистр 13 записана информация. Одновременно со считыванием информации информация по вторым адресным входам поступает на вход дешифратора 8, который

5 настроен так, что при выполнении любой программы процессором 22 на его выходе формируется сигнал единичного уровня, который через элемент ИЛИ 7 устанавливает регистры узла 6 регистровой памяти в еди0 ничное состояние, подготавливая устройство к приему новых данных для процессора 22, После считывания всей информации процессор 22 формирует сигнал на входе 20, по которому все регистры 13 устанавлива5 ются в нулевое состояние.

После окончания выполнения подпрограммы процессор 22 выдает сообщение процессору 21 об окончании работы и считывание результата происходит через шины 15-17.

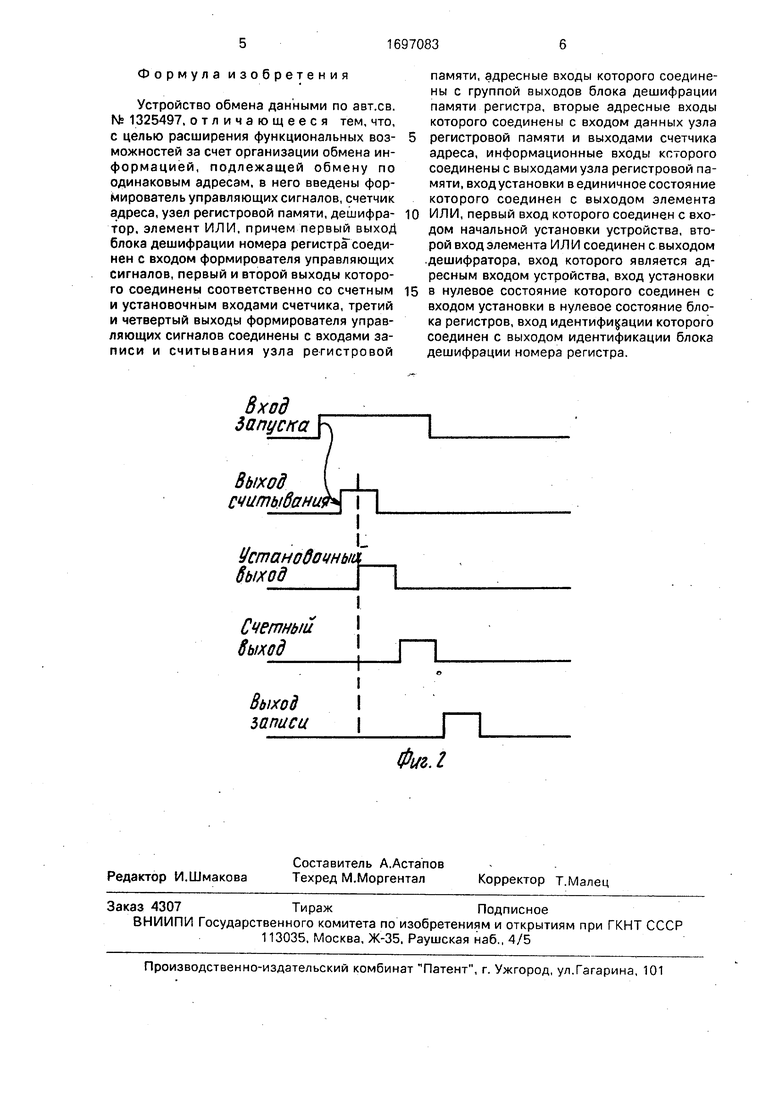

Формула изобретения

Устройство обмена данными по авт.св. Ms 1325497, отличающееся тем, что, с целью расширения функциональных возможностей за счет организации обмена информацией, подлежащей обмену по одинаковым адресам, в него введены формирователь управляющих сигналов, счетчик адреса, узел регистровой памяти, дешифратор, элемент ИЛИ, причем первый выход блока дешифрации номера регистра соединен с входом формирователя управляющих сигналов, первый и второй выходы которого соединены соответственно со счетным и установочным входами счетчика, третий и четвертый выходы формирователя управляющих сигналов соединены с входами записи и считывания узла регистровой

Устанобочньи выход

памяти, адресные входы которого соединены с группой выходов блока дешифрации памяти регистра, вторые адресные входы которого соединены с входом данных узла

регистровой памяти и выходами счетчика адреса, информационные входы которого соединены с выходами узла регистровой памяти, вход установки в единичное состояние которого соединен с выходом элемента

0 ИЛИ, первый вход которого соединен с входом начальной установки устройства, второй вход элемента ИЛИ соединен с выходом .дешифратора, вход которого является адресным входом устройства, вход установки

5 в нулевое состояние которого соединен с входом установки в нулевое состояние блока регистров, вход идентификации которого соединен с выходом идентификации блока дешифрации номера регистра.

J-I

01Л.1

| Устройство обмена данными | 1986 |

|

SU1325497A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-12-07—Публикация

1989-07-28—Подача