1

Изобретение относится к вычислительной технике и может быть исполь- зонано при разработке многопроцессор ных систем, в частности мультимикро- процессорных. .

Целью изобретения является сокращение затрат оборудования.

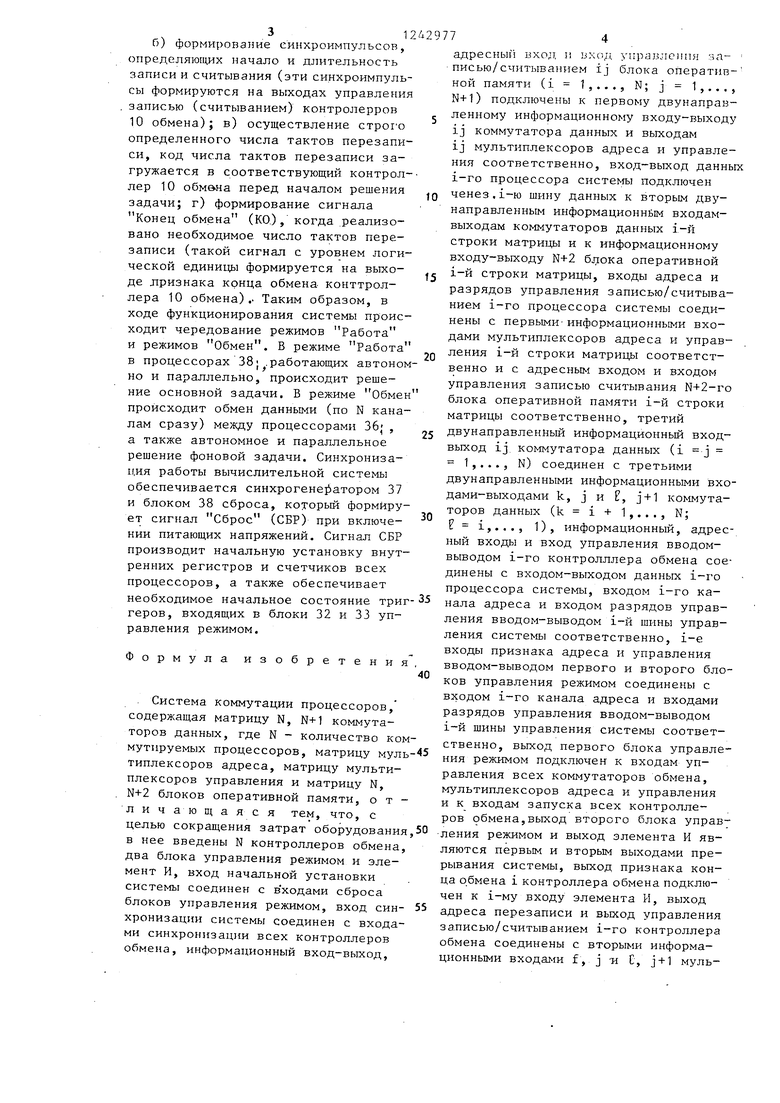

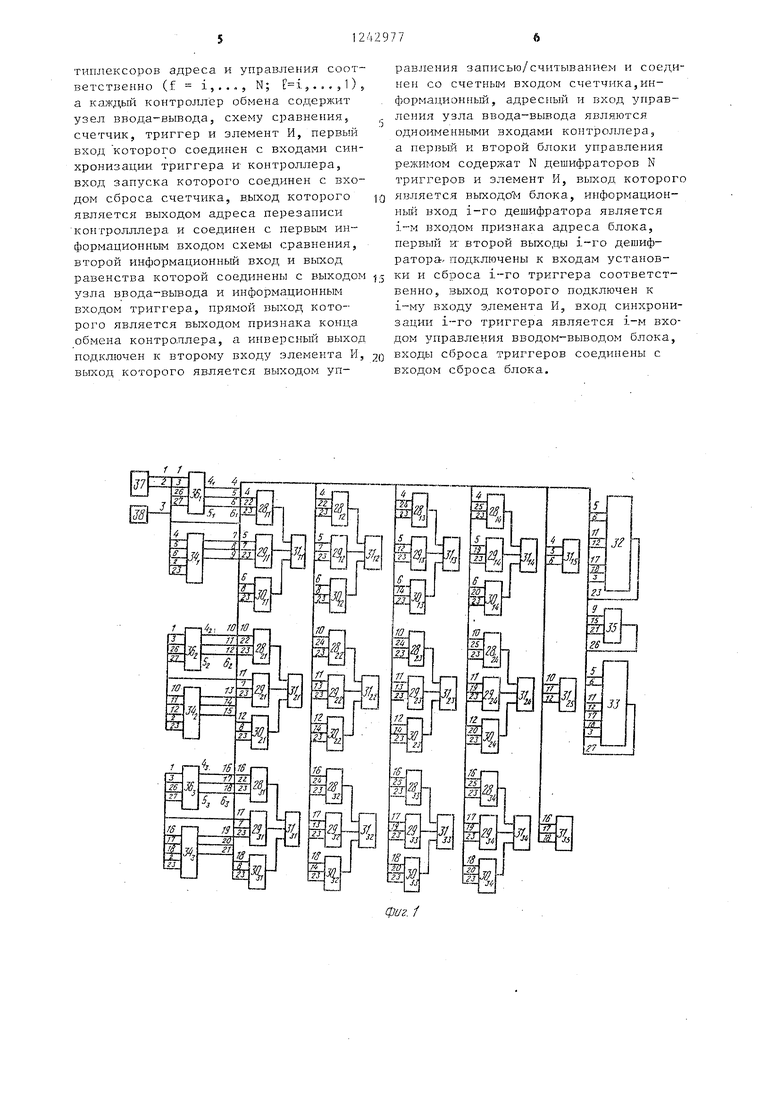

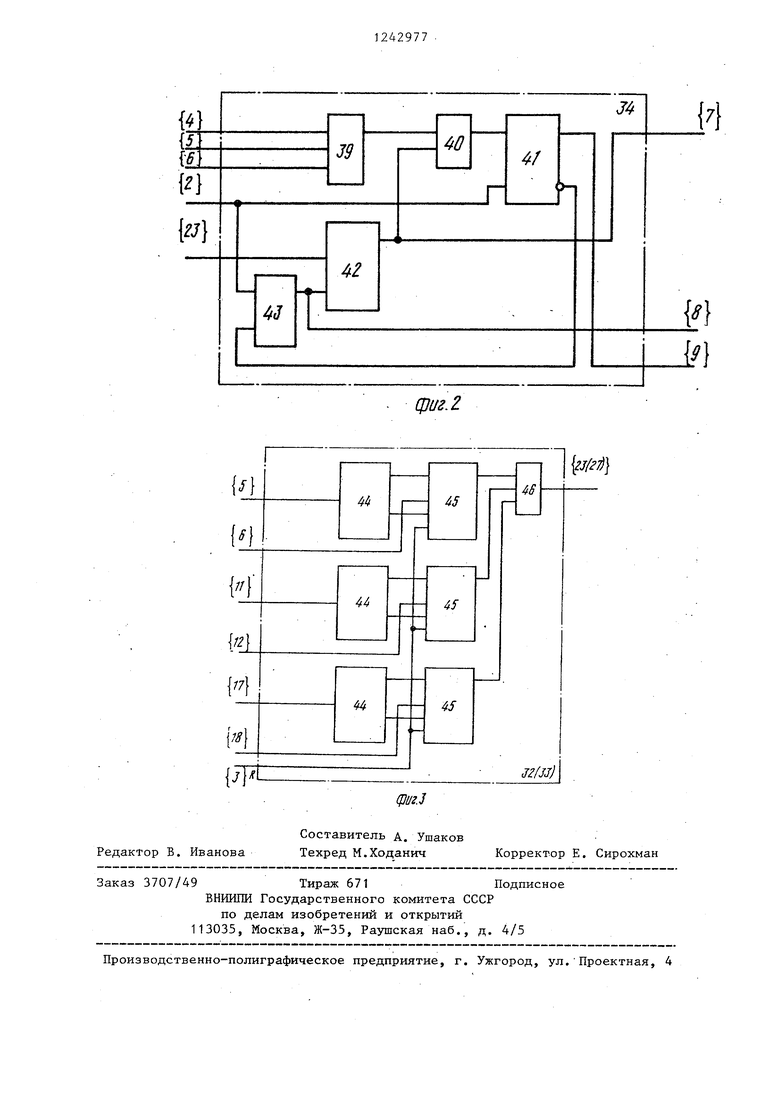

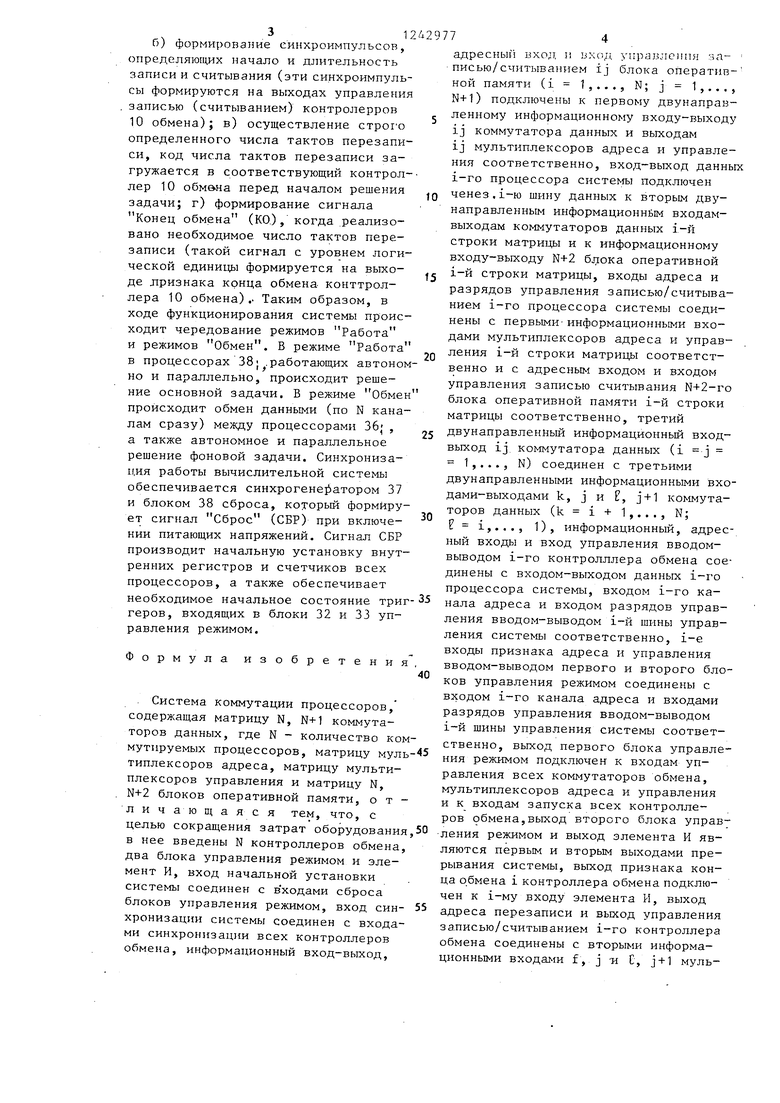

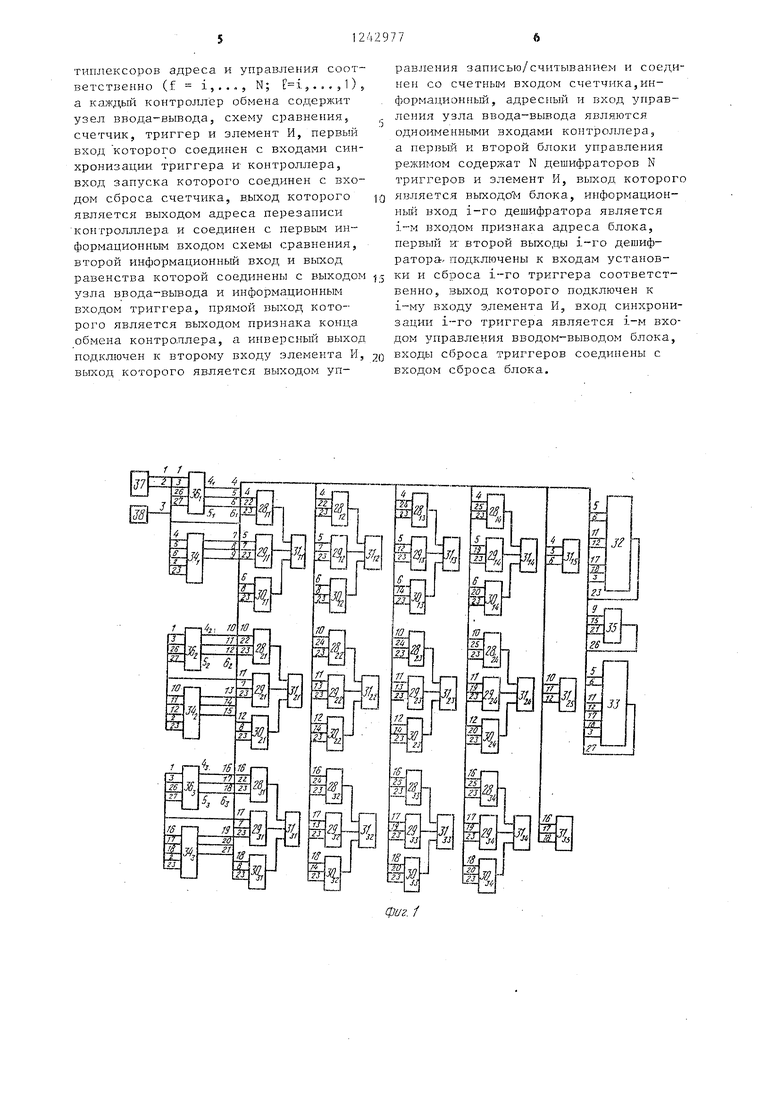

На фиг. 1 представлена функциональная схема системы при N 3, i ,,..,3; j. 1,...,5; на фиг.2 функциональная схема контроллера обмена, соответствующего первому процессору системы, в фигурных скобках сохранены номера шин и проводников жгута, приведенного на фиг. 1; на фиг. 3 - функциональная схема блоков управления режимом.

Вычислительная система, построенная с использованием предложенной системы коммутации процессоров, содержит шину 1 синхронизации процессоров 5шину 2 синхронизации системы,шин 3 сброса системы, шины 4-6 данных, адреса управления первого процессора шины 7-9 - адреса перезаписи управления записью/считыванием и конца обмена первого процессора, шины 10-15 втрого процессора и 16-21 третьего процессора, которые имеют, аналогичное Ф5 нкциональное назначение и название соответственно шинам 4-9 первого процессора, первую шину 22 обмена данны шину 23 запуска обмена, вторую 24 и третью 25 шины обмена да.нных, первую 26 и вторую шины 27 прерывания,а систе коммутации содержит матрицу N, N+1 коммутаторов 28- данных, матрицу мультиплексоров 29, J адреса и 30, J управления,матрицу N,N+2 блоков 31 оперативной памяти, первый н второй блоки 32 и 33 управления режимов, N контроллеров обмена 34{ , элемент И 35. К системе коммутации подключаются процессоры 36, а для обеспечения ее работы подключен синхр генератЬр 37 и блок 38 сброса.

Каждый контроллер 34 обмена содержит узел 39 ввода/вьшода, схему 40 сравнения, триггер 41, счетчик 42 и элемент И 43.

Каждый блок 32 (33) управления р жимом содержит N дешифраторов 44, N триггеров 45, элемерт И 46.

Система работает следующим образом.

Все микроэвм, подключаемые к системе коммутации, идентичны по структуре .

1

Если сигнал на входах управления

0

5

5

0

5

коммутаторов 28,; и мультиплексоров 29, ;, 30;j, назовем его Обмен/работа (0/Р),равен нулю,т.е. ,то блоки

31jj (где I

N; j .1, N+1)

0

подключены к внутренним шинам своих процессоров 36,. Так, например, информационные входы блоков 31,-31, через ком1 утаторы 28. 28, .подключены к тине 4 данных, адресные входы блоков 31,I-31, через мультиплексоры 29, -29, подключены KI шине 5 адреса, входы управления записью (считыванием) блоков ц через мульти5 плексоры ЗО,, подключены к шине 6 управления.При этом блоки 31, образуют единый модуль оперативной памяти перйого процессора, все ячейки которого доступны для адресации их первым процессором. В таком режиме производится -решение основной задачи параллельно тремя процессорами При 0/Р 1 блоки 31,. отключаются от внутренних шин соответствующих процессоров, при этом возникает возможность для обмена данными между всеми процессорами одновременно. JIpH,реализации обмена блоки 31;;- 2 не отключаются от внутренних шин своих i х

процессоров 36:j (к таким относятся блоки 31, 31j, 31), поэтому процессоры в режиме обмена сохраняют возможность решать фоновую задачу. В ре- jKHMe обмена определенные блоки 31;;

28:j и мультиплексокоммутаторыи 30.

J

через

ры 29; и 30,-j связываются между собой, образуя цепочки блоков 31, ;, Обмен разрешен только внутри определенной цепочки блоков 31 и только следующим образом: один блок 31;j этой цепочки работает на считыв ание, остальные - на запись, Например, в первой цепочке таким блоком является блок 31,, , во второй 312, 5 в третьей 31,. Такой режим обмена в цепочках блоков 31 обеспечивается подачей синхроимпульсов, определяющих начало и длительность занкрси и считывания, которые формируются на выходах управления записью (считыванием) соответствующих контролллеров 10 обмена, на вход счи- тьюания блоков 31, , из которых производится считывание данных, а на

вход записи блоков 31

ч

в которые

производится запись данных. В функции 55 контроллеров 10 обмена входит:

а) формирование адреса перезаписи (для всех блоков 31;; ) ,312

б) формирование синхроимпульсов,

определяющих начало и длительность записи и считывания (эти синхроимпульсы формируются на выходах управления записью (считыванием) контролерров 10 обмена); в) осуществление строг о определенного числа тактов перезаписи, код числа тактов перезаписи загружается в соответствующий контроллер 10 обмена перед началом решения задачи; г) формирование сигнала Конец обмена (КО.), когда реализовано необходимое число тактов перезаписи (такой сигнал с уровнем логической единицы формируется на выходе лризнака конца обмена конттрол- лера 10 обмена).- Таким образом, в ходе функционирования системы происходит чередование режимов Работа и режимов Обмен. В режиме Работа в процессорах 38j .работающих автономно и параллельно, происходит решение основной задачи. В режиме Обмен происходит обмен данными (по N каналам сразу) между процессорами 36| , а также автономное и параллельное решение фоновой задачи. Синхронизация работы вычислительной системы обеспечивается синхрогене1)атором 37 и блоком 38 сброса, который формирует сигнал Сброс (СВР) при включении питающих напряжений. Сигнал СВР производит начальную установку внутренних регистров и счетчиков всех процессоров, а также обеспечивает необходимое начальное состояние триггеров, входящих в блоки 32 и 33 управления режимом.

Формула изобретения

Система коммутации процессоров, содержащая матрицу N, N+1 коммутаторов данных, где N - количество коммутируемых процессоров, матрицу муль- З типлексоров адреса, матрицу мультиплексоров управления и матрицу N, N+2 блоков оперативной памяти, отличающаяся тем, что, с целью сокращения затрат оборудования,50 в нее введены N контроллеров обмена, два блока управления режимом и элемент И, вход начальной установки системы соединен с в ходами сброса блоков управления режимом, вход син- 55 хронизации системы соединен с входами синхронизации всех контроллеров обмена, информационный вход-выход.

,

0

5

0

5

0

З 0 5

9774

адресный вход и вход управлелпя за- писью/считыванием ij блока оператив- ной памяти (i 1,..., N; j 1,..., N+1) подключены к первому двунапран- , ленному информационному входу-выходу ij коммутатора данных и выходам ij мультиплексоров адреса и управления соответственно, вход-выход данных i-ro процессора системы подключен чeнeз.i-ю шину данных к вторым двунаправленным информационнЁм входам- выходам коммутаторов данных i.-й строки матри1д 1 и к информационному входу-выходу N+2 блока оперативной i-й строки матрицы, входы адреса и разрядов управления записью/считыванием i-ro процессора системы соединены с первыми-информационными входами мультиплексоров адреса и управления i-й строки матрицы соответственно и с адресным входом и входом управления записью считывания N+2-го блока оперативной памяти i-й строки матрицы соответственно, третий двунаправленный информационный вход- выход ij. коммутатора данных (i j 1 ,. .., N) соединен с третьими двунаправленными информационными входами-выходами k, j и Е, J+1 коммутаторов данных (k i + 1,..., N; i,.. . , 1), информационный, адресный входы и вход управления вводом- выводом i-ro контролллера обмена соединены с входом-выходом данных i-ro процессора системы, входом i-ro канала адреса и входом разрядов управления вводом-выводом i-й шины управления системы соответственно, i-e входы признака адреса и управления вводом-выводом первого и второго блоков управления режимом соединены с входом i-ro канала адреса и входами разрядов управления вводом-выводом i-й шины управления системы соответственно, выход первого блока управления режимом подключен к входам управления всех коммутаторов обмена, мультиплексоров адреса и управления и к входам запуска всех контроллеров обмена,выход второго блока управу -ления режимом и выход элемента И являются первым и вторым выходами прерывания системы, выход признака конца о.бмена i контроллера обмена подключен к i-му входу элемента И, выход адреса перезаписи и выход управления записью/считыванием i-ro контроллера обмена соединены с вторыми информационными входами f, j И С, J + 1 муль0

5

типлексоров адреса и управления соответственно (f i,..., N; ,..,,1)5 a каждьш контроллер обмена содержит узел ввода-вывода, схему сравнения счетчик, триггер и элемент И, первый вход которого соединен с входами синхронизации триггера и контроллера, вход запуска которого соединен с входом сброса счетчика, выход которого является выходом адреса перезаписи контролллера и соединен с первым информационным входом сравнения, второй информационный вход и выход равенства которой соединены с выходом узла ввода-вывода и информационным входом триггера, прямой выход которого является выходом признака конца обмена контроллера, а иьшерсный выход подключен к второму входу элемента И, выход которого является выходом управления записью/считыванием и соединен со счетньИ входом счетчика,информационный, адресный и вход управления узла ввода-вывода являются одноименными входами контроллера, а первый и второй блоки управления режимом содержат N дешифраторов N триггеров и элемент И, выход которог является выxoдo блока, информацион- ньй вход i-го дешифратора является i-M входом признака адреса блока, первый и- второй выходы дешифратора, подключены к входам установки и сброса i-ro триггера соответственно, выход которого подключен к 1-му входу элемента И, вход синхронизации i-ro триггера является i-м входом управления вводом-выводом блока, входы сброса триггеров соединены с входом сброса блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| СИСТЕМА КОММУТАЦИИ ПРОЦЕССОРОВ | 1991 |

|

RU2006931C1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Распределенная система для программного управления технологическими процессами | 1990 |

|

SU1797096A1 |

| Мультипрограммное вычислительное устройство | 1990 |

|

SU1777147A1 |

| Система для обмена информацией | 1980 |

|

SU980087A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Цифровое устройство доплеровской фильтрации | 1990 |

|

SU1830496A1 |

| Устройство для быстрого преобразования Фурье | 1985 |

|

SU1304034A1 |

| Устройство для определения среднеквадратического значения переменного сигнала | 1989 |

|

SU1781686A1 |

Изобретение относится к вычислительной технике и может быть использовано для организации эффективного обмена между процессорами при небольших затратах оборудования. Система коммутации содержит матрицу N, N+1 коммутаторов данных, где N - число подключаемых к системе процессоров, матрицу N, N+1 мультиплексоров адреса и управления, матрицу N, N+2 блоков оперативной памяти, первый и второй блоки управления режимом, N контроллеров обмена, элемент И. Функционирование системы происходит в чередующихся режимах Работа и Обмен. В режиме Работа процессоры работают параллельно и автономно и решают основную задачу. В режиме Обмен происходит обмен данными между N процессорами по N шинам данных одновременно, а также параллельно и автономное решение фоновой задачи. 2 ил. (О (Л ю |N5

1 / .-.

фиг.2

{18

{Л

В. Иванова

фиг.

Составитель А. Ушаков Техред М.Ходанич

Заказ 3707/49Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Е. Сирохман

| Аналоговые и цифровые интегральные микросхемы | |||

| Справочное пособие С.В | |||

| Якубовский и др | |||

| /Под ред | |||

| С.В | |||

| Якубовского, 2-е изд., перераб | |||

| и доп., М.: Радио и связь, 1985, с | |||

| Система механической тяги | 1919 |

|

SU158A1 |

| Заявка ФРГ № 3104928, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1979 |

|

SU1012232A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-07—Публикация

1984-07-04—Подача