1

(Л

с

Изобретение относится к вычисли- тыльной технике и может быть использовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональными основаниями и обработки век- информации в трехмерной систе- мЈ координат .

Цель изобретения - расширение функциональных возможностей за счет

с.

тожения в кодах с иррациональным

снованием

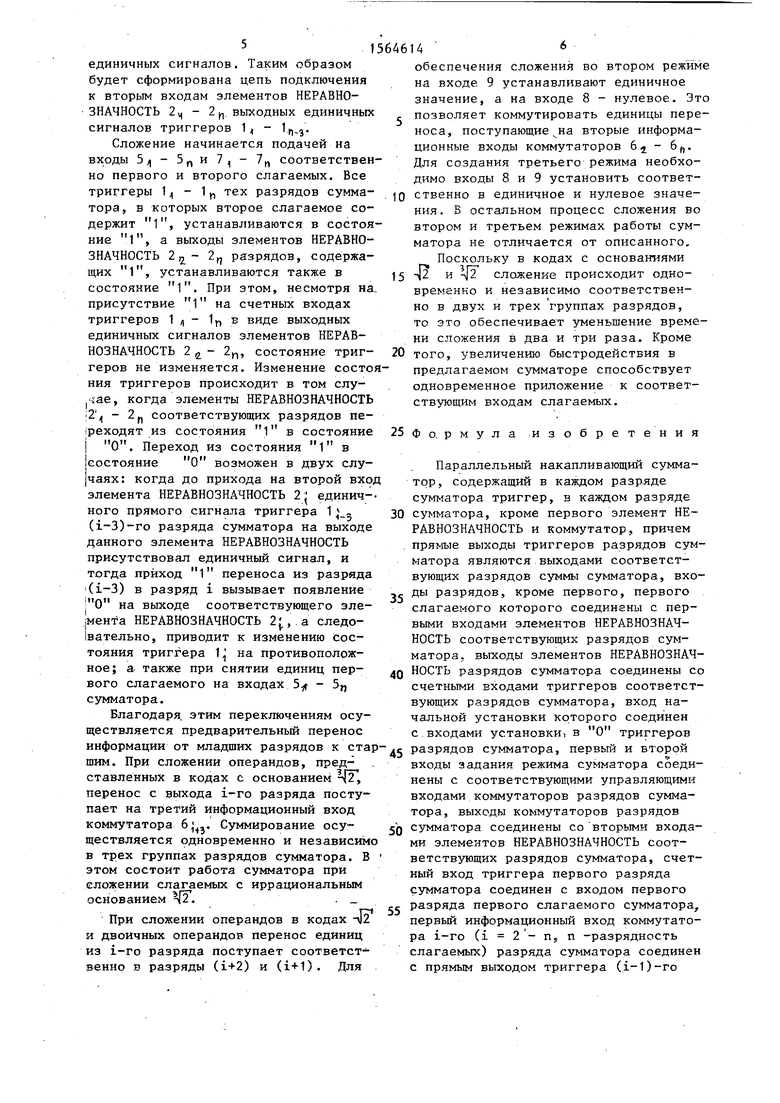

На чертеже представлена схема па р|аллельного накапливающего сумматора (для п 5) .

Сумматор содержит триггеры 14 -15 соответствующих разрядов сумматора, эпементы НЕРАВНОЗНАЧНОСТЬ 2г - 25 соответствующих разрядов сумматора, вход 3 начальной установки сумматора, выходы 4 -Ад- соответствующих разрядов суммы сумматора, входы 5.,- Зр соответствующих разрядов первого спагаемого сумматора, коммутаторы бд, -65 соответствующих разрядов сумматора, входы 7ц 75 соответствующих разрядов второго слагаемого сумматора, а также первый и второй входы 8 и 9 задания режима сумматора соответственно.

Коммутаторы 6Й - 65резлизованы на основе мультиплексоров.

Параллельный накапливающий сумматор предназначен для сложения one- р-андов и координат трехмерных векто- р)ов, представленных в двоично-кодированной позиционной системе счисления d иррациональным основанием -4 2 .

В этой системе счисления любое Число (вектор А) представляется в виде

А ап.,(Э42 ) + ... + а,)1 +

-i- a

,(V)°.

(1)

Учитывая, что веса разрядов данно- fo кода являются последовательностью Степеней основания 42

2, 2Щ 2.. 4, 1

И составляют три группы двоичных раз рйдов, умноженные на коэффициенты 1, ЦТ то выражение (1) можно представить в следующем виде:

п ч-Ј .„ п-2. j-i

А - V 51 а, 2 - /я

-чг- 0 /3

+ Ив а; 2

.%..,

2 3 +

(2)

где

ак, aj, a; Ј

(

0

k € 2,5,8,11

j e fl,4,7,10,

i e 0,3,6,9, п-3,

Выражение (2) позволяет любое чис- ло (вектор в трехмерном пространстве) изобразить в виде трех составных (векторов).

Особенностью такого изображения является то, что код с основанием s используемый для записи числа (вектора), единый и в то же время члены выражения (2) независимы друг от друга. Это позволяет при сложении двух операндов осуществить параллельное и независимое сложение составных частей операндов. Сложение двух одноименных разрядов в двоично-кодиро25

ванной системе счисления с иррациональным основанием выполняется согласно следующей таблице.

5

0 + 0 0 0+1 1 01 + 1 1000

Если в 1-х разрядах слагаемых имеются единицы, то, как это следует из таблицы, единица переноса поступает в (1+3)-й разряд кода.

Сумматор может работать в трех режимах: в режиме сложения операндов, представленных в коде с основанием 42 ; в режиме сложения операндов, представленных в коде с иррациональ- п ным основанием 42 J в режиме суммирования при двоичном представлении операндов.,

Первый режим обеспечивается приложением единичных сигналов к входам 8 и 9. Для создания второго режима в единичном состоянии находится только вход 9, а для создания третьего режима - только вход 8.

г

Параллельный накапливающий сум- п матор при сложении операндов в коде с иррациональным основанием -|2 работает следующим образом. Суммированию чисел предшествуют установка всех триггеров 1 - 1 п, в нулевое состояние путем приложения импульса к входу 3 и подача на входы 8 и 9 единичных значений, при этом обеспечивается приложение к первому и второму управляющим входам коммутаторов 6 ц. - 6„

51

единичных сигналов. Таким образом будет сформирована цепь подключения к вторым входам элементов НЕРАВНОЗНАЧНОСТЬ 2Ч - 2И выходных единичных сигналов триггеров 1,, - 1 Сложение начинается подачей на входы 5/| - 5П и 7, - 1п соответственно первого и второго слагаемых. Все триггеры 1 j| - 1 п тех разрядов сумматора, в которых второе слагаемое содержит 1, устанавливаются в состояние 1, а выходы элементов НЕРАВНОЗНАЧНОСТЬ 2П разрядов, содержащих 1, устанавливаются также в состояние 1. При этом, несмотря на присутствие 1 на счетных входах триггеров 1 ц - 1П в виде выходных единичных сигналов элементов НЕРАВНОЗНАЧНОСТЬ 2 й - 2П, состояние триггеров не изменяется. Изменение состония триггеров происходит в том слу- ае, когда элементы НЕРАВНОЗНАЧНОСТЬ 24 - 2П соответствующих разрядов переходят из состояния 1 в состояние | О. Переход из состояния 1 в состояние О возможен в двух слу- |чаях: когда до прихода на второй вход элемента НЕРАВНОЗНАЧНОСТЬ 2; единичного прямого сигнала триггера 1 „ (i-3)-ro разряда сумматора на выходе данного элемента НЕРАВНОЗНАЧНОСТЬ присутствовал единичный сигнал, и тогда приход 1 переноса из разряда (i-3) О

в разряд 1 вызывает появление на выходе соответствующего эле

,мента НЕРАВНОЗНАЧНОСТЬ 2;,, а следо- 1вательно, приводит к изменению состояния триггера 1 ,j на противоположное; а также при снятии единиц первого слагаемого на входах 5 - 5п сумматора.

Благодаря этим переключениям осуществляется предварительный перенос информации от младших разрядов к сташим. При сложении операндов, представленных в кодах с основанием ЦТ, перенос с выхода 1-го разряда поступает на третий информационный вход коммутатора . Суммирование осу- ществляется одновременно и независим в трех группах разрядов сумматора. В этом состоит работа сумматора при сложении слагаемых с иррациональным основанием Ч.

При сложении операндов в кодах и двоичных операндов перенос единиц из 1-го разряда поступает соответственно в разряды (i+2) и (i+1). Для

0

6

14

обеспечения сложения во втором режиме на входе 9 устанавливают единичное значение, а на входе 8 - нулевое. Это позволяет коммутировать единицы переноса, поступающиечна вторые информационные входы коммутаторов 64 - 6„. Для создания третьего режима необходимо входы 8 и 9 установить соответственно в единичное и нулевое значения. В остальном процесс сложения во втором и третьем режимах работы сумматора не отличается от описанного. Поскольку в кодах с основаниями $2 и 2 сложение происходит одновременно и независимо соответственно в двух и трех группах разрядов, то это обеспечивает уменьшение времени сложения в два и три раза. Кроме того, увеличению быстродействия в предлагаемом сумматоре способствует одновременное приложение к соответствующим входам слагаемых.

5

0

25 Формула изобретения

0

5

0

5

Ь

Параллельный накапливающий сумматор , содержащий в каждом разряде сумматора триггер, в каждом разряде сумматора, кроме первого элемент НЕРАВНОЗНАЧНОСТЬ и коммутатор, причем прямые выходы триггеров разрядов сумматора являются выходами соответствующих разрядов суммы сумматора, входы разрядов, кроме первого, первого слагаемого которого соединены с первыми входами элементов НЕРАВНОЗНАЧНОСТЬ соответствующих разрядов сумматора, выходы элементов НЕРАВНОЗНАЧНОСТЬ разрядов сумматора соединены со счетными входами триггеров соответствующих разрядов сумматора, вход начальной установки которого соединен с входами установки, в О триггеров разрядов сумматора, первый и второй входы задания режима сумматора соединены с соответствующими управляющими входами коммутаторов разрядов сумматора, выходы коммутаторов разрядов сумматора соединены со вторыми входами элементов НЕРАВНОЗНАЧНОСТЬ соответствующих разрядов сумматора, счетный вход триггера первого разряда сумматора соединен с входом первого разряда первого слагаемого сумматора, первый информационный вход коммутатора i-го (i 2- ns n -разрядность слагаемых) разряда сумматора соединен с прямым выходом триггера (i-1)-го

71564614 8

разряда сумматора, второй информа-рого слагаемого сумматора соединены цИоИный вход коммутатора второго раз-с входами установки в 1 триггеров Рида сумматора соединен с входом ну-соответствующих разрядов сумматора, левого потенциала сумматора, второйтретьи информационные входы коммута- ийформационный вход коммутатора k-roторов второго и третьего разрядов сум- (k 3-п) разряда сумматора соединенматора соединены с входом нулевого с прямым выходом триггера (k-2)-roпотенциала сумматора, третий информа- разряда сумматора, отличаю-ционный вход коммутатора р-го раэря- щ и и с я тем, что, с целью расшире- JQда (р 4-п) соединен с прямым выхо- ния функциональных возможностей задом триггера (р-З)-го разряда сумма- счет сложения в кодах с иррациональ-тора. HEJM основанием -42, входы разрядов вто

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Последовательный сумматор | 1989 |

|

SU1709298A2 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для суммирования двоичных чисел | 1988 |

|

SU1578709A2 |

| Последовательный сумматор | 1987 |

|

SU1411734A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения чисел с иррациональными основаниями и обработки векторной информации в трехмерной системе координат. Целью изобретения является расширение функциональных возможностей за счет сложения в кодах с иррациональным основанием √2. Сумматор содержит триггеры 11-15 разрядов сумматора, элементы НЕРАВНОЗНАЧНОСТЬ 22-25 разрядов сумматора, коммутаторы 62-65 разрядов сумматора с соответствующими связями. 1 ил., 1 табл.

| Сумматор кодов Фибоначчи | 1987 |

|

SU1411735A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1988-09-29—Подача