Изобретение относктся к вычислительной технике и может использовать ся при построении устройств параллел ного выполнения нескольких операций обработки двоичных чисел. Известно устройство обработки нескольких двоичных чисел,которое соде жит элементы И, ИЛИ, триггер и позво ляет реализовать любые операции- логи ческой обработки трех переменных 1 . . Недостаток этого устройства состо ;ит в том, что оно не реализует арифметических операций, например сложения, над несколькими переменными, чт ограничивает область его применения. Наиболее близким по технической сущности к данному изобретению является устройство для сложения п чисел содержащее двухвходовые сумматоры, группы элементов И, цепи входа, выхо да и поразрядного переноса .2 . Недостатком устройства является то, что Оно реализует только арифметические операции суммирования п чисел и не реализует логических операций над входными переменными, а также не позволяет выполнять произвольные последовательности логических операций и операций суммирования над входными переменными. Это ограничивает область применения устройства, предназначенного для сложения нескольких чисел. Цель изобретения - расширение области применения путем реализации арифметической и логической обработки двоичных чисел. Поставленная цель достигается тем, что в устройстве для арифметической и логической обработки двоичных чисел, содержащее элементы И, каждый i-й разряд (з1,2, .,.,п) его содержит элементы ИЛИ и .Неравнозначность, два мультиплексора, управляющие входы которых попарно объединены и подключены к информационным входам устройства, информационные входы мультиплексоров являются управляющими входами уст ройства, выход первого мультиплексора соединен с первыми входами первого и второго элементов И и первого элемента Неравнозначность, второй вход которого соединен со вторым входом первого элемента И и выходом,третьего элемента И, входы которого попарно объединены со входами второго элемента Неравнозначность и подключены ко входам пе реноса устройства, выход второго элемента Неравнозначность соединен со

вторым входом второго элемента И, а также с первыми входами четвертого элемента И и третьего элемента Неравнозначность , вторые входы которых попарно объединены и подключены к выходу второго мультиплексора и третье входу второго элемента И, выход

которого соединен с третьим входом первого элемента Неравнозначность, выход которого соединен со входом первого элемента ИЛИ, другой вход которого соединен с выходом четвертого элемента И, входы второго элемента ИЛИ подключены к выходам первого и второго-элементов И, выходы первого и второго элементов ИЛИ являются выходами переноса устройства соответственно в i-Й и в (+1)-й разряды, а выход третьего элемента Неравнозначность является выходом результата устройства.

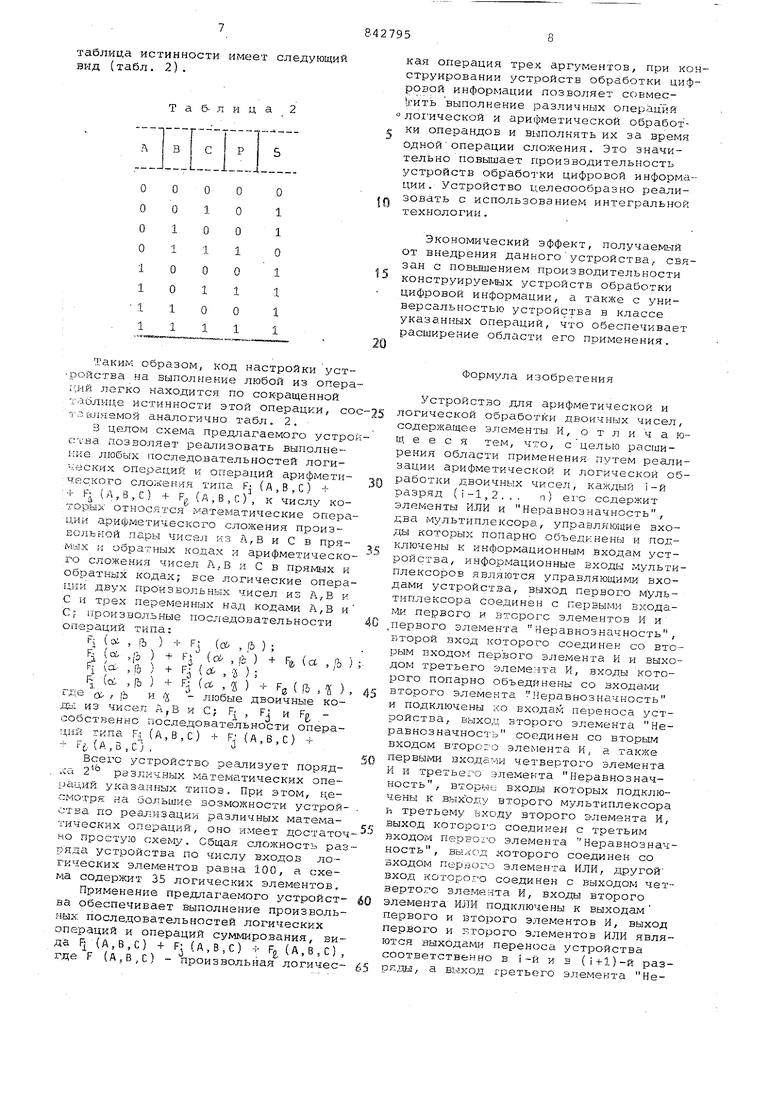

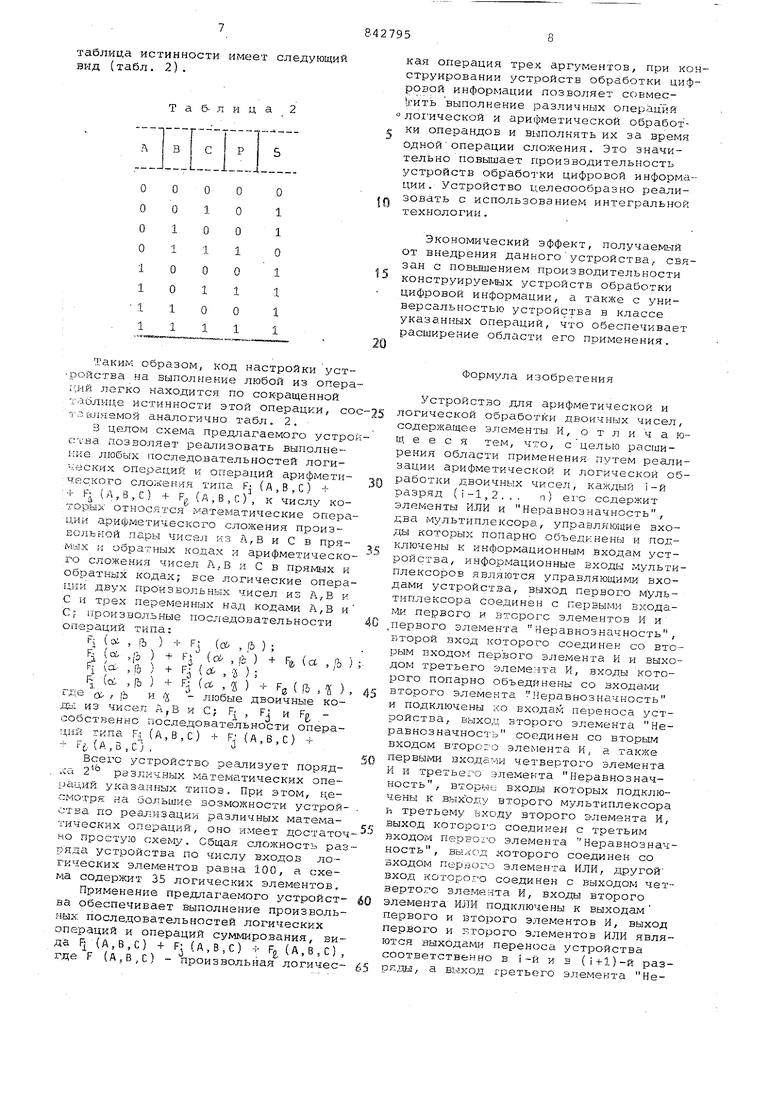

На фиг. 1 изобретена схема одного разряда устройства для арифметической и логической обработки трех двоичных чисел; на фиг. 2 - схема мультиплексора..

Устройство содержит мультиплексоры 1 и 2, логические элементы И 3-6, элементы 7-9 Неравнозначность, ИЛИ 10 и 11, информационные входы 12-14, два входа переноса 15 и 16, группы управляющих входов 17 и 18, выход 19 результата, два выхода 20 и 21 переноса j элементы И 22-29, элемент ИЛИ 30, элементы НЕ 31-33, управляющие входы 34-36, информационные входы 3744 и выход 45.

Управлякяцие входы мультиплексоров 1 и 2 попарно объединены и подключены к информационным входам 12-14 устройства, информационные входы мультиплексора 1 подключены к группе управлякхцих входов 17 устройства, а информационные входы мультиплексора 2 - к группе управляющих входов 18 устройства. Выход мультиплексора 1 соединен с первыми входами элементов И 3 и 4 и элемента 7 Неравнозначность. Второй вход .которого соединен со вторым входом элемента И 3 и с выходом элемента И 5, входы которого попарно объединены со входами элемента Неравнозначность 8 и подключены ко входам переноса 15 и 16 устройства. Выход элемента 8 соединен со вторым входом элемента И 4 и с первыми входами элементов .И 6 и Неравнозначность 9, вторые входы которых соединены с выходом мультиплексора 2 и с третьим входом элемента И 4, выход которого соединен с третьим входом элемента Неравнозначность 7. Входы элемента ИЛИ 10 подключены к выходам элементов 3 и 4, а элемента ИЛИ 11 - к выходам элементов 6 и 7. Выходы элементов ИЛИ 10 и 11 являются выходами переноса 21 и 20 устройства, а выход элемента Неравнозначность 9 является выходом результата устройства19 .

Устройство работает следующим .образом.

На информационные входы 12 - 14 устройства подаются одноименные разряды А, Bj и С|- операндов А, В и Ста на выходы 15 и 16. - сигналы пере-носа Р,;, и PI-I соответственно из (i-2) и {i-1) разрядов-устройства. С выхода 19 разряда устройства снимается сигнал S результата выполняемой математической операции, а с выходов 20 и 21 - сигналы P.J и Pj+i переносов в (i+1) и (i+2) разряды устройства соответственно. Настройка устройства на выполнение требуемой операции типа F| (А,В,с) + F,j (А,В,С) + + Fg (А,В,с) осуществляется с помощью сигналов настройки И - И и И(5 - И подаваемых на группы управляющих входов 17 и 18 мультиплексоров 1 и 2 соответственно.

РаЬота устройства рассматривается на примере выполнения любой из реализуемых операций, например, операции S (AVB) + (АД С) + С, таблица истинности для которой имеет следующий вид -(табл.. 1).

.Т а б л и ц а 1

и

Pt

I Продолжение табл. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для арифметической и логической обработки двоичных и двоично-десятичных @ -разрядных чисел | 1980 |

|

SU962922A1 |

| Устройство для арифметической и логической обработки двоичных чисел | 1981 |

|

SU983705A1 |

| Накапливающий сумматор | 1979 |

|

SU920708A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Многофункциональный запоминающий элемент для логической матрицы | 1983 |

|

SU1104584A1 |

| Многофункциональный элемент для логической матрицы | 1982 |

|

SU1037344A1 |

| Накапливающий сумматор | 1982 |

|

SU1166096A1 |

| Суммирующе-вычитающее устройство | 1977 |

|

SU667967A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| УСТРОЙСТВО ДЛЯ КОНВЕЙЕРНОГО СУММИРОВАНИЯ ЧИСЕЛ ПО ПРОИЗВОЛЬНОМУ МОДУЛЮ | 2023 |

|

RU2805939C1 |

Для выполнения устройством указанной математической операции мультиплексор 1 настраивается на реализацию логической функции сигнала Р таблицы истинности при Pj-i P-j., 0, а мультиплексор 2 - на реализацию логической функции Сигнала Si таблицы истинности при P. - следует из cxeNbi мультиплексора (фиг,2) для настройки мультиплексора на соответствующую логическую функцию трех аргументов достаточно двоинный код этой функции из таблицы истинности подать в ка.честве сигналов настройки на соответствующие входы мультиплексора, В устройстве для реализации в. мультиплексоре 1 логической функции сигнал необходимо двоичный код функции этого сигнала P.J 00010101 подать в. качестве сигналов И - Hg на группу управляющих входов 17 устройства. Соответственно код логической функции сигнала подается для настройки мультиплексора 2 в качестве управлякяцих сигналов Ид - И, .на группу управляющих входов 18 устройства. При Pj ® PIM выходе логического элемента Неравнозначность - 8 появляется сигнал 1, который инвертирует выходной сигнал и открывает элемент И б - в результате на выходах 19 и 20 устройства формируются сигналы Si и Р , соответствующие таблице истинности операции при комбинациях входных сигналов

0 переноса Р р и PJ.Q Р.

Кроме того, в этом случае при 1 формируется с помощью

РЛ

элемента И 4 выходной сигнал 1. При входных сигналах Pj.j 5 в устройстве происходит формирование с помощью элементов И 3 и 5, ИЛИ 10 сигнала Pj4 , соответствующего таблице истинности операции для данных

и Pi-, , а ТАНОзначений сигналов Р;

1-2

П же формирование сигналов Pj и Sj,

Аналогично устройство работает при выполнении любых других математических операций типа Fi(A,B,C) + + F. (А,В,С) + Fa(A,B,C). Для настрой5ки устройства на выполнение любой из операций указанного типа достаточно настроить.мультиплексоры 1 и 2 на реализацию логических функций сигналов Р и соответственно, получен0ных по таблице истинности операции при PJ.J Pj., i О , Эти функции легко получить по таблице истинности операции, составляемой без учета сигналов i-7 1 Например, для рассматривае5 мой операции -S (AV В) + () + С.

таблица истинности имеет следующий вид (табл. 2).

Т а б- л и ц а Таким образом, код настройки устройства на выполнение любой из операций легко находится по сокращенной таблице истинности этой операции, сос тавляемой аналогично табл. 2. В целом схема предлагаемого устрой ства позволяет реализовать выполнение любых последовательностей логических операций и операций арифметического сложения типа FJ (А, В, С) + + F(A,B,C) + Fg(A,B,C), к числу которых относятся математические операции арифметического сложения произвольной пары чисел из А,В и С в прямых и обратных кодах и арифметического сложения чисел А,В и С в прямых и обратных кодах; все логические операции двух произвольных чисел из А,В и С и трех переменных над кодами А,В и С; произвольные последовательности операций типа: Fi (oi. , fb ) + FJ (ot , (Ь ) ; (о. ,fb ) + F (c ,Ь } + Ft, (a ,/b FI ( ,lb ) + F|(C ,.й ); P (c6 ,/Ь ) + Fj (ct. , Й ) -H Fg (|Ъ Л ) где oi, , (Ь и /X любые двоичные коды ;ИЗ чисел и С; F.j , FJ и Fg собственно последовательности операций типа Fi (А , В , С ) + F: (А , В , С ) + + Fe, {А,В,С; . Всего устройство реализует порядка 2 различных математических операций указанных типов. При этом, цесмотря на большие возможности устройства по реализации различных математических операций, оно имеет достаточ но простую схему. Общая сложность раз ряда устройства по числу входов логических элементов равна 100, а схема содержит 35 логических элементов. Применение предлагаемого устройства обеспечивает выполнение произвольных последовательностей логических операций и операций суммирования, вида 1| (А,В,С) + F (А,В,С) + Fg (А,В,С) где F (А,В,с) - произвольная логичес

кая операция трех аргументов, при конструировании устройств обработки цифровой информации позволяет .совместить выполнение различных операцйй логической и арифметической обработки операндов и выполнять их за время одной операции сложения. Это значительно повышает производительность устройств обработки цифровой информации. Устройство целесообразно реали-зовать с использованием интегральной технологии.

Экономический эффект, получаемый от внедрения данногоустройства, связан с повышением производительности конструируемых устройств обработки цифровой информации, а также с универсальностью устройства в классе . указанных операций, что обеспечивает расширение области его применения. Формула изобретения Устройство для арифметической и логической обработки двоичных чисел, содержащее элементы И, отличающееся тем, что, сцелью расширения области применения путем реализации арифметической и логической обработки двоичных чисел, каждый 1-й разряд (i-1,2... п) eio содержит элементы ИЛИ и Неравнозначность, два мультиплексора, управляющие входы которых попарно объединены и подключены к информационным входам устройства, информационные входы мультиплексоров являются управляющими входами устройства, выход первого мультиплексора соединен с первыми входаМи первого и второго элементов И и первого элемента Неравнозначность, второй вход которого соединен со вторым входом первого элемента И и выходом третьего элементами, входы которого попарно объединены со входами второго элемента Неравнозначность и подключены ко входам переноса устройства, выход второго элемента Неравнозначность соединен со вторым входом второго элемента И, а также первыми входами четвертого элемента И и третьего элемента Неравнозначность, вторые входы которых подключены к выхЪду второго мультиплексора и третьему входу второго элемента И, выход которого соединен с третьим входом первого элемента Неравнозначность, выход которого соединен со входом первого элемента ИЛИ, другой вход которого соединен с выходом четвертого элемента И, входы второго элемента ИЛИ подключены к выходам первого и второго элементов И, выход первого и второго элементов ИЛИ являются выходами переноса устройства соответственно в i-й и в (4-1)-й разряды, а выход третьего элемента Неравнозначность является выходом результата устройства. Источники информации, принятые во внимание при экспертизе

i/,T(/g /jE

ФизЛ 1.Авторское свидетельство СССР № 275524, кл. G Об F 7/00, 1970. 2.Авторское свидетельство СССР 571809, кл. G 06 F 7/385, 1977 (прототип).

Авторы

Даты

1981-06-30—Публикация

1979-12-13—Подача