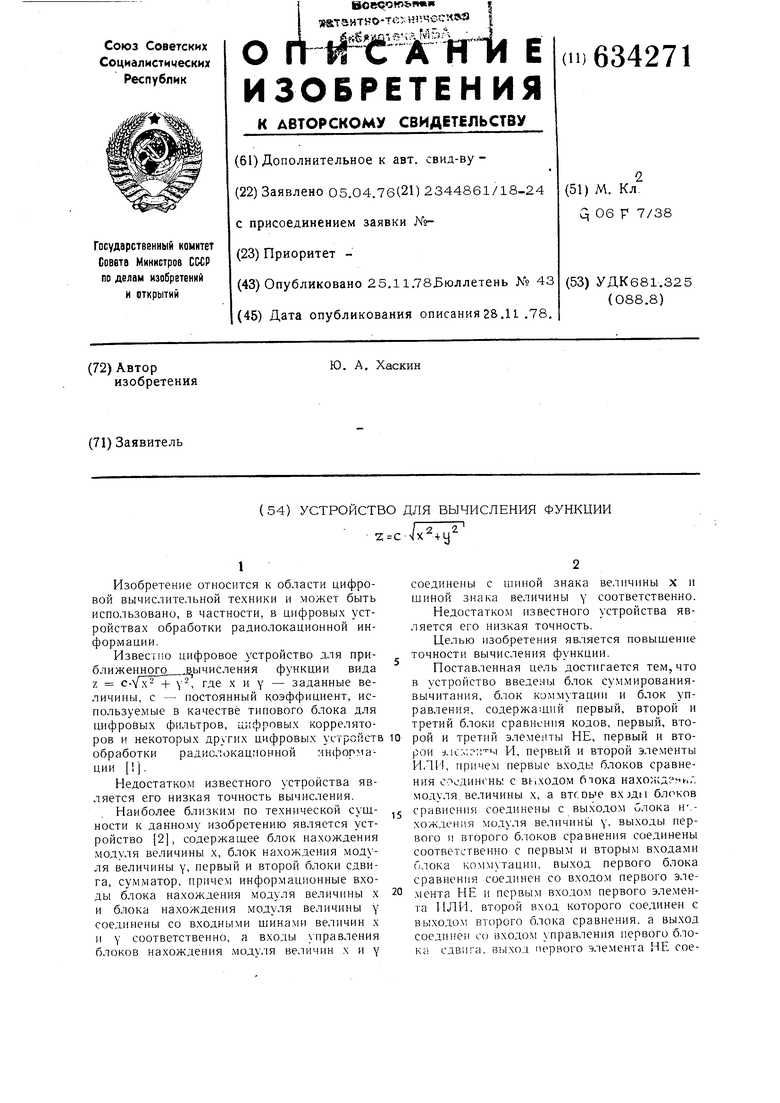

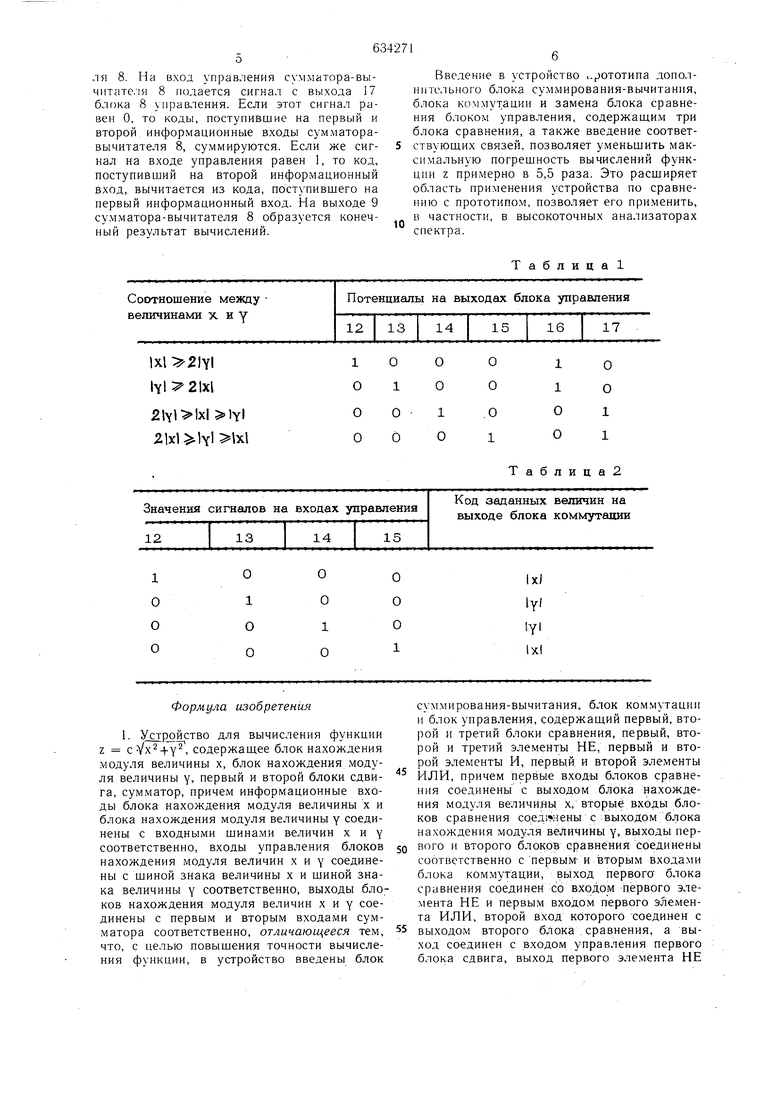

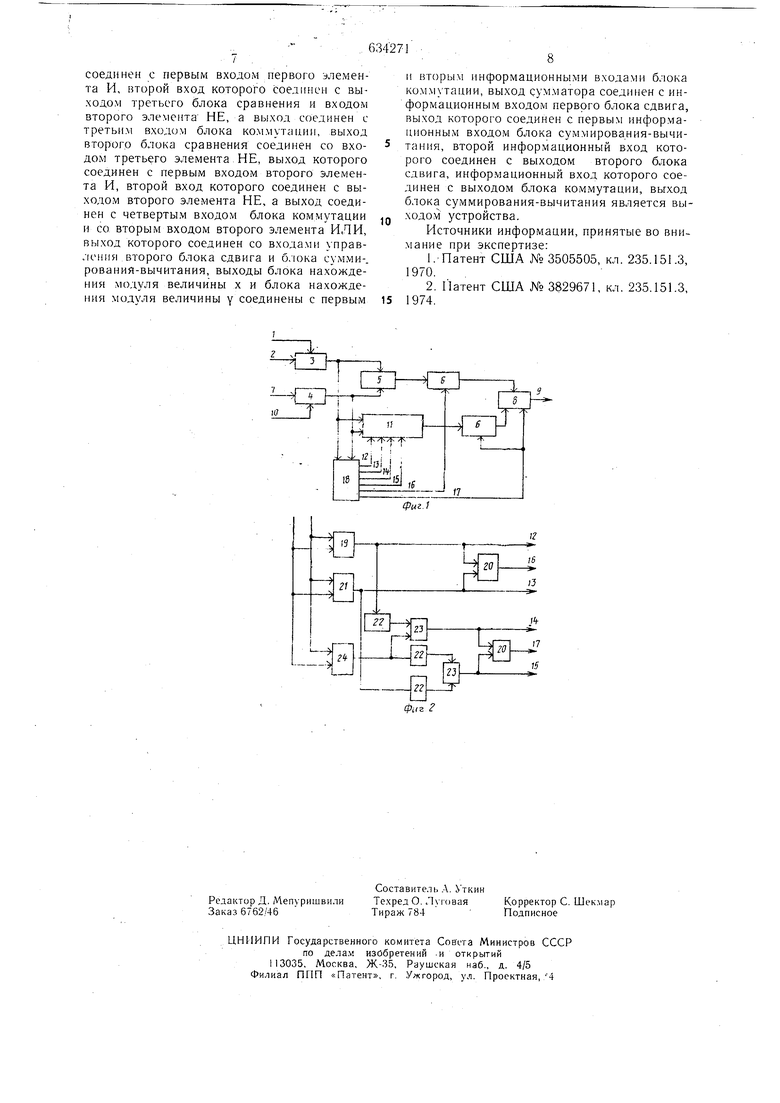

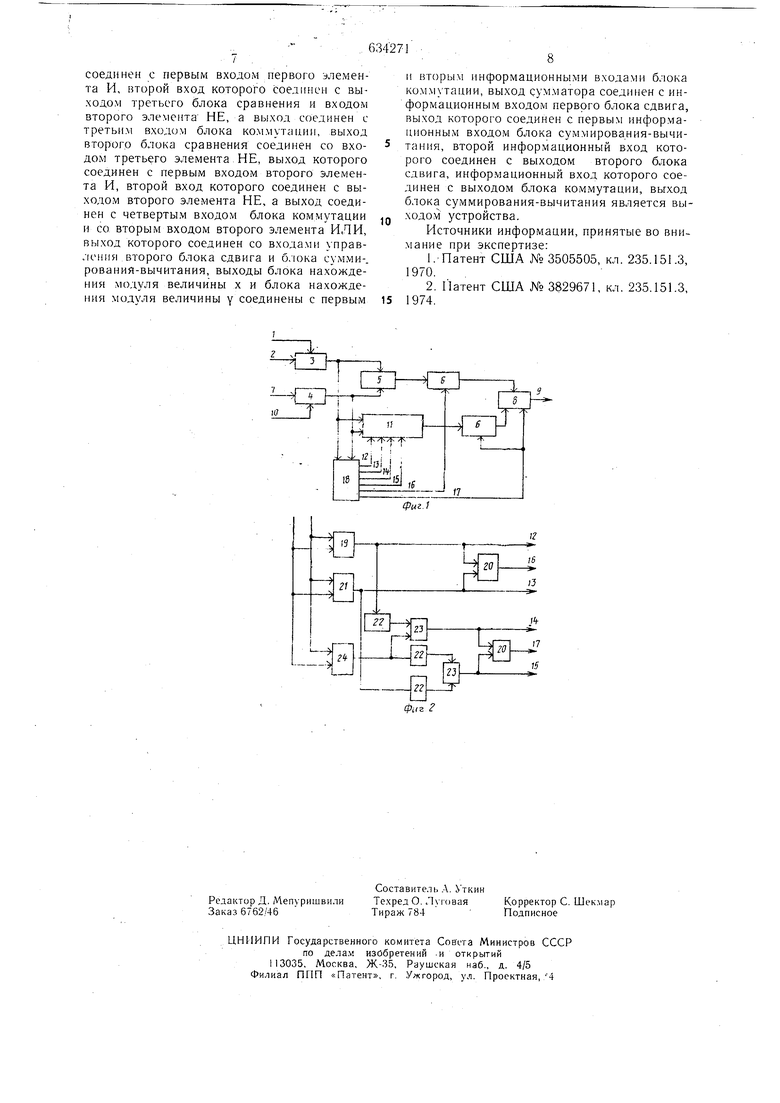

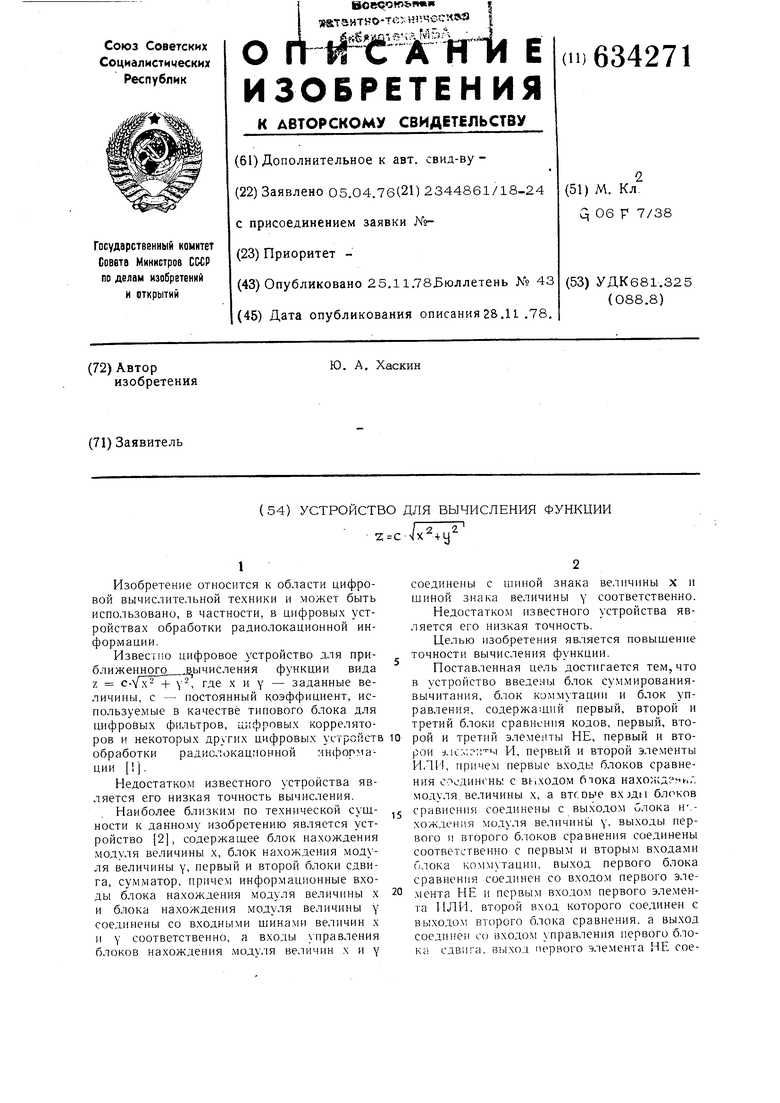

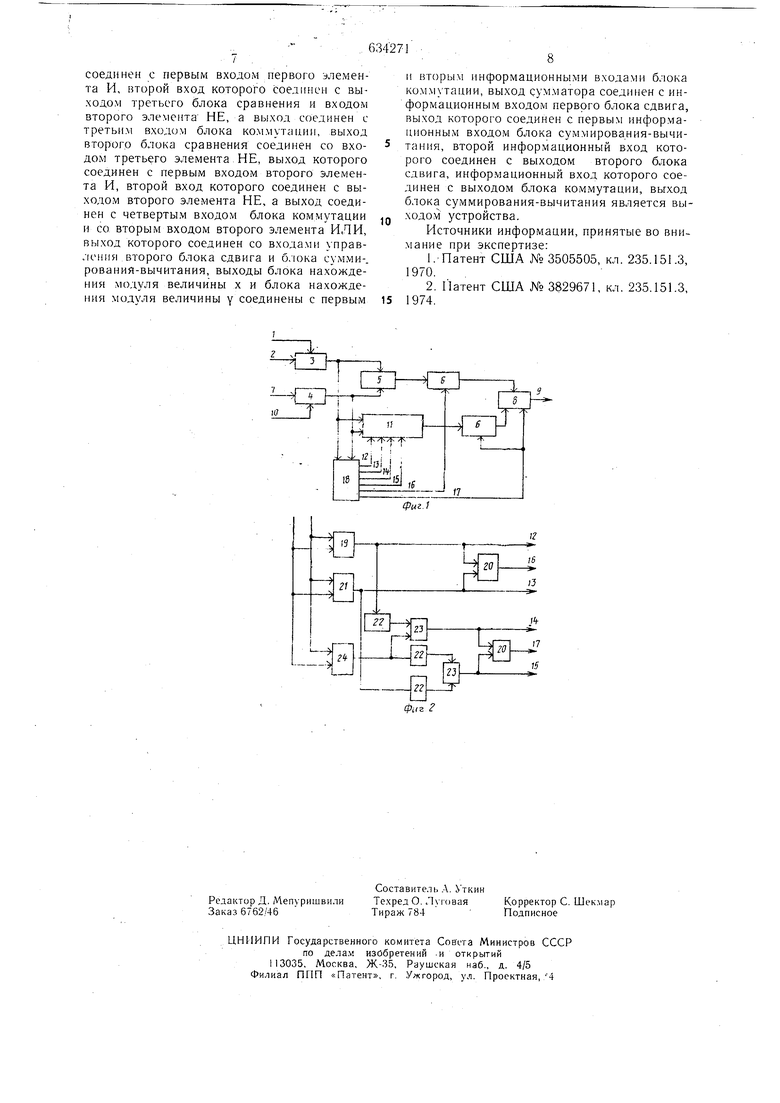

динсн с первым входом первого элемента И, второй вход которого соединен с выходом третьего блока сравнения и входом второго элемента НЕ, а выход соединен с третьим входом блока коммутации, выход второго блока сравнения соединен со входом третьего элемента НЕ, выход которого соединен с нервым входом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ, а выход соединен с четвертым входом блока коммутации и со вторым входом второго элемента ИЛИ, выход которого соединен со входами уцравления второго блока сдвига и блока суммирования-вычитания, выходы блока нахождениямодуля величины X и блока нахождения модуля величины у соединены с первым и вторым информационными входами блока коммутации, выход сумматора соединен с информационным входом первого блока сдвига, выход которого соединен с первым информационным входом блока суммированиявычитания, второй информационный вход которого соединен с выходом второго блока сдвига, информационный вход которого соединен с выходОдМ блока коммутации, выход блока суммирования-вычитания является выходом устройства. Схема устройства изображена на фиг. 1 и фиг. 2. Устройство содержит: шину 1 знака величины X, шину 2 кода величины х, блок 3 на.хождения модуля величины х, блок 4 нахождения модуля величины у сумматор 5, блоки 6 сдвига, шину 7 кода величины у. блок 8 суммирования-вычитания, шины 9 результата, шину 10 знака величины у блок 11 ко.ммутации, первый выход 12 блока управления, второй выход 13 блока управления, третий выход 14 блока унравления, .четвертый выход 15 блока управления, пятый выход 16 блока управления, шестой выход 17 блока управления, блок 18 управления, первый блок 19 сравнения, элементы 20 ИЛИ, второй блок 21 сравнения, элементы 22 НЕ, элементы 23 И, третий блок 24 сравнения. В устройстве используется следующий a;iгоритм:Zi 1x1 + lyl; z w asZi +|xl, если lxl 21yi; z ajzi +ly|, если lyj 2|yl; . -Ьз lyl, если 2ly| x |yl; x-xzi -bjlxl, если . Для реализации этих выражений достаточно иметь два блока сдвига и один блок ко.ммутации. При этом коэффициенты принимают значения: а 0,01, Ьз 0,01, с 0,313075, а наибольшая относительная ошибка сохраняет прежнее значение 1,79%. Работа устройства осуществляется следующим образом. На информационные входы блоков 3, 4 нахождения модуля величин х и у поступают многоразрядные коды величин х и , представленных в двоичном дополнительном коде. По отдельным шинам 1 и 10 на входы управления блоков 3 и 4 поступают знаковые разряды величин х и у. Если потенциал на шине знака соответствует знаку «Ч-, то код величины х и у пропускается блока.ми 3 и 4 без изменения; если же потенциал соответствует знаку «-, то код величины поразрядно инвертируется и к младшему разряду инвертированного кода добавляется единица. Полученный код появляется па выходных шинах блоков 3, 4. Схемно блоки 3 и 4 нахождения модуля быть выполнены, в частности, в виде сум.маторавычитателя. Полученные на выходах блоков 3 и 4 коды величин 1x1 и 1у1 поступают на входы сумматора 5, на выходе которого .образуется код функции z |х + 1у|. С выхода су.мматора 5 код функции-zi поступает на информационные входы первого блока 6 сдвига. Коды величин txl и |у1 также поступают в блок 8 управления. Блок 8 управления вырабатывает управляющие сигналы, соответствующие условиям выражений (2)ч-(5), на выходах , а также управляющий сигнал, соответствующий выполнению условия (2) или (3), на выходе 16 и управляющий сигнал, соответствхюшпй выполнению условия (4) или (5), на выходе 17. Для выработки этих сигналов используются три блока сравнения кодов; нерв1)1Й блок 19 сравнения сра1И1ивает код X и код 2 l; второй блок 21 сравнения сравнивает код у и код 2 х ; третий блок сравнения сравнивает код |х| и KO;I lyi. Порядок выработки сигналов на выходах 12- 17 иллюстрирует табл. 1. Сигналы с выходов 12-М7 блока 8 управления поступают на входы управления блока 11 коммутации. На первый и второй инфор.мационные входы блока 18 ком.мутации поступают соответственно коды х и у- Логика работы блока коммутации полностью описывается таблицей 2. С выхода блока 11 ком.мутации код поступает на второй блок 6 сдвига. Первый и второй блоки сдвига управляются сигна.чами с выходов 16 и 17 блока 18 управления. Если сигнал на входе управления блока 6 сдвига имеет значение О, то блок 6 сдвига пропускает код, поданный на его информационный вход, без изменения. Если же сигнал на входе управления имеет значение 1, то код на выходе блока 6 сдвига сдвинут по отнощению к коду на входе на два разряда в сторону уменьшения, что эквивалентно умножению входного кода на число 0,01. Схемная реализация блоков 6 сдвига, в частности, может быть такой же, как и в устройстве прототипа. Коды с выходов блоков 6 сдвига поступают на первый и второй информационные входы сумматора-вычитателя 8. На вход управления сумматора-вычитателя 8 подается сигнал с выхода 17 блока 8 управления. Если этот сигнал равеп О, то коды, поступившие на первый и второй, информационные входы сум.маторавычитателя 8, суммируются. Если же сигнал на входе управления равен 1, то код, поступивший на второй информационный вход, вычитается из кода, поступившего на первый информационный вход. На выходе 9 сумматора-вычитателя 8 образуется конечный результат вычислений.

Таблица Введение в устройство 1.рототипа дополнительного блока суммирования-вычитания, блока коммутации и замена блока сравнения блоком управления, содержаш,им три блока сравнения, а также введение соответствуюших связей, позволяет уменьшить максимальную погрешность вычислений функции Z примерно в 5,5 раза. Это расширяет область применения устройства по сравнению с прототипо.м, позволяет его при.менить, в частности, в высокоточных анализаторах спектра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня из суммы квадратов | 1981 |

|

SU1001094A1 |

| Устройство для алгебраического сложения чисел | 1983 |

|

SU1136148A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Декодер кода Рида-Маллера первого порядка по максимуму правдоподобия | 1990 |

|

SU1775857A1 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Устройство для алгебраического сложения чисел | 1986 |

|

SU1339552A1 |

| Устройство для извлечения квадратного корня из суммы квадратов | 1987 |

|

SU1425663A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Функциональный преобразователь | 1984 |

|

SU1211756A1 |

Значения сигналов на входах управления

О

о о

1 О

1 о

о

Формула изобретения

ооо10

1оо10

Таблица2

Код заданных величин на выходе блока коммутации

1x1

IY/

у1 1x1

суммирования-вычитания, блок коммутации и блок управления, содержащий первый, второй и третий блоки сравнения, первый, второй и третий элементы НЕ, первый и второй элементы И, первый и второй элементы

ИЛИ, причем первые входы блоков сравнения соединены с выходом блока нахождения модуля величины х, вторые входы блоков сравнения соед1«нены с выходом блока нахождения модуля величины у, выходы первого и второго блоков сравнения соединены соответственно с первым-и вторым входами блока коммутации, выход первого блока сравнения соединен со входом первого элемента НЕ и первым входом первого элемента ИЛИ, второй вход которого соединен с

выходом второго блока сравнения, а выход соединен с входом управления первого блока сдвига, выход первого элемента НЕ

соединен с первым входом первого элемента И, 5торой вход которого соединен с выходом третьего блока сравнения и входом второго элемента НЕ, а выход соединен с третьим входом блока коммутации, выход второго блока сравнения соединен со входом третьего элемента, НЕ, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с выходом второго элемента НЕ, а выход соединен с четвертым входом блока коммутации и со вторым входом второго элемента ИЛИ, выход которого соединен со входами управления второго блока сдвига и блока сумми-. рования-вычитания, выходы блока нахождения модуля величины х и блока нахождения модуля величины у соединены с первым

II вторым информационными входами блока коммутации, выход сумматора соединен с информационным входом первого блока сдвига, выход которого соединен с первым информационным входом блока суммирования-вычитания, второй информационный вход которого соединен с выходом второго блока сдвига, информационный вход которого соединен с выходом блока коммутации, выход блока суммирования-вычитания является выходом устройства.

Источники информации, принятые во внимание при экспертизе:

Авторы

Даты

1978-11-25—Публикация

1976-04-05—Подача