Изобретение относится к вычисли- те льной технике, в частности к ьа- поминающим устройствам, и может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении.

Цель изобретения - повышение достоверности контроля схем коррекции ошибок и повышение быстродействия, устройства в режиме самоконтроля.

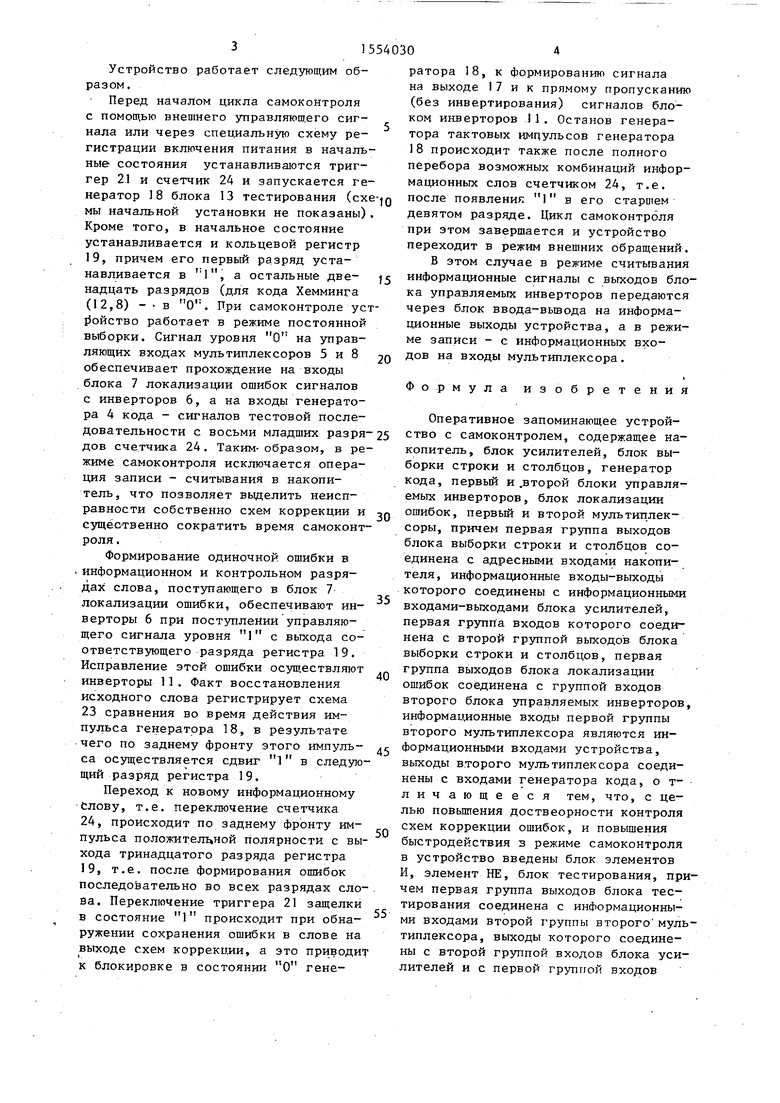

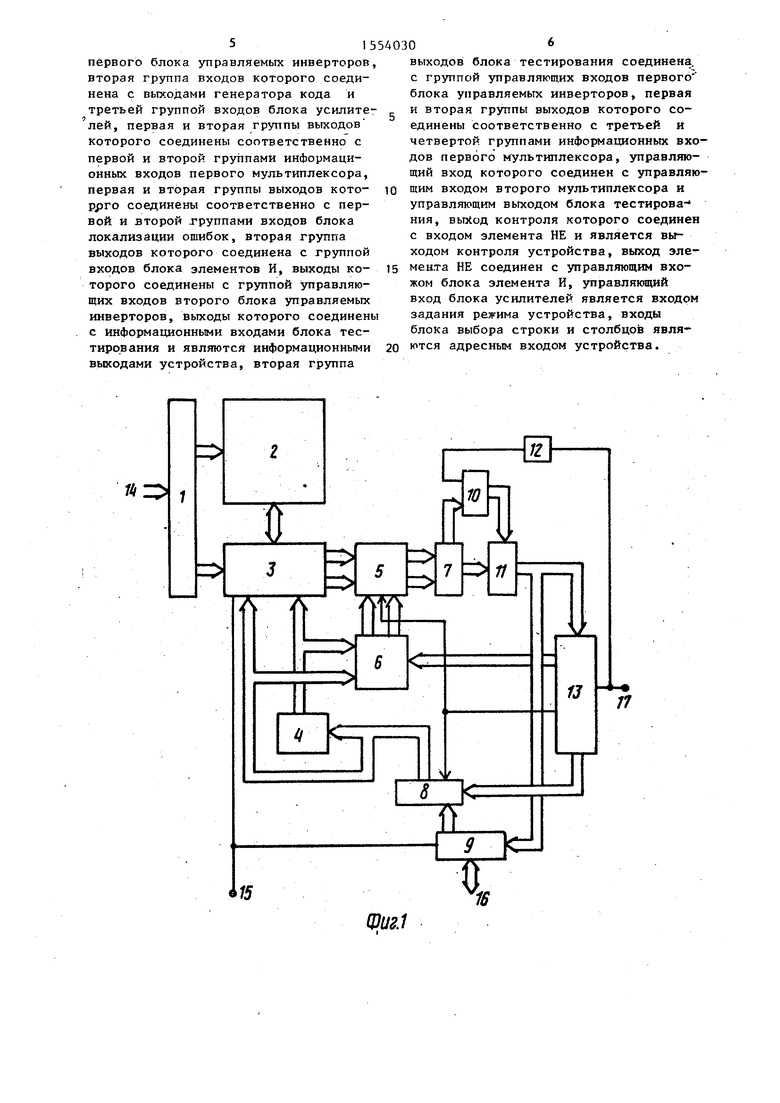

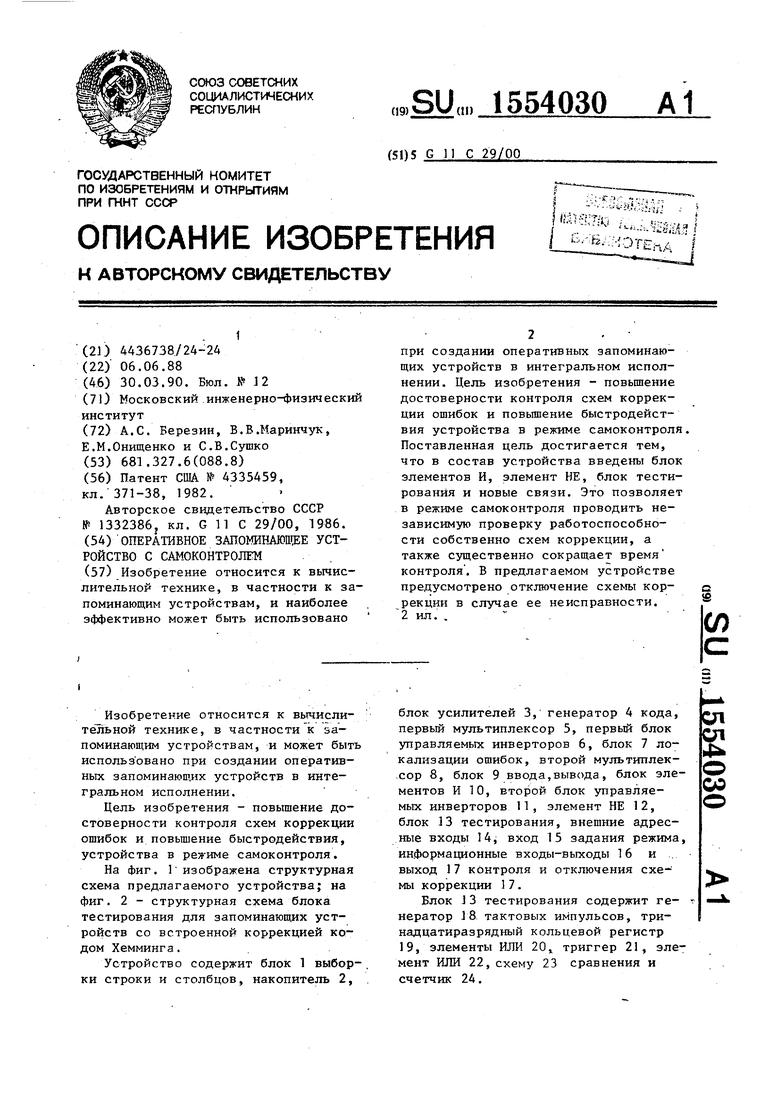

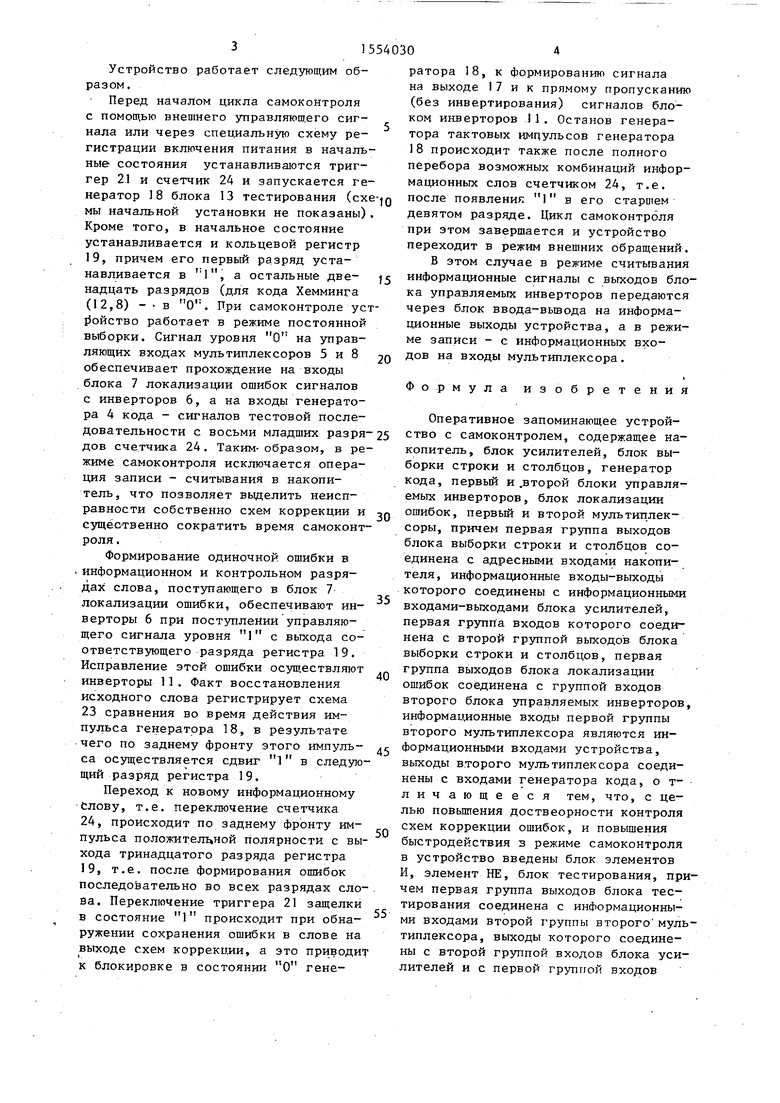

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2 - структурная схема блока тестирования для запоминающих устройств со встроенной коррекцией кодом Хемминга.

Устройство содержит блок 1 выборки строки и столбцов, накопитель 2,

блок усилителей 3, генератор 4 кода, первый мультиплексор 5, первый блок управляемых инверторов 6, блок 7 локализации ошибок, второй мультиплексор 8, блок 9 ввода,вывода, блок элементов И 10, второй блок управляемых инверторов 11, элемент НЕ 12, блок 13 тестирования, внешние адресные входы 14, вход 15 задания режима, информационные входы-выходы 16 и выход 17 контроля и отключения схемы коррекции 17.

Блок 13 тестирования содержит ге- нератор 18 тактовых импульсов, тринадцатиразрядный кольцевой регистр 19, элементы ИЛИ 20х триггер 21, элемент ИЛИ 22, схему 23 сравнения и счетчик 24.

сл

S

о

GO

20

Устройство работает следующим обазом.

Перед началом цикла самоконтроля помощью внешнего управляющего сигала или через специальную схему реистрации включения питания в начальые состояния устанавливаются триггер 21 и счетчик 24 и запускается геератор 18 блока 13 тестирования (cxe-jQ после появления ы начальной установки не показаны). девятом разряде роме того, в начальное состояние устанавливается и кольцевой регистр 19, причем его первый разряд устанавливается в , а остальные две- щ надцать разрядов (для кода Хемминга (12,8) - в О. При самоконтроле устройство работает в режиме постоянной ыборки. Сигнал уровня О на управяющих входах мультиплексоров 5 и 8 обеспечивает прохождение на входы блока 7 локализации ошибок сигналов с инверторов 6, а на входы генератора 4 кода - сигналов тестовой послеовательности с восьми младших разря 25 ов счетчика 24. Таким- образом, в режиме самоконтроля исключается операция записи - считывания в накопитель, что позволяет выделить неисправности собственно схем коррекции и п существенно сократить время самоконтроля.

Формирование одиночной ошибки в информационном и контрольном разрядах слова, поступающего в блок 7 локализации ошибки, обеспечивают инверторы 6 при поступлении управляющего сигнала уровня 1 с выхода соответствующего разряда регистра 19. Исправление этой ошибки осуществляют инверторы 11. Факт восстановления исходного слова регистрирует схема 23 сравнения во время действия импульса генератора 18, в результате чего по заднему фронту этого импулъратора 18, к фо на выходе 17 и к (без инвертирова ком инверторов тора тактовых им 18 происходит т перебора возможн мационных слов с при этом заверша переходит в реж В этом случа информационные ка управляемых через блок ввод ционные выходы ме записи - с и дов на входы мул

Формула и

35

40

са осуществляется сдвиг 1 в следующий разряд регистра 19.

Переход к новому информационному Слову, т.е. переключение счетчика 24, происходит по заднему фронту импульса положительной полярности с выхода тринадцатого разряда регистра 19, т.е. после формирования ошибок последовательно во всех разрядах слова. Переключение триггера 21 защелки в состояние 1 происходит при обнаружении сохранения ошибки в слове на выходе схем коррекции, а это приводит к блокировке в состоянии О гене45

50

55

Оперативное ство с самоконт копитель, блок у борки строки и с кода, первый и .в емых инверторов ошибок, первый и соры, причем пе блока выборки с единена с адрес теля, информаци которого соедин входами-выходами первая группа вх нена с второй г выборки строки группа выходов ошибок соединен второго блока уп информационные в второго мультипл формационными в выходы второго м нены с входами г личающее лью повышения д схем коррекции быстродействия в устройство вв И, элемент НЕ, чем первая груп тирования соеди ми входами втор типлексора, вых ны с второй груп лителей и с перв

после появления девятом разряде

ратора 18, к формированию сигнала на выходе 17 и к прямому пропусканию (без инвертирования) сигналов блоком инверторов 11. Останов генератора тактовых импульсов генератора 18 происходит также после полного перебора возможных комбинаций информационных слов счетчиком 24, т.е. 1 в его старшем Цикл самоконтроля при этом завершается и устройство переходит в режим внешних обращений. В этом случае в режиме считывания информационные сигналы с выходов блока управляемых инверторов передаются через блок ввода-вывода на информационные выходы устройства, а в режиме записи - с информационных входов на входы мультиплексора.

после появления девятом разряде

Формула изобретения

Q после появления девятом разряде 5п

5

0

45

50

5

Оперативное запоминающее устройство с самоконтролем, содержащее накопитель, блок усилителей, блок выборки строки и столбцов, генератор кода, первый и .второй блоки управляемых инверторов, блок локализации ошибок, первый и второй мультиплексоры, причем первая группа выходов блока выборки строки и столбцов соединена с адресными входами накопителя, информационные входы-выходы которого соединены с информационными входами-выходами блока усилителей, первая группа входов которого соединена с второй группой выходов блока выборки строки и столбцов, первая группа выходов блока локализации ошибок соединена с группой входов второго блока управляемых инверторов, информационные входы первой группы второго мультиплексора являются информационными входами устройства, выходы второго мультиплексора соединены с входами генератора кода, о т- личающееся тем, что, с целью повышения доствеорности контроля схем коррекции ошибок, и повышения быстродействия з режиме самоконтроля в устройство введены блок элементов И, элемент НЕ, блок тестирования, причем первая группа выходов блока тестирования соединена с информационными входами второй группы второго1 мультиплексора, выходы которого соединены с второй группой входов блока усилителей и с первой группой входов

первого блока управляемых инверторов вторая группа входов которого соединена с выходами генератора кода и третьей группой входов блока усилите лей, первая и вторая группы выходов которого соединены соответственно с первой и второй группами информационных входов первого мультиплексора, первая и вторая группы выходов кото- ррго соединены соответственно с первой и второй труппами входов блока локализации ошибок, вторая группа выходов которого соединена с группой входов блока элементов И, выходы ко- торого соединены с группой управляющих входов второго блока управляемых инверторов, выходы которого соединен с информационными входами блока тестирования и являются информационными выходами устройства, вторая группа

выходов блока тестирования соединена. с группой управляющих входов первого блока управляемых инверторов, первая и вторая группы выходов которого соединены соответственно с третьей и четвертой группами информационных входов первого мультиплексора, управляющий вход которого соединен с управляющим входом второго мультиплексора и управляющим выходом блока тестирова- ния, выход контроля которого соединен с входом элемента НЕ и является выходом контроля устройства, выход элемента НЕ соединен с управляющим вхо- жом блока элемента И, управляющий вход блока усилителей является входом задания режима устройства, входы блока выбора строки и столбцов являются адресным входом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1566414A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1287240A1 |

| Оперативное запоминающее устройство с коррекцией ошибок и резервированием | 1989 |

|

SU1709397A1 |

| Устройство для контроля оперативной памяти | 1989 |

|

SU1705875A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1988 |

|

SU1644233A1 |

| Устройство для сопряжения вычислительной машины с устройством ввода изображения | 1985 |

|

SU1260967A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и наиболее эффективно может быть использовано при создании оперативных запоминающих устройств в интегральном исполнении. Цель изобретения - повышение достоверности контроля схем коррекции ошибок и повышение быстродействия устройства в режиме самоконтроля. Поставленная цель достигается тем, что в состав устройства введены блок элементов И, элемент НЕ, блок тестирования и новые связи. Это позволяет в режиме самоконтроля проводить независимую проверку работоспособности собственно схем коррекции, а также существенно сокращает время контроля. В предлагаемом устройстве предусмотрено отключение схемы коррекции в случае ее неисправности. 2 ил.

/4

Фиг.1

1В

21

12,П

Редактор А. Ревин

Составитель В. Чеботова

Техред М.Ходанич Корректор Т.Палий

Заказ 460

Тираж 484

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Ц

19

4 t

22

23

2Ь

тт .

И 8

Фив. 2

Подписное

| Патент США № 4335459, кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-03-30—Публикация

1988-06-06—Подача