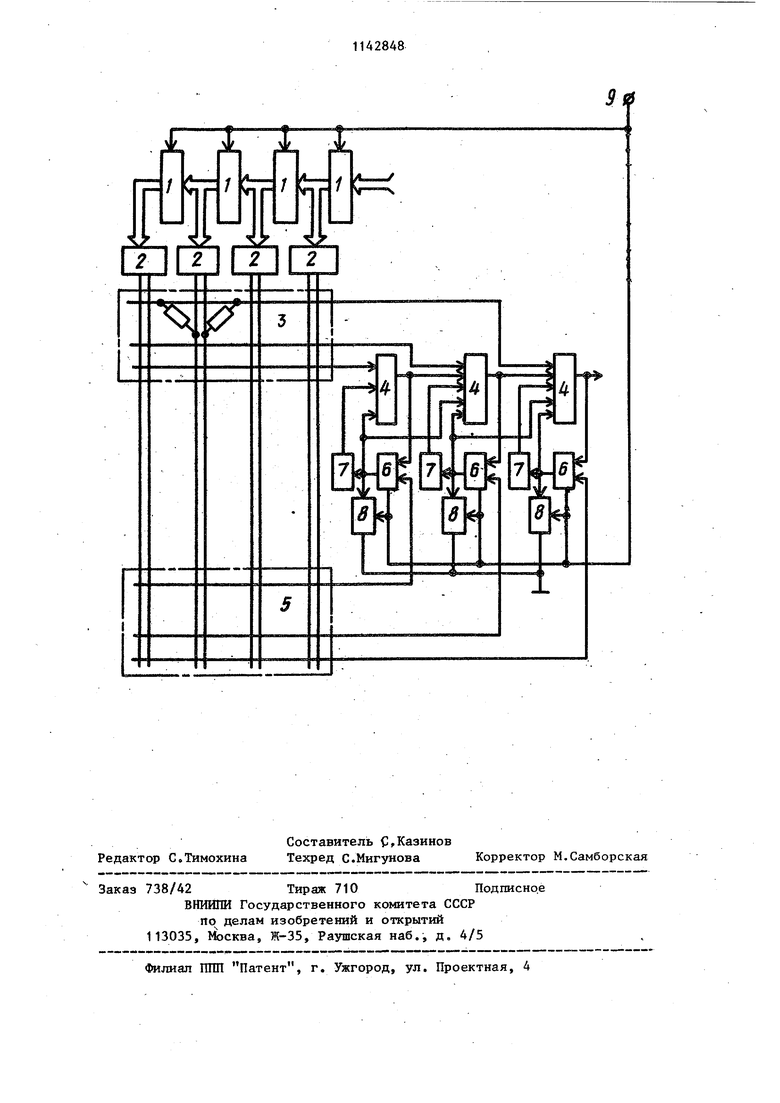

Изобретение относится к автома,тике и вычислительной технике и может быть использовано для восстановления формы сигналов, заданных своими значениями в дискретные моменты времени. Известен интерполятор, содержащий блок нелинейной интерполяции, коммутатор-и фильтр нижних частот 1, Недостатком этого интерполятора является сложность технической реал зации при повышенных требованиях к точности интерполяции. Известен также интерполятор, содержащий сумматоры, инте.граторы, аналоговые запоминакщиё элементы и ключи Г21. Недостатками данного интерполято ра являются пониженная точность интерполяции. Наиболее близким к изобретению является интерполятор, содержащий (п + 1) регистров (тде п - степень интерполирующего полинома), п суммирукяцих интеграторов, п усилителей слежения-хранения и (п+1) цифроаналоговых преобразователей, подключен ных прямыми и инверсными выходами к входам двух матриц весовых резисторов, выходы первой из которых соединены с первыми входами суммирующих интеграторов, а выходы второй матрицы весовых резисторов подключе ны к первым информационным входам усилителей слежения-хранения, соеди ненных управляняцими входами с шиной тактовых импульсов, причем каждьй i-й (1 i i t п ) усилитель слеженияхранемия подалючен выходом к второму входу 1-го и третьему входу (i + 1)-ro сзгммирующих интеграторов, а вторым информационным входом - к выходу 1-го и четвертому входу (1+1)-го суммирующих интеграторов, причем выход i-ro суммирующего интегратора соединен с выходом интерполятора, информационный вход перво го регистра подключён к входу интер полятора, выход каждого 1-го (1 i fi + 1) регистра соединен с информационным входом (i+1)-ro регистра и входом -i-ro цифроаналого вого преобразователя, а входы управ ления записью регистров подключены к выходу элемента задержки, соедине ного входом с шиной тактовых импуль сов Сз 3. 8 Недостатком известного устройства является пониженная точность интерполяции из-за неполной компенсации знакопостоянных погрешностей. Кроме того, быстродействие интерполяции ограничено влиянием конечной величины длительности тактовых импульсов на работу импульсной коррекции. Целью изобретения является повышение точности и быстродействия интерполятора , Поставленная цель достигается тем, что в интерполятор, содержащий (п+1) регистров (где п- степень интерполирукщего полинома), п суммирующих интеграторов, п усилителей слежения-хранения и (п+1) цифроаналоговых преобразователей, подкпюченных прямыми и инверсными выходами к входам двух матриц весовых резисторов, выходы первой из которьк соединены с первыми входами суммирующих интеграторов, а выходы второй матрицы весовых резисторов подключены к первым информационным входам усилителей слежения-хранения, соеди ненньк управляющими входами с шиной тактовых импульсов, причем каждьй i-й (1i i 6 n ) усилитель слеженияхранения подключен выходом к второму входу i-ro и третьему входу (i+1)-ro суммирующих интеграторов, а вторым информационным входом - к выходу i-ro и четвертому входу (+1)-го суммирумцих интеграторов, причем выход п-го суммирующего интегратора соединен с выходом интерполятора, информационный вход первого регистра подключен к входу интерполятора, а выход каждого i-ro (1 1 п+ 1) регистра соединен с информационным входом (i +1)-го регистра и входом -то цифроаналогового преобразователя, дополнительно введены п интеграторов и п ключей, соединенных управляющими входами с шиной тактовых импульсов и входами управления записью регистров, а выходами - с общей шиной интерполя7 тора, причем выход каждого i-rq усилителя слежения-хранения подключен к к сигнальному входу i-ro дополнительного ключа и входу i-ro дополнительного интегратора, соединенного выходом с дополнительным входом -го суг-тирукщего интегратора. На чертеже схематически изображены (для случая ) регистры 1,

цифроаналоговые преобразователи 2, первую матрицу 3 весовых резисторов суммирующие интеграторы 4, входную матрицу 5 весовых резисторов, усилители 6 слежения-хранения, дополнительные интеграторы 7 и ключи 8, а также шину 9 тактовых импульсов.

Устройство работает следующим образом.

Каждый такт инициируется подачей на шину 9 тактового импульса, по заднему фронту которого происходит передача информации в цепочке регистра 1 от каждого правого к левому (по блок-схеме) регистру. Информация из крайнего левого регистра 1 теряется, а в крайний правый регистр 1 поступает цифровой код новой выборки, Цифроанапоговые преобразователи 2 преобразуют цифровые коды в аналоговз о форму и передают напряжения на входы матриц 3 и 5 весовых резисторов, матрица 3 резисторов вычисляет значения, равные

разности между производными интер. полирующего полинома в начале участка интерполяции и ожидаемыми значениями напряжений, которые должны быть накойлены интеграторами 4 к концу предьщущего такта работы. Эти значения в виде токов поступают на токовые входы суммирующих интеграторов 4 (остальные входы сз ммирующего интегратора соединень с токовым входом через весовые резисторы). На выходе м-го суммирующего интегратора 4 в течение длительности такта работы формируется выбранньш участок Он выбирается в середине интерполирующей функции, поэтому выходная функция формируется из средних наиболее точных участков интерполирующего полинома.

Матрица 5 резисторов вычисляет ожидаемые значения напряжений на выходах суммирующих интеграторов 4 к концу текущего такта работы. Эти ожидаемые значения в виде токов Поступают на первые (токовые) входы усилителей 6 .слежения-хранения, на

вторые (вычитающие) входы которых поступают фактические напряжения с выходов интеграторов 4, Разность этих значений к концу такта работы должна быть равна нулю, но из-за влияния различных случайных факторов таких как дрейф нуля интеграторов неточность подбора элементов, воздействия помех и тому подобное, эта разность может отличаться от нуля, Под действием следующего тактового импульса, которьй приходит в конце каждого такта работы, напряжение ошибки запоминается в аналоговой форме усилителем 6 слежения-хранения и в противофазе подается на вход суммирующего интегратора 4, Благодаря этому в следующем такте происходит исправление ошибки. Если на входе одного из интеграторов 4 появляется знакопостоянная погрешность, усредненное значение которой за несколько периодов работы отлично от нуля, то через время, равное постоянной интегрирования интегратора 7,. на его выходе появляется интегральное значение этой ош1бки, которое с выхода интегратора 7 поступает в противофазе на вход суммирующего интегратора 4, где происходит полная компенсация такого вида ошибок.

На время действия тактового импульса ключи 8 замыкаются и блокируют выходные напряжения усилителей 6 слежения-хранения, Благодаря этому можно расширить длительность тактового импульса, не опасаясь помех на входах сзгммирующих интеграторов 4 от переходных процессов в усилителях 6 слежения-хранения, или (что то же самое) при неизменной длительности тактовых импульсов увеличить частоту их поступления.

Таким образом, за .счет введения интеграторов 7 и ключей 8 достигается повышение быстродействия и точности интерполяции по сравнению с прототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Интерполятор | 1981 |

|

SU987634A1 |

| Интерполятор | 1986 |

|

SU1334167A1 |

| Полиномиальный интерполятор | 1988 |

|

SU1522245A1 |

| Нелинейный интерполятор | 1985 |

|

SU1267446A1 |

| Функциональный преобразователь | 1980 |

|

SU879603A1 |

| Линейный интерполятор | 1989 |

|

SU1659986A1 |

| Интерполятор | 1986 |

|

SU1396140A1 |

| Устройство для двухкоординатного программного управления | 1981 |

|

SU962857A1 |

| Линейный интерполятор | 1986 |

|

SU1423984A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

ИНТЕРПОЛЯТОР, содержащий П+1 регистров (где п- степень интерпопирунщего полинома), п суммирующих интегратсфов, «усилителей слежения-хранения и цифроанапоговых преобразователей, подключенных прямыми и инверсными выходами к входам двух матриц весовых резисторов, выходы первой из которых соединены с, первыми входами суммирующих интеграторов, а выходы второй матрицы весовых резисторов подключены к первым информационным входам усилителей слежения-хранения, соединенных управляющими входами с шиной тактовых импульсов, причем каждый i-й

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроизмерительное устройство для определения полей давлений | 1980 |

|

SU877372A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-02-28—Публикация

1983-11-28—Подача