№г

7V

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Оперативное запоминающее устройство | 1980 |

|

SU959166A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Буферное запоминающее устройство | 1986 |

|

SU1363308A1 |

| Оперативное запоминающее устройство | 1990 |

|

SU1751812A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

Изобретение относится к вычислительной технике, в частности к запо- минвнщим устройствам, и может быть использовано в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти. Целью изобретения является расширение области применения .устройства за счет обеспечения одновременного чтения по

i (Л

произволь гюму числу несовпадающих адресов и гювь шение быстродеми твия устройства в режиме чтения. Устройство содержит регистры 1,1, адреса, блок 2 коммутации адресов, блок 3 анализа адресов, блок 4 сброса обслуженных запросов, дешифраторы , адреса, формирователи адресных сигналов, накопители 7,-7„, усилители 8,- 8„ чтения, формирователи 9(-9 информационных сигнапов, комгтутатор 10 считанных данных, коммутатор 11 записываемых данньгк, регистры 12,-12 слова, адресные входы 13,-П,, информационные выходы 14(-14„, информаци1432606

онные входы 15 (-15, и входы обращения. Устройство работает в режиме записи информационных слов, чтения одновременно по произвольному числу поступающих по п каналам как несовпадающих, так и совпадающих адресов, а также в режиме одновременной обработки обращений для записи и чтения, поступающих по разным п каналам. Во всех режимах обработки обраг ений происходит в соответствии с приоритетом: запрос, поступающий по каналу с меньшим номером, имеет больший приоритет при обращении к одному накопителю 7. 3 з.п. ф-лы, 6 ил.

1

Изобретение относится к вычислительной технике, в частности к з апо- минающим устройствам, и может быть использовано в многопроцессорных и многомашинных вычислительных системах в качестве общей оперативной памяти

Цель изобретения - расширение области применения устройства путем обеспечения одновременного чтения по произвольному числу несовпадающих адресов и повышение быстродействия в режиме чтения.

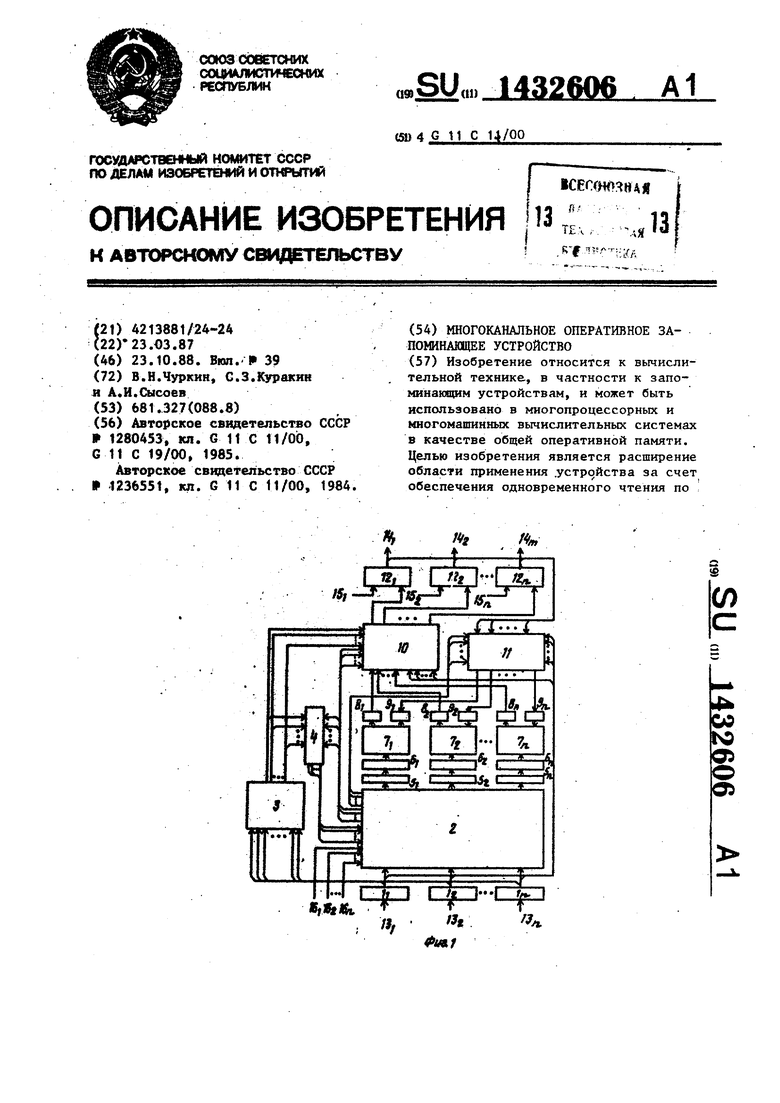

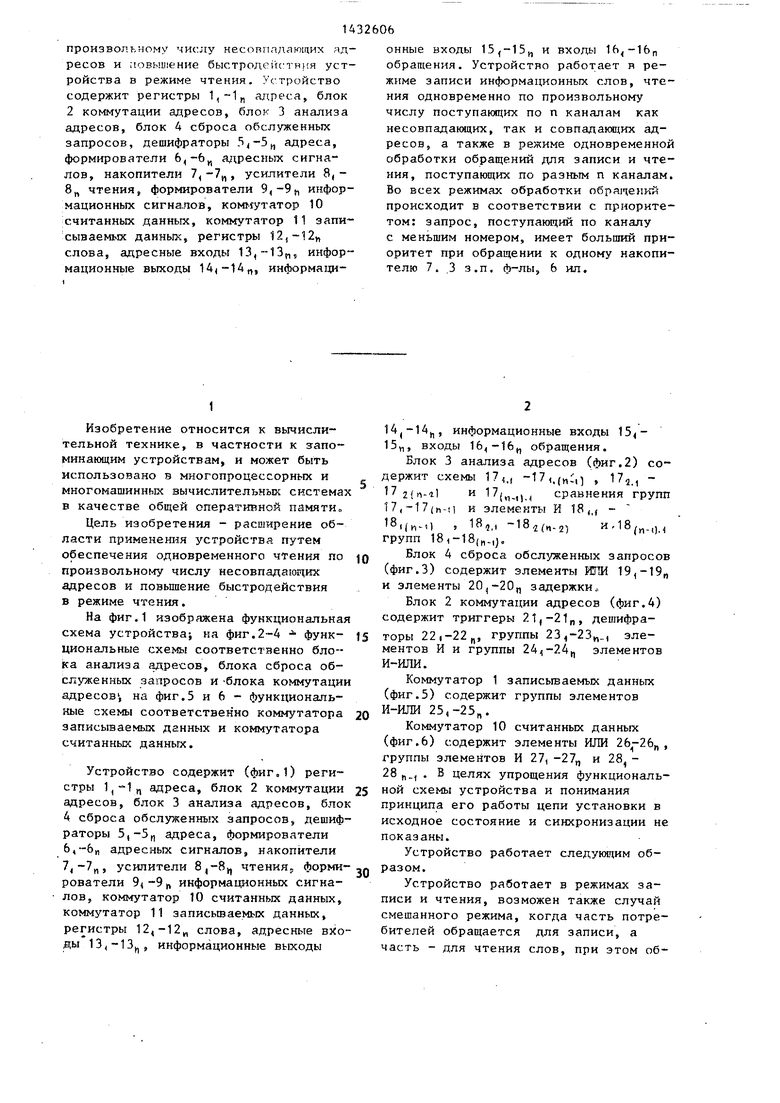

На фиг.1 изображена функциональная схема устройства; на фиг.2-4 - функ- циональные схемы соответственно блока анализа адресов, блока сброса обслуженных запросов и -блока коммутации адресов , на фиг.5 и 6 - функциональные схемы соответственно коммутатора записываемых данных и коммутатора считанных данных.

Устройство содержит {фиг,1) регистры 1,1ц адреса, блок 2 коммутации адресов, блок 3 анализа адресов, блок 4 сброса обслуженных запросов, дешифраторы 5,-5 адреса, формирователи 6,-6и адресных сигналов, накопители , усилители 8,-8„ чтенияр форми- рователи информационных сигналов, коммутатор 10 считанных данных, коммутатор 11 записьгоаемых данных, регистры 12,-12„ слова, адресньте входы 134-13,,, информационные выходы

S

0

5 0

5 Q

,, информационные входы 15у|, входы , обращения.

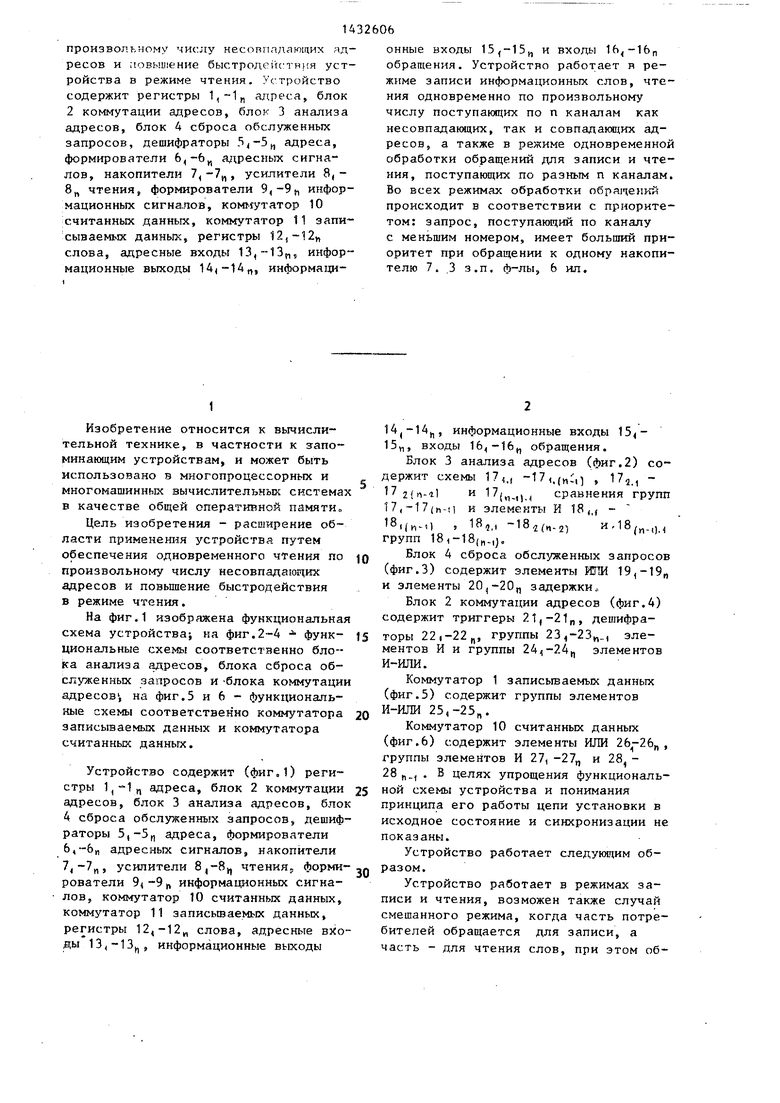

Блок 3 анализа адресов (фиг.2) содержит схемы 174., -t7,.(rt;, , 17,2,,

17 2{п-а) И 17

{и-1).4 сравнения групп

t7,-17(i-si и элементы И 18,,, 18,(.,) , 18,,, -18(„.2 и,18.,,

групп 18,-18(.,j,

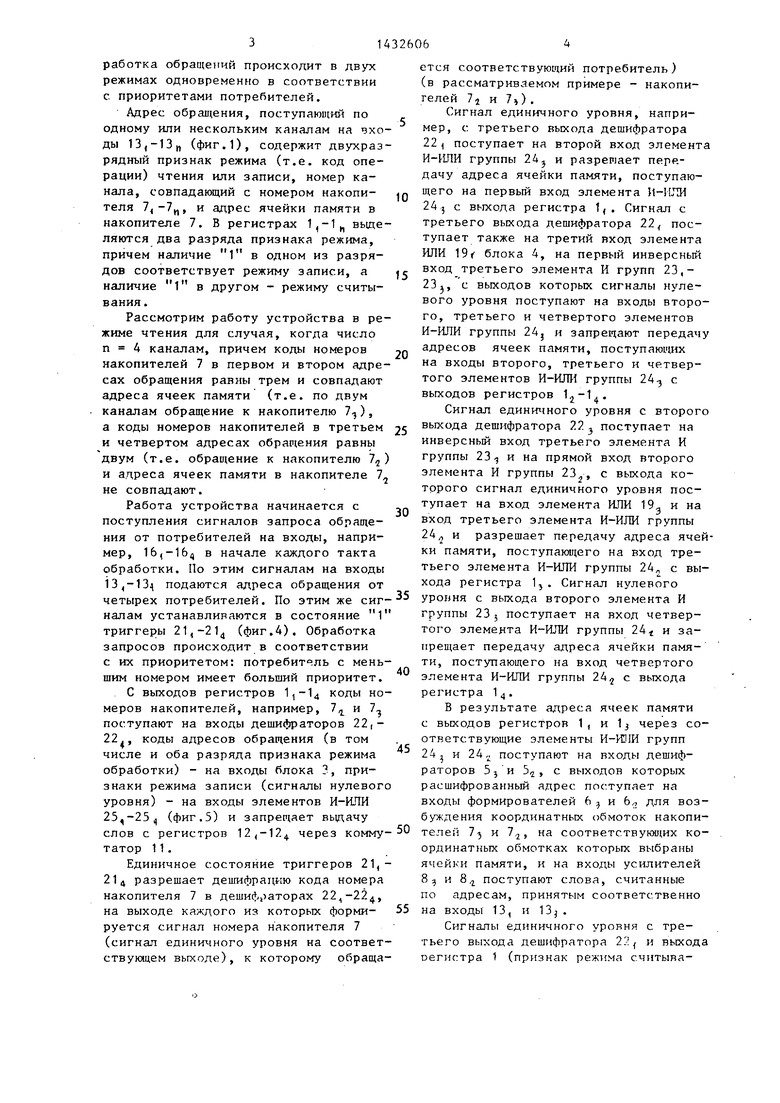

Блок 4 сброса обслуженных запросов (фиг.З) содержит элементы РШИ 19,-19„ и элементы 20,-20 задержки о

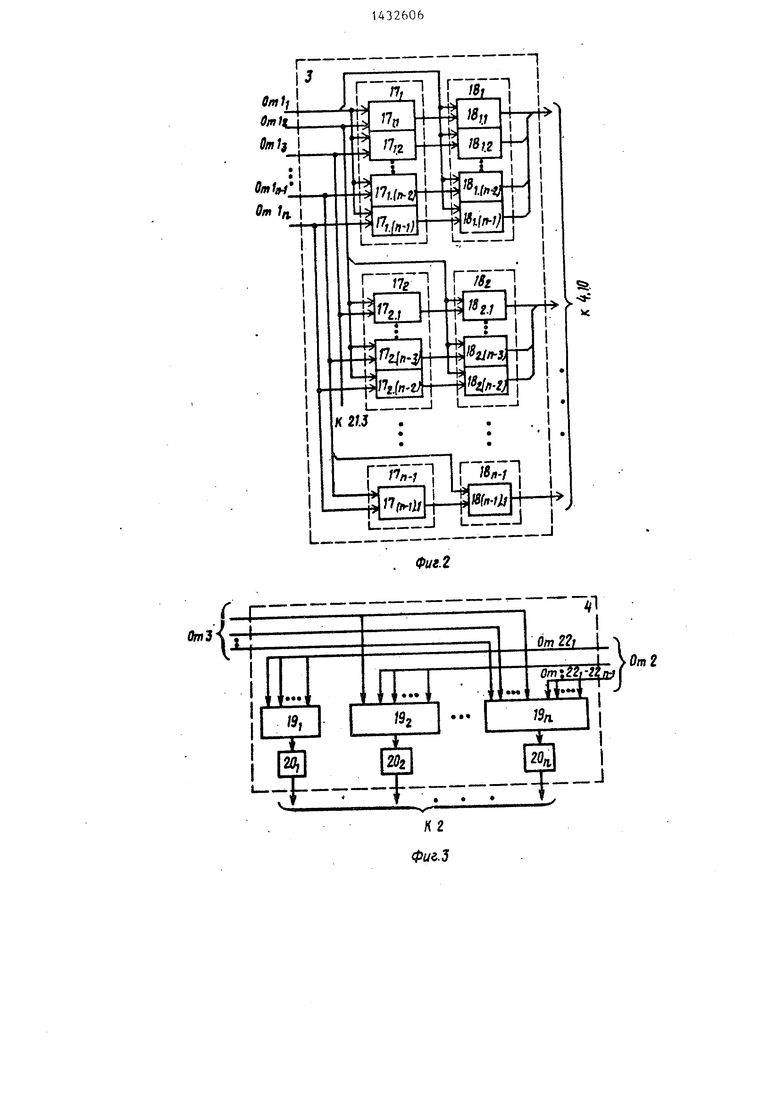

Блок 2 коммутации адресов (фиг.4) содержит триггеры 21,-21п, дешифраторы 22,-22„, группы 23,-23„, элементов И и группы 24,-24 элементов И-ИЛИ.

Коммутатор 1 записьгеаемых данных (фиг.З) содержит группы элементов И-ИЛИ 25,-25„.

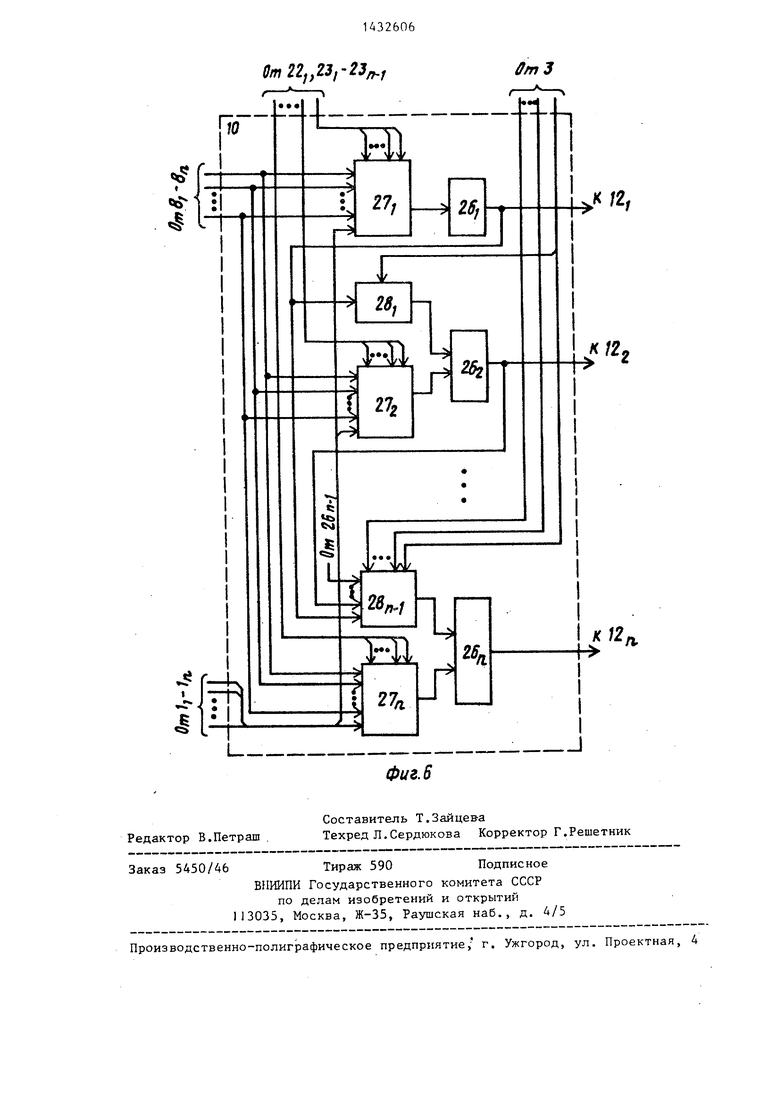

Коммутатор 10 считанных данных (фиг.6) содержит элементы ИЛИ 26-26„ , группы элементов И 27, -27„ и 28, - 28 ., . В целях упрощения функциональной схемы устройства и понимания принципа его работы цепи установки в исходное состояние и синхронизации не показаны.

Устройство работает следующим образом.

Устройство работает в режимах записи и чтения, возможен также случай смешанного режима, когда часть потребителей обращается для записи, а часть - для чтения слов, при этом обработка обращений происходит в двух режимах одновременно в соответствии с приоритетами потребителей.

Адрес обращения, поступаюв(ий по одному или нескольким каналам на чхо- ды 13,-13п (фиг.1), содержит двухразрядный признак режима (т.е. код операции) чтения или записи, номер канала, совпадающий с номером накопителя , и адрес ячейки памяти в накопителе 7. В регистрах 1,-1 вьще- ляются два разряда признака режима, причем наличие 1 в одном из разряts

дов соответствует режиму записи, а наличие 1 в другом - режиму считывания.

Рассмотрим работу устройства в режиме чтения для случая, когда число п 4 каналам, причем коды номеров 20 накопителей 7 в первом и втором адресах обращения равны трем и совпадают адреса ячеек памяти (т.е. по двум каналам обращение к накопителю 7), а коды номеров накопителей в третьем и четвертом адресах обращения равны двум (т.е. обращение к накопителю 7) и адреса ячеек памяти в накопителе 7 не совпадают.

Работа устройства начинается с поступления сигналов запроса обращения от потребителей на входы, например, 16,-16 в начале каждого такта обработки. По этим сигналам на входы 13,-13;( подаются адреса обращения от

Сигнал единичного уровня, например, с третьего выхода дешифратора 22( поступает на второй вход элемент И-ИЛИ группы 24J и разрешает передачу адреса ячейки памяти, поступающего на первый вход элемента И-ИЛИ 24 с выхода регистра t,. Сигнал с третьего выхода дешифратора 22 поступает также на третий вход элемента ИЛИ 19 блока 4, на первый инверсный вход третьего элемента И групп 23,- 23J, с выходов которых сигналы нулевого уровня поступают на входы второго, третьего и четвертого элементов И-ИЛИ группы 24J и запрещают передачу адресов ячеек памяти, поступающих на входы второго, третьего и четвертого элементов И-ИЛИ группы 24 с выходов регистров .

Сигнал единичного уровня с второго jc выхода дешифратора 22 поступает на инверсный вход третьего элемента И группы 23 и на прямой вход второго

30

элемента И группы 23 , с выхода которого сигнал единичного уровня поступает на вход элемента ИЛИ 19 и на вход третьего элемента И-ИЛИ группы 24, и разрешает передачу адреса ячей

тьего элемента И-ИЛИ группы 24„ с выхода регистра 1,. Сигнал нулевого

четырех потребителей. По этим же сиг- уроння с выхода второго элемента И налам устанавливаются в состояние 1 группы 23, поступает на вход четвер- триггеры 21,-21 (фиг.4). Обработка того элемента И-ИЛИ группы 24 и за- запросов происходит в соответствии с их приоритетом: потребитель с меньшим номером имеет больший приоритет. С выходов регистров коды но40

прещает передачу адреса ячейки памяти, поступающего на вход четвертого элемента И-ИЛИ группы 24 с выхода регистра 1.,.

меров накопителей, например, 7 и 7 поступают на входы дешифраторов 22,- 22,, коды адресов обращения (в том числе и оба разряда признака режима обработки) - на входы блока 3, признаки режима записи (сигналы нулевог уровня) - на входы элементов И-ИЛИ 25,-254 (фиг.5) и запрещает вьдачу

слов с регистров 12,-12 через комму татор 11.

Единичное состояние триггеров 21, 214 разрешает дешифрацию кода номера накопителя 7 в дешифраторах 22,-22,

на выходе каждого из которых форми-

руется сигнал номера накопителя 7 (сигнал единичного уровня на соответствующем вьгходе), к которому обраща

ется соответствующий потребитель) (в рассматриваемом примере - накопителей 7j и 7) .

Сигнал единичного уровня, например, с третьего выхода дешифратора 22( поступает на второй вход элемента И-ИЛИ группы 24J и разрешает передачу адреса ячейки памяти, поступающего на первый вход элемента И-ИЛИ 24 с выхода регистра t,. Сигнал с третьего выхода дешифратора 22 поступает также на третий вход элемента ИЛИ 19 блока 4, на первый инверсный вход третьего элемента И групп 23,- 23J, с выходов которых сигналы нулевого уровня поступают на входы второго, третьего и четвертого элементов И-ИЛИ группы 24J и запрещают передачу адресов ячеек памяти, поступающих на входы второго, третьего и четвертого элементов И-ИЛИ группы 24 с выходов регистров .

Сигнал единичного уровня с второго выхода дешифратора 22 поступает на инверсный вход третьего элемента И группы 23 и на прямой вход второго

элемента И группы 23 , с выхода которого сигнал единичного уровня поступает на вход элемента ИЛИ 19 и на вход третьего элемента И-ИЛИ группы 24, и разрешает передачу адреса ячейтьего элемента И-ИЛИ группы 24„ с выхода регистра 1,. Сигнал нулевого

уроння с выхода второго элемента И группы 23, поступает на вход четвер- того элемента И-ИЛИ группы 24 и за-

уроння с выхода второго элемента И группы 23, поступает на вход четвер- того элемента И-ИЛИ группы 24 и за-

прещает передачу адреса ячейки памяти, поступающего на вход четвертого элемента И-ИЛИ группы 24 с выхода регистра 1.,.

В результате адреса ячеек памяти с выходов регистров 1, и Ij через соответствующие элементы И-Ш1И групп 24 и 24,; поступают на входы дешифраторов 55 и 5, с выходов которых расшифрованный адрес поступает на входы формирователей 6 и 6., для возбуждения координатных обмоток накопителей 7з и 72, на соответствуюв1их координатных обмотках которых выбраны ячейки памяти, и на входы усилителей 8 и 8 поступают слова, считанные по адресам, принятым соответственно

Сигнапы единичного уровня с третьего выхода дешифратора 22 и выхода оегистра 1 (признак режима считывания) поступают соответственно на входы элементов И 27, и разрешают передачу слова, прступакяцего на вход третьего элемента И 27, с выхода усили- .дгеля 8j и далее на выход элемента ИЛИ 26,..

Сигналы единичного уровня с выхода второго элемента И группы 23 и выхода регистра 1 Чпризнак режима считывания) поступают соответственно на входы элементов И 27 и разрешают передачу слова, поступающего на вход соответствующего элемента И 27 с выхода усилителя 8 и далее на вЬ Лсод элемента ИЛИ 26j.

Для рассматриваемого случая (совпадение адресов обра0 ения по первому и второму каналам) на вьжоде схемы 17,2.1 (фиг.2) появляется сигнал единичного уровня, который поступит на вход элемента И 18 «, , на, другой вход которого поступает признак режима считывания) сигнал единичного уровня) с регистра 1 /.

Сигнал единичного уровня с выхода элемента И 18 ,., блока 3, свидетельствующий о совпадении адресов обращения первого и второго каналов в режиме чтения, поступает на вход элемента 202 и на вход элемента И 28j и разрешает передачу слова, поступающего с выхода элемента Е1Ж 26, через элемент И 28 - на вькод элемента ИЛИ 26,2

С выходов элементов ИЛИ 26,-26j считанные слова поступагот на входы регистров 12j-123 и далее на выходы АЗ устройства, С выходов злемен тов или сигнал единютного уровня, задержанные элементами 20 203 задержки на время, необходимое для считывания слова,, устанавливают триггеры 21,(-215 в нулевое состояние При этом сбрасываются обработанные обращения (на выходах дешифраторов 22,-22j появляются сигналы нулевого уровня) и разрешается поступление сигналов обращения от первого, второго и третьего каналов в следующем такте. Если этих сигналов установки не поступило, то сигнал единичного уровня с второго выхода дешифратора

22 поступает на прямой вход второго адресов, первьй дешифратор адреса.

элемента И группы 231, с выхода которого сигнал единичного уровня поступает на вход элемента ИЛИ 194, на ; вхтэд четвертого элемента К-ИЛИ группы

первый формирователь адресных сигн лов, первьй усилитель чтения, комм татор считанньгх данных, коммутатор записьшаемых данных, первый и втор

24 и разрешает передачу адреса ячейки памяти, поступающего на вход четвертого элемента И-ИЛИ группы 24 с выхода регистра 1,

В результате адрес ячейки памяти с вьгхода элемента И-ИЛИ группы 24 поступает на вход дешифратора 5, с . выхода которого сигналы поступают на

Q вход формирователя 6 для возбуждения координатных обмоток накопителя 7, в котором будет выбрана ячейка памяти, и на вход усилителя 8 поступает слово, считанное по адресу, принятоg. му на вход 13,

Сигналы с единичного уровня с выхода второго элемента И группы 23 и с выхода регистра 1 .гризнак режима считывания) поступают соответстQ венно на входы элементов И 274.

(фиг,6) и разрешают передачу слова, поступакнцего на вход соответствующего элемента И 274- с выхода усилителя 8, на выход элемента ИЛИ 26 и далее

5

5 на вход регистра 12ц, с выхода которого поступает ка выход 144.

В режиме записи слова, предназначенные для записи, поступают на входы регистров , с выходов

5 которых через коммутатор 1 1 по сигналам признака режима записи (сигналы единичного уройня), поступающим с вы- ходов регистров 1, на входы коммутатора 11, и сигналам поступающим с выходов блока 2 на входы коммутатора 11, поступают на. соответствующие усилители ,, с выходов которых - на входы накопителей 7,-7,. В режиме записи блок 3 не работает, так как на его входы с выходов регистров 14-1,, поступают сигналы нулевого уровня (признаки режима считьшания), Признаки режима считывания поступают также на входы коммутатора 10 и запрещают вьщачу слов с усилителей 8;,-8и, Выбор ячеек памяти в накопителях для записи слов осуществляется логично режиму чтения.

0

45

ана

Формула изобретения

1, Многоканальное оперативное запоминающее устройство, содержащее первый накопитель, блок коммутации

первый формирователь адресных сигналов, первьй усилитель чтения, коммутатор считанньгх данных, коммутатор записьшаемых данных, первый и второй

регистры слова, первый формирователь информационных сигналов, первый и второй регистры адреса, информационные входы которых являются соответственно адресными входами первого и второго каналов устройства, информационными выходами первого и второго каналов которого являются соответственно выходы первого и второго реги- стров слова, причем выходы первого и второго регистров адреса соединены соответственно с адресными входами первой и второй групп блока коммутации адресов, адресные выходы первой группы которого подключены к информационным входам первого дешифратора адреса, выход которого соединен с входом первого формирователя адресных сигналов, выход которого подключен к адресному входу первого накопителя, информационный выход которого соединен с входом первого усилителя чтения, выход которого подключен к первому информационному входу комнутато- ра считанных данных, первый и второй выходы которого соединены с первыми информационными входами первого и второго регистров слова, выходы которых подключены соответственно к первому и второму информационным входам коммутатора записываемых данных, первый выход которого соединен с информационным входом первого формирователя информационных сигналов, выход которого подключен к информационному входу первого накопителя, вторые информационные входы первого и второго регистров слова являются информационными входами первого и второго каналов устройства, отличающее- с я тем, что, с целью расширения области применения устройства путем обеспечения одновременного чтения по произвольному числу несовпадающих адресов и повышения быстродействия в режиме чтения, в него введены блок анализа адресов, блок сброса обслуженных запросов, с второго по п-й (где п 1, число каналов) накопители, с второго по п-й дешифраторы адреса, с второго по п-й формирователи адресных сигналов, с второго по п-й усилители чтения, с второго по п-й формирователи информационных сигналов, с третьего по п-й регистры адреса и с третьего по п-й регистры слова, выходы которых являются информационными выходами с третьего по п-й

5

0

5

0

5

0

5

0

5

каналов устройства, адресными входами с третьего по п-й канапов которого являются информационные входы регистров адреса с третьего по п-й, выходы которых подключены к адресным входам с третьей по п-ю групп блока коммутации адресов, адресные выходы с второй по п-ю групп которого соединены с ин-. формационными входами одноименных дешифраторов адреса, выходы которых под- подключены к входам одноименных формирователей адресных сигналов, выходы которых соединены с адресными входами одноименных накопителей с второго по п-й, информационные выходы которых подключены к информационным входам одноименных усилителей чтения, выходы которых соединены с иг1формационными входами с второго по п-й коммутатора считанных данных, выходы с третьего по п-й которого подключены к первым информационным входам одноименных регистров слова, выходы которых соединены с информационными входами с третьего по п-й коммутатора записываемых данных, выходы с второго по п-й которого подключены к информационным входам одноименных формирователей информационных сигналов, выходы которых соединены с информационными входами накопителей с второго по п-й, причем выходы кода режима регистров адреса с первого по п-й подключены к управ- ляюгдим входам перворЧ группы коммутатора записываемых данных и управляющим входам первой группы коммутатора считанных данных, управляющие входы второй группы которого соединены с выходами блока анализа адресов и входами признаков совпадения адресов блока сброса обслуженных запросов, выходы которого подключены к входам установки блока коммутации адресов, выходы кода номера накопителя, первой и второй групп которого соединены соответственно с входами установки первой и второй групп блока сброса обслуженных запросов и управляющими входами третьей группы комм татора считанных сигналов, информационные входы блока анализа адресов подключены к выходам адреса регистров адреса с первого по п-й, управляю1чие входы второй группы коммутатора зггписывае- мых данных соединены с выходами кода номера накопителя третьей группы блока коммутации адресов, входы обращения которого являются входами обращения устройства, информационными входами с третьего по п-й каналов, кото- рого являются вторые информационные входы регистров слова с третьего по п-й.

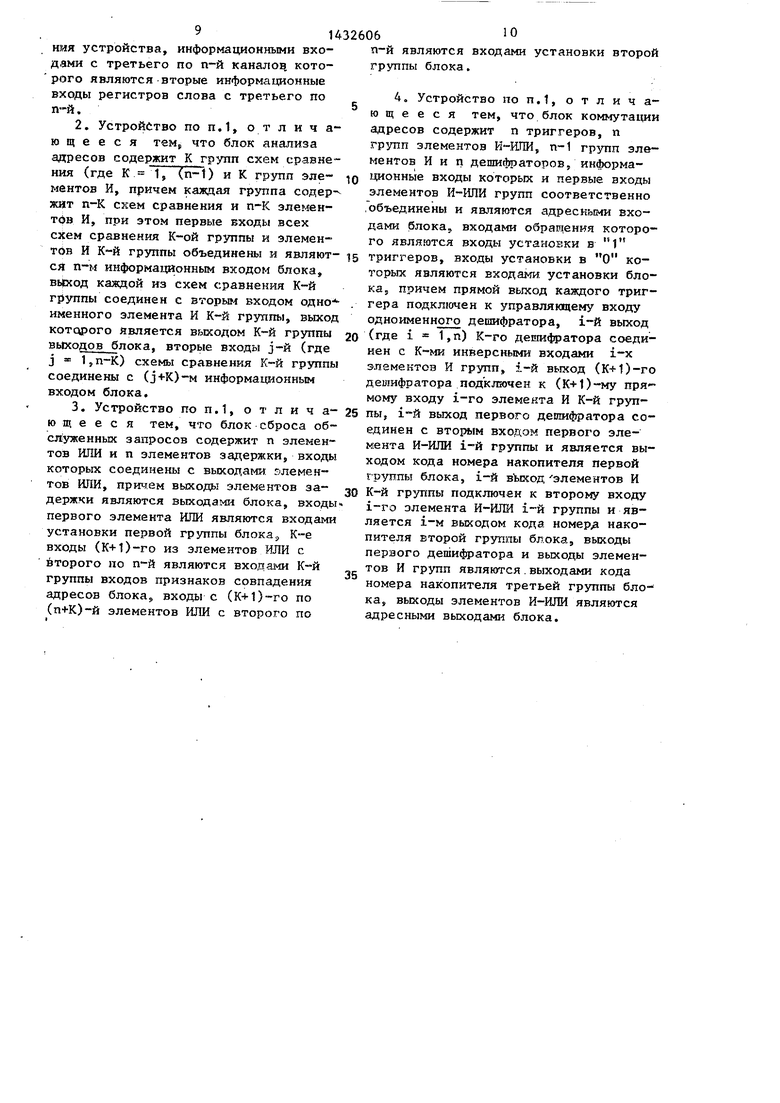

жнт п-К скем сравнения и п-К элементов И, при этом первые входы всех схем сравнения К-ой группы и элементов И К-й группы объединены и являют- § триггеров, входы установки в О кося п-м информационным входом блока, торых являются входами установки бло- выход каждой из схем сравнения К-й соединен с вторым входом одно именного элемента И К-й группы, выход

ка, причем прямой выход каждого триггера подключен к управляющему входу одноименного дешифратора, i-й выход

(где i 1,п) К-го дешифратора соединен с инверсными входами i-x элементов И групп, i-й выход (K+D-ro дешифратора подключен к (К+1)Му пря- мому входу i-ro элемента И К-й групKOTcvporo является выходом К-й группы 20 выходо в блок а, вторые входы j-й (где j 1,п-К) схемы сравнения К-й группы соединены с (j+K)-M информационным входом блока.

первого элемента ИЛИ являются входами установки первой группы блока., К-е входы (К+1)-го из элементов ИЛИ с йторого по п-й являются входами К-й группы входов признаков совпадения адресов блока, входы с (К+1)-го по (п+К)-й элементов ИЛИ с второго по

п-й являются входами установки второй группы блока.

триггеров, входы установки в О которых являются входами установки бло-

триггеров, входы установки в О которых являются входами установки бло-

ка, причем прямой выход каждого тригтриггеров, входы установки в О которых являются входами установки бло-

гера подключен к управляющему входу одноименного дешифратора, i-й выход

(где i 1,п) К-го дешифратора соединен с инверсными входами i-x элементов И групп, i-й выход (K+D-ro дешифратора подключен к (К+1)Му пря- мому входу i-ro элемента И К-й груп25 пы, i-й выход первого дешифратора со- д

35

единен с вторым входом первого элемента И-ИЛИ i-й группы и является выходом кода номера накопителя первой группы блока, i-й вТыход элементов И К-й группы подключен к второму входу i-ro элемента И-ИЛИ i-й группы и является i-M выходом кода номер;а накопителя второй группы блока, выходы первого дешифратора и выходы элементов И групп являются.выходами кода номера накопителя третьей группы блока, выходы элементов И-ИЛИ являются адресными выходами блока.

fffn -12fi

dm 2

К5п

От tfl.

;U Ml

f}m22j,23f 23 j

I.

fffn 3

Фиг. В

| Многоканальное буферное запоминающее устройство | 1985 |

|

SU1280453A1 |

| ка | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство | 1984 |

|

SU1236551A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-23—Публикация

1987-03-23—Подача