Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств п вышенной надежности на базе кристаллов памяти с многоразг- рядной организацией.

Цель изобретения - упрощение и повышение надежности устройства,

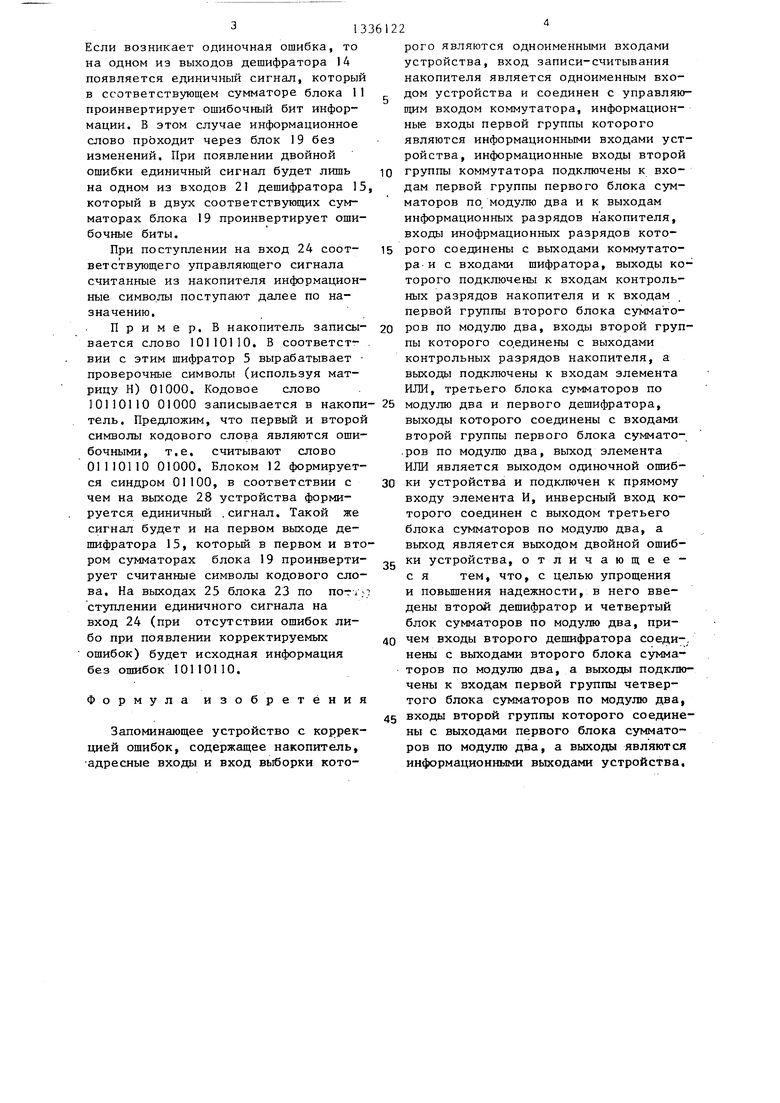

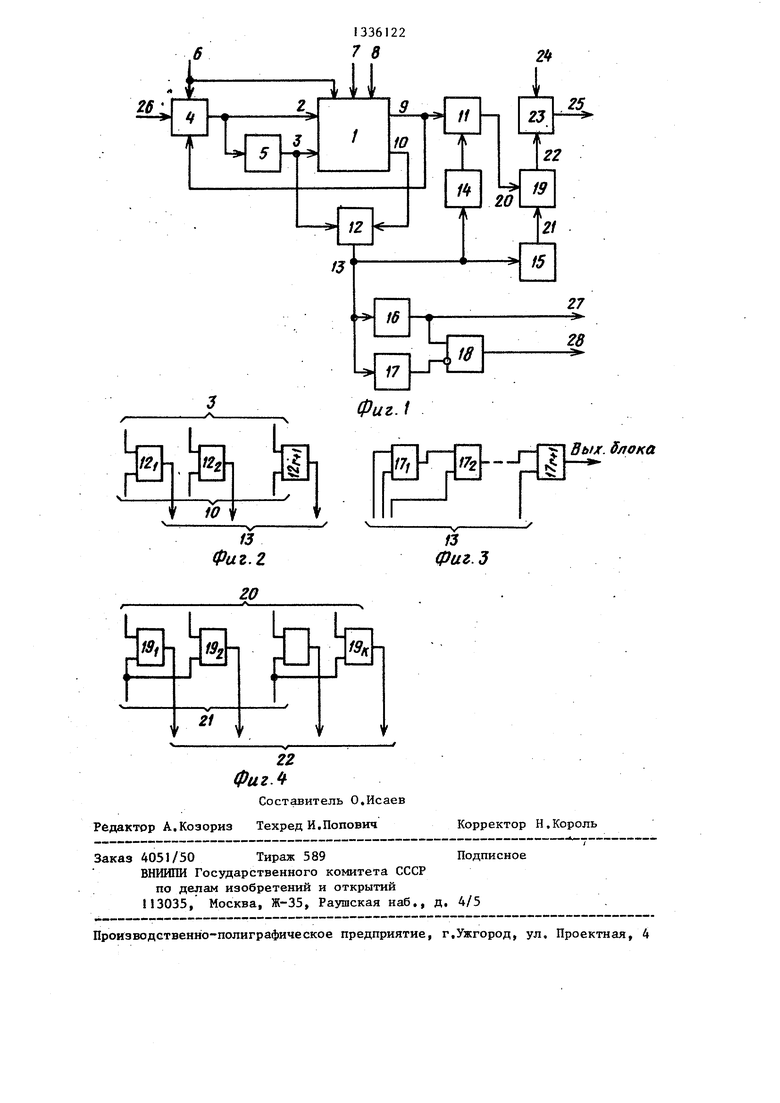

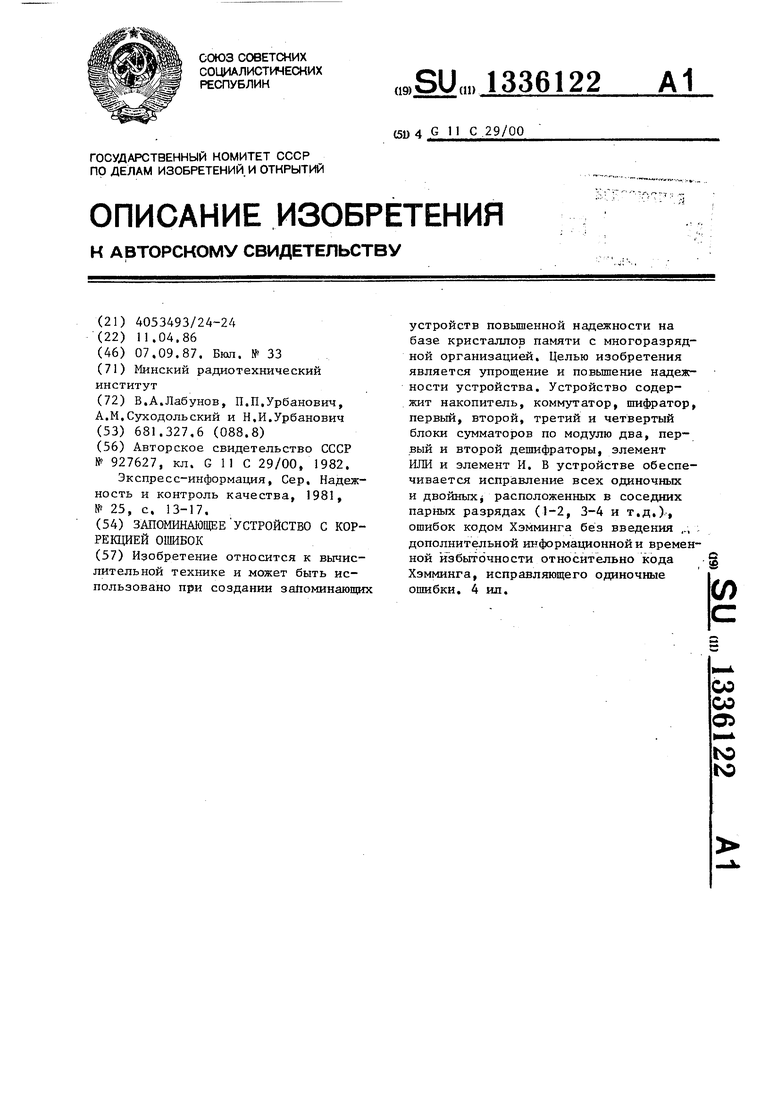

На фиг. 1 представлена структурная схема запоминающего устройства с коррекцией ошибок; на фиг.2- функциональная схема первого (второго)блока сумматоров по модулю два; на фиг. 3 - функциональная схема третьего блока сумматоров по модулю два; на фиг,4 - функциональная схема четвертого блока сумматоров по модулю два,

Запоминаюп1ее устройство (фиг,1) содержит накопитель 1 с входами информационных 2 и контрольных 3 разрядов, коммутатор 4, шифратор 5, входы записи считывания 6, выборки 7 и адреса 8, выходы информационных 9 и контрольных 10 разрядов накопителя 1, первый блок 11 сумматоров по мо- дулю два, второй блок 12 сумматоров по модулю два с выходами 13, первый 14 и второй 15 дешифраторы, элемент ИЛИ 16, третий блок 17 сумматоров по модулю два, элемент И 18, четвертый блок 19 сумматоров по модулю два. с входами 20 и 21 и выходами 22,

Устройство содержит также блок 23 вывода с синхровходом 24 и выходами 25 и информационный вход 26,

Блок 12 (фиг,2) состоит из отдельных сумматоров по модулю два по числу проверочных символов кодового слова. Аналогично строится и блок 1I, однако число дискретных сумматоров равно количеству информационных символов слова. Блок 17 (фиг,3) состоит из г сумматоров по модулю два (по числу .проверочных символов).

Блок 19 (фиг,4) состоит из сумматоров по модулю два (по числу инфор мационных символов), Накопитель 1 состоит из отдельных кристаллов памяти с многоразрядной организацией обращение. Одновременно обращение может производиться к одному либо к нескольким кристаллам (БИС) в зависимости от длины слова и разрядности кристалла.

По входу 6 устройства поступает сигнал, задающий режим функционирования устройства (запись-считывание), по входу 7 - сигнал выборки кристалла (кристаллов), по входу 24 - сигнал, разрешающий использование информации, считанной из накопителя, -Все управляющие сигналы связаны с процессором (не показан).

На управляющем выходе 27 устройства единичной сигнал появляется при наличии хотя бы одного ошибочно- го символа в считанном кодовом слове, на выходе 28 - при наличии двойной ошибки. Такие выходы (их состояние) учитываются лишь в режиме считывания через определенный промежуток време- 5 ни после начала цикла.

Принцип работы устройства, в особенности принцип коррекции ошибок, основан на свойстве кода Хэмминга, состоящего в том, что для исправле- 0 ния всех одиночных и всех парных двойных ошибок необходимо такое же число проверочных символов, как и для модифицированного кода Хэмминга с кодовым расстоянием, равным 4, 5 Например, проверочная Матрица Н 8 имеет вид: 10000 01000 00100

0 U011U111 00010 00001

При К 8 необходимо ( + проверочных символов. При возникновении одной ошибки синдром имеет нечетный 5 вес (число единиц), а при возникновении двойной - четный.

Устройство работает следующим образом.

Режим работы. На входах 26 - ин- 0 формация, подлежащая записи в накопитель по адресу 8, На основании этого шифратор 5 вырабатывает проверочные символы. Кодовое слово, состоящее из информационных и провероч- 5 ных битов по входам соответственно 2 и 3 записывается в накопитель 1, На этом цикл записи заканчивается.

Режим считывания. На входе 6 устройств - нулевой сигнал. Считываемые 0 из накопителя информационные и проверочные разряды кодового слова поступают соответственно в блок 11 сумматоров, ,через коммутатор 4 - шифратор 5 и на вторые входы блока 12 суммато- g ров, на первые входы которого поступает проверочное число с выходов шифратора 5, Таким образом, на выходах 13 блока 12 формируется синдром, равный нулю лишь при отсутствии ошибок.

кода при К

. 11101001

10011011

Н 01011100

00110111

11100110

Если возникает одиночная ошибка, то на одном из выходов дешифратора 14 появляется единичный сигнал, который в соответствующем сумматоре блока 11 проинвертирует ошибочный бит информации. В этом случае информационное слово проходит через блок 19 без изменений. При появлении двойной ошибки единичный сигнал будет лишь на одном из входов 21 дешифратора 15 который в двух соответствующих сумматорах блока 19 проинвертирует ошибочные биты.

При поступлении на вход 24 соответствующего управляющего сигнала считанные из накопителя информационные символы поступают далее по назначению.

Пример. В накопитель записывается слово 10110110. В соответст- ВИИ с этим шифратор 5 вырабатывает проверочные символы (используя матрицу Н) 01000. Кодовое слово

10110110 01000 записывается в накопи- 25 модулю два и первого дешифратора.

тель. Предложим, что первый и второй символы кодового слова являются ошибочными, т.е. считывают слово 01110110 01000. Блоком 12 формируется синдром 01100, в соответствии с чем на выходе 28 устройства формируется единичный .сигнал. Такой же сигнал будет и на первом выходе дешифратора 15, который в первом и втором сумматорах блока 19 проинвертирует считанные символы кодового слова. На выходах 25 блока 23 по no-v;: ступлении единичного сигнала на вход 24 (при OTCjrrcTBHH ошибок либо при появлении корректируемых ошибок) будет исходная информация без ошибок 10110110.

Формула изобретения

Запоминающее устройство с коррекцией ошибок, содержащее накопитель, адресные входы и вход выборки которого являются одноименными входами устройства, вход записи-считывания накопителя является одноименным входом устройства и соединен с управляющим входом коммутатора, информационные входы первой группы которого являются информационными входами устройства, информационные входы второй

группы коммутатора подключены к входам первой группы первого блока сумматоров по модулю два и к выходам информационных разрядов накопителя, входы инофрмационных разрядов которого соединены с выходами коммутатора- и с входами шифратора, выходы которого подключены к входам контрольных разрядов накопителя и к входам первой группы второго блока сумматоров по модулю два, входы второй группы которого соединены с выходами контрольных разрядов накопителя, а выходы подключены к входам элемента ИЛИ, третьего блока сумматоров по

выходы которого соединены с входами второй группы первого блока суммато- ров по модулю два, выход элемента ИЛИ является выходом одиночной ошибки устройства и подключен к прямому входу элемента И, инверсный вход которого соединен с выходом третьего блока сумматоров по модулю два, а выход является выходом двойной ошибки устройства, отличающее- с я тем, что, с целью упрощения и повышения надежности, в него введены второй дешифратор и четвертый блок сумматоров по модулю два, причем входы второго дешифратора соеди-, нены с выходами второго блока сумматоров по модулю два, а выходы подключены к входам первой группы четвертого блока сумматоров по модулю два,

входы второй группы которого соединены с выходами первого блока сумматоров по модулю два, а выходы являют ся информационными выходами устройства.

22 Фиг л

Составитель О.Исаев Редактор А.Козориз Техред И.Попович

Заказ 4051/50 Тираж 589Подписное

ВНИИПИ Государствеиного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

Фиг.1

дых. блока

Корректор Н. Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1297120A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании запоминающих устройств повышенной надежности на базе кристаллов памяти с многоразрядной организацией. Целью изобретения является упрощение и повышение надежности устройства. Устройство содержит накопитель, коммутатор, шифратор, первый, второй, третий и четвертый блоки сумматоров по модулю два, первый и второй депшфраторы, элемент ИЛИ и элемент И. В устройстве обеспечивается испра.вление всех одиночных и двойныхi расположенных в соседних парных разрядах (1-2, 3-4 и т.д.)., ошибок кодом Хэмминга без введения ,., :. дополнительной информационной и временной избыточности относительно кода Хэмминга, исправляющего одиночные ошибки. 4 ил. i (Л со СО а ю ю

| Разборный катамаран | 1980 |

|

SU927627A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Экспресс-информация, Сер, Надежность и контроль качества, 1981, № 25, с | |||

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1987-09-07—Публикация

1986-04-11—Подача