113

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств (ЗУ) повышенной надежности

Целью изобретения является повы- шение надежности устройства.

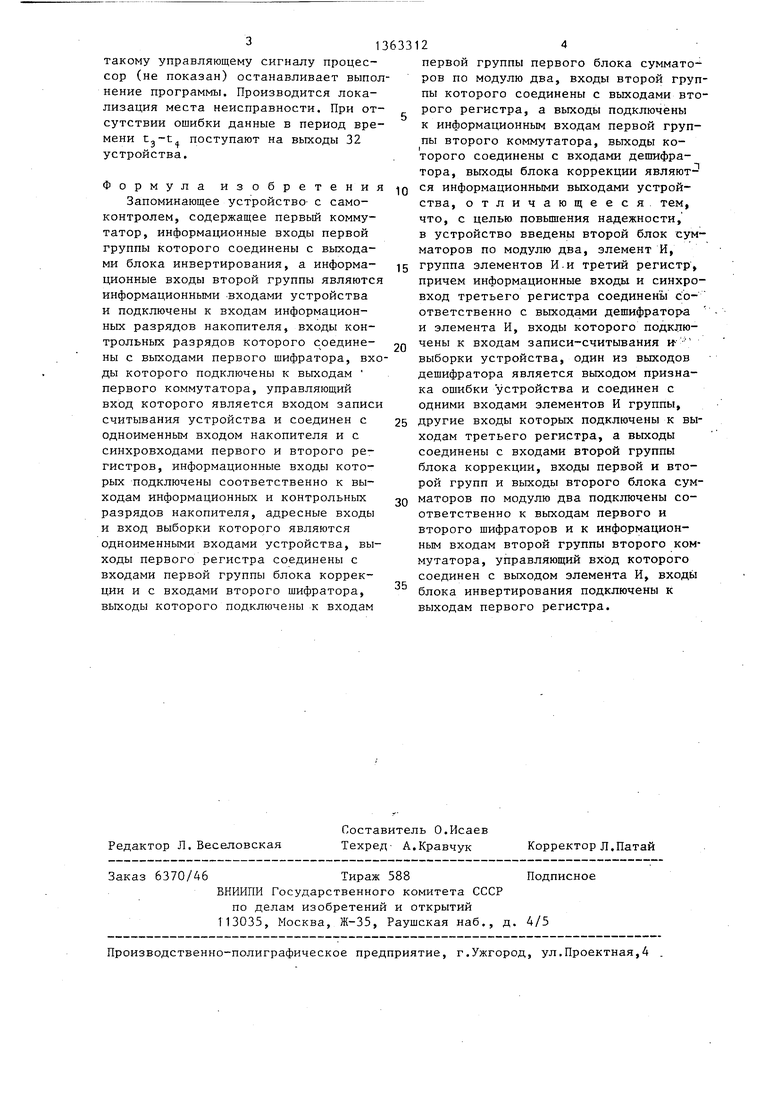

На чертеже изображена схема запоминающего устройства с самоконтролем.

Устройство содержит накопитель 1, информационные входы 2, адресные входы 3, вход 4 записи-считывания, вход 5 выборки, первьм коммутатор 6 первьш шифратор 7, входы контрольных разрядов 8, выходы 9. информационных и 10 контрольных разрядов накопителя 1, первьш 11 и второй 12 регистры, входы 13 блока коррекции 14, второй шифратор 15у блок 16 инвертирования с выходами 17,. первый блок 18- сумма- торов по Модулю два с входами 19,- 20 и выходами 21, второй коммутатор 22 с выходами 23,.второй блок 24 сумматоров -по модулю два, дешифратор 25 с выходами 26,27, третий регистр 28,. группа элементов И 29,. выход 30 элемента И 31, информационные выходы 32.

,Принцип функционирования цепей самоконтроля основан на использовании свойства кода Хемминга, состоящего в том, что при правильной работе этих цепей синдромы считанного из накопителя и инверсного ему кодовых слов отличаются во всех позициях, т.е. также являются прямым- и инверсным,, При неправильной работе цепей коррекции такое условие не выполняется.

Устройство работает следующим образом. , .

В режиме записи- информации на входы 3-5 устройства подаются адрес опрашиваемой ячейки накопителя 1, сигнал, задающий режим, и сигнал выборки кристалла соответственна. .Коммутатор 6 пропускает на выход информационные символы,, в соответствии с которыми шифратор 7 вьфабатывает контрольные символы кодового слова,, последние по входам 8 вместе с информационными символами записываются в на- копитель по .поступлении сигнала разрешения записи (tj), после окончания чего (tj) цикл записи заканчивается.

В реядаме считывания информации опрашив.аемая ячейка выбирается как ив режиме записи. На входе 4-присутствует противоположный логический уровень сигнала, на выходе элемента

5

о

0

5

122

И 31 - сигнал логической единицы. В регистры 11 и 12 с выходов накопителя 9 и 10 происходит запись считанных из накопителя соответственно информационных и контрольных символов кодового слова. Считанные информационные символы поступают в шифратор 15, а инверсные информационные символы через коммутатор 6 - в шифратор 7, где происходит формирование новых наборов КОНТРОЛЬНЫХ символов.. Сформированные шифратором 15 контрольные символы в блоке 18 сумматоров поразрядно сравниваются со считанными из Накопителя контрольными разрядами. На выходах 21 таким образом формируется признак ошибки, (синдром). Если в считанных, из накопителя символах нет ошибок, то синдром равен нулю, и отличен от нуля - в противном случае . Синдром проиа,ходит через коммутатор 22 и дешифрируется дешифратором 25, результат чего записывается в регистр 28. В момент времени t изменяется сигнал на входе 5, на выходе элемента И 31 - нулевой сигнал, разрешающий прохождение через хоммута- тор 22 двоичных символов, установленных на выходах блока 24, где к этому времени уже сформированасумма по модулю два контрольных символов, выработанных шифраторами 7 и 15. Если шифраторы и предшествуюшре им цепи прохождения соответствующих сигналов функционируют нормально, то на вы- .ходах блока 24 присутствуют единичные символы.

Если все цепи контроля не содер- жат неисправностей (включая дешифратор) , то на выходе 26 дешифратора 25 (выход 26 - обычный выход дешифратора, формирующий единичный сигнал, если на всех его входных шинах - еди- ничные сигналы) присутствует единичный сигнал, который при наличии ошибки в слове данных позволяет исправить эту ошибку в блоке 14 единичным сигналом с выхода регистра 28 через элементы И 29. При отсутствии ошибок в слове данных на выходах всех элементов И 29 - нулевые сигналы и изменений информационных символов не происходит.

Если же к моменту времени t с выхода дешифратора 25 на управляющий выход 26 устройства не поступит единичный .сигнал, то это соответствует наличию ошибки в цепях контроля. По

313633

такому управляющему сигналу процессор (не показан) останавливает выполнение программы. Производится локализация места неисправности. При отсутствии ошибки данные в период врепоступают на выходы 32

мени tj-t устройства,

Формула изобретени

Запоминающее устройство- с самоконтролем, содержащее первый коммутатор, информационные входы первой группы которого соединены с выходами блока инвертирования, а информационные входы второй группы являютс информационными входами устройства и подключены к входам информационных разрядов накопителя, входы контрольных разрядов которого соединены с выходами первого шифратора, вхды которого подключены к выходам первого коммутатора, управляющий вход которого является входом запис считывания устройства и соединен с одноименным входом накопителя и с синхровходами первого и второго регистров, информационные входы которых подключены соответственно к выходам информационных и контрольных разрядов накопителя, адресные входы и вход выборки которого являются одноименными входами устройства, выходы первого регистра соединены с входами первой группы блока коррекции и с входами второго шифратора, выходы которого подключены к входам

ор Л. Веселовская 6370/46

Составитель О.Исаев Техред- А.Кравчук

Кор Под

Тираж 588 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул,Проектная,4

0

5

0

5

0

5

124

первой группы первого блока сумматоров по модулю два, входы второй группы которого соединены с выходами второго регистра, а выходы подключены к информационным входам первой группы второго коммутатора, выходы которого соединены с входами дешифратора, выходы блока коррекции являются информационными выходами устройства, отличающееся тем, что, с целью повьш1ения надежности, в устройство введены второй блок сумматоров по модулю два, элемент И, группа элементов И.и третий регистр, причем информационные входы и синхро- вход третьего регистра соединены соответственно с выходами дешифратора и элемента И, входы которого подключены к входам записи-считывания и- - выборки устройства, один из выходов дешифратора является выходом признака ошибки устройства и соединен с одними входами элементов И группы, другие входы которых подключены к выходам третьего регистра, а выходы соединены с входами второй группы блока коррекции, входы первой и второй групп и выходы второго блока сумматоров по модулю два подключены соответственно к выходам первого и второго шифраторов и к информационным входам второй группы второго коммутатора, управляющий вход которого соединен с выходом элемента И, входы блока инвертирования подключены к выходам первого регистра.

Корректор Л.Патай Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1336122A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1985 |

|

SU1277214A1 |

| Запоминающее устройство | 1985 |

|

SU1295456A1 |

| Запоминающее устройство с исправлением ошибок | 1987 |

|

SU1585835A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1325569A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

Изобретение относится к вычислительной технике и может быть ис3 If 5 пользовано для построения запоминающих устройство (ЗУ) повышенной надежности. Целью изобретения является по- вьппение надежности устройства. Устройство содержит накопитель 1, первый и второй шифраторы 7,15, первый, второй и третий регистры 11,12,28, первый и второй блоки 18,24 сумматоров по модулю два, блок 16 инвертирования, первый и второй коммутаторы 6,22, дешифратор 25, блок 14 коррекции, группу 29 элементов И, элемент И 31. Повьшгение надежности устройства осуществляется путем контроля . всех цепей коррекции ошибок и цепей формирования контрольных разрядов кодового слова. 1 ил. i W С

| Устройство для контроля памяти | 1979 |

|

SU769641A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059630A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-12-30—Публикация

1986-02-06—Подача