Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти на базе БИС запоминающих устройств (ЗУ) со словарной ор- гарнизацией обращения.

Цель изобретения - повышение надежности устройства.

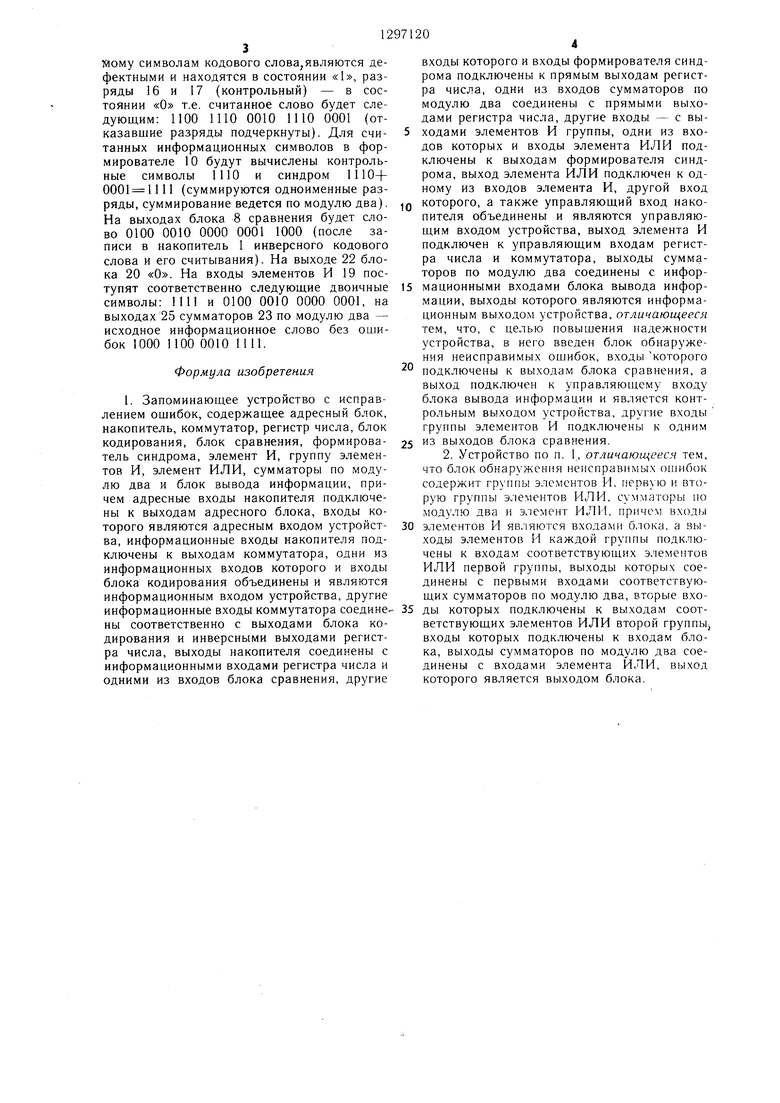

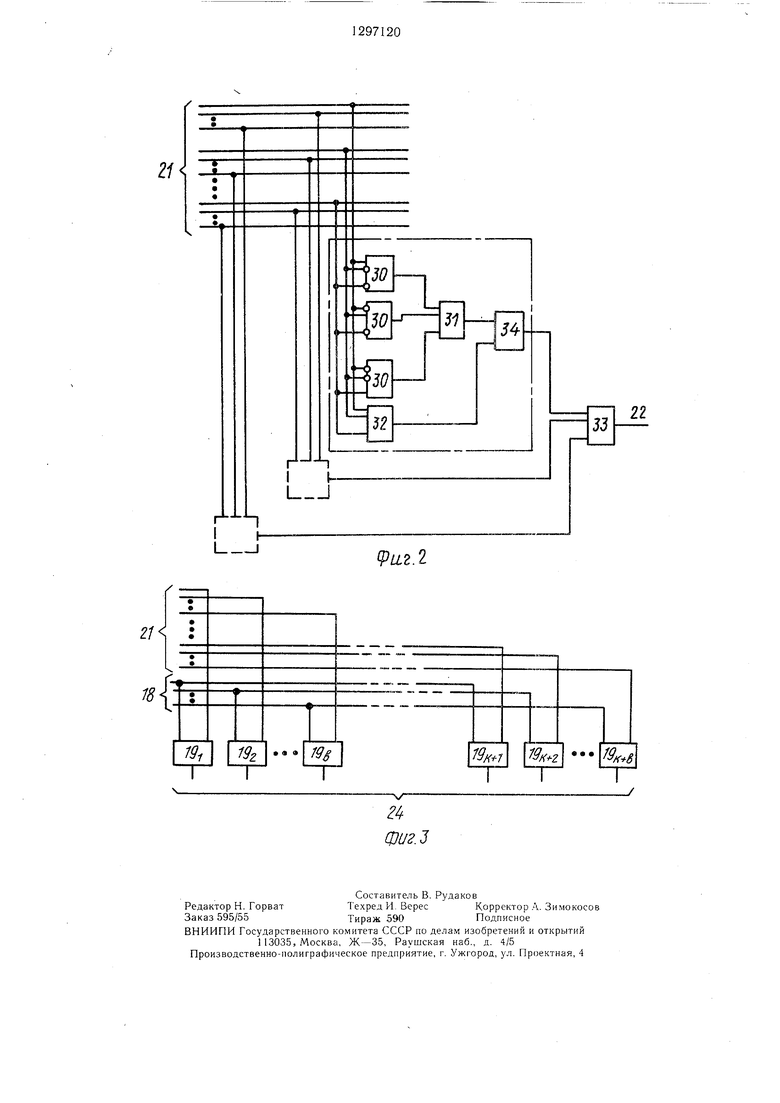

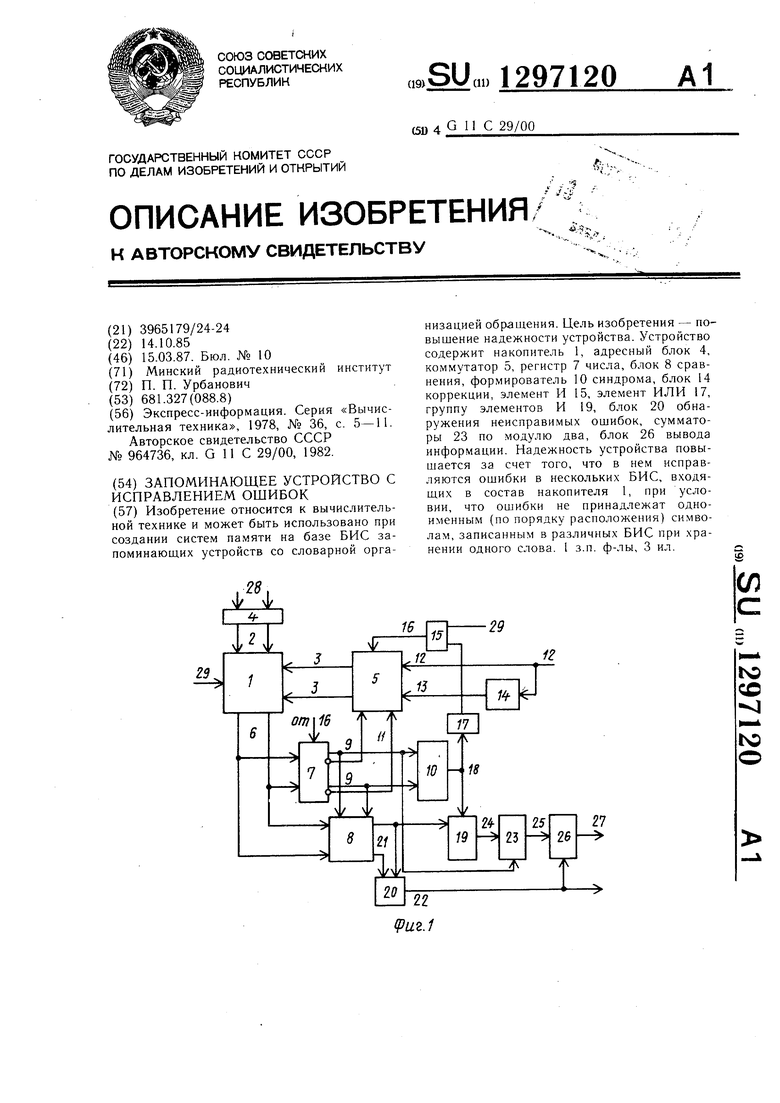

На фиг. i приведена структурная схема предложенного устройства; на фиг. 2 - функциональная схема блока обнаружения неисправимых ощибок; на фиг. 3 - соединение входов группы элементов И с выходами блока сравнения и формирователя синдрома.

Устройство (фиг. 1) содержит накопитель 1, адресные .2 и информационные 3 входы которого подключены соответственно к выходам адресного блока 4 и коммутатора 5. Выходь 6 накопителя соединены с входами регистра числа 7 и одними из входов блока 8 сравнения, другие входы которого связаны с прямыми выходами 9 регистра 7, соединенными также с входами формирователя 10 синдрома. Инверсные выходы регистра 7 соединены соответственно с входами 11 коммутатора 5, входы 12 и 13 которого подключены соответственно к информационному входу устройства и к выходу блока 14 кодирования. Устройство содержит также элемент И 15, выход 16 которого соединен с управляющими входами коммутатора 5 и регистра 7, элемент ИЛИ 17, входы 18 которого соединены с выходами формирователя 10 и одними из входов группы элементов И 19, блок 20 обнаружения неисправимых ошибок с входами 21 и выходом 22, сумматора 23 по модулю два, одни из входов которых подключены к одному из прямых выходов 9 ре истра 7, другие - к выходам 24 элементов И 19, а выходы 25 сумматоров 23 - к входам блока 26 вывода информации, имеющего выход 27. Входы 28 адресного блока 4 являются адресным входом устройства, управляю щий вход 29 устройства соединен с управляющими входами накопителя 1 и одним из входов элемента И 15.

Блок 20 (фиг. 2) содержит группы элементов И 30, первую группу элементов ИЛИ 31, вторую группу ИЛИ 32, элемент ИЛИ 33, сумматоры 34 по модулю два.

Устройство работает следующим образом. На прямых выходах 9 регистра 7 нулевые символы. В режиме записи информации на вход 12 коммутатора 5 вход блока 14 поступают «k и информационных символов, которые нужно записать в накопитель 1 по адресу, заданному блоком 4. Блок 14 кодирования вырабатывает «Ь контрольных символ ов. Сформированное таким образом кодовое слово длины k-|-b разрядов по сигналу записи на входе 29 устройства записывается в накопитель 1.

Пример. Пусть в накопитель нужно записать 16-разрядное слово: 1000 1100 0010

1111 (k 16). Накопитель строится на базе 4-разрядных Е)ИС ЗУ (Ь 4), т.е. по от- нощению к одной БИС информация может одновременно записываться в 4 элемента (или считываться). Блок кодирования формирует 4 контрольных символа :1000- и 20-разрядное кодовое слово записывается в накопитель 1

На этом цикл записи окончен.

В режиме считывания (задается противоположным режиму записи логическим сигналом на входе 29) считанная информация (20 разрядов) записывается в регистр 7. Формирователь 10 вырабатывает «Ь новых проверочных символов (синдром). Если в считанном из накопителя 1 слове нет ощибок, то все разряды синдрома равны нулю и синдром не равен нулю - в противном случае. Если в считанном слове нет ошибок, то на выходах блоков 8 и 20 и элементов 19 И будут нулевые сигналы. Информационные символы с выходов 9 регистра 7 проходят через

сумматоры 23 и далее в блок 26 без изменений. Блок 26 (в определенный момент времени, определяемый процессором) выдает информацию по назначению. Если в считываемом слове имеются ошибки во всех рядах одной БИС или в разноименных разрядах разных БИС (в обоих случаях общее число ошибок не больше Ь), то на выходе эле.мента ИЛИ 7 появляется единичный сигнал, который через элемент И 15 устанавливает ка управляющем входе коммутатора 5 сигнал, который устанавливает на входах 3 накопителя 1 инверсное по отношению к считанному кодовое слово, которое записывается в те же ячейки накопителя. Затем производится контрольное считывание инверсного кодового слова, которое

в блоке 8 сравнивается со считанным ранее (прямым кодовым словом). Состояние регистра 7 не изменяется. На выходах 21 блока 8, соответствующих отказавшим разрядам, будут единичные сигналы, поскольку даже при записи в отказавшую ячейку инверсного сигнала ее логическое состояние не изменится. Если отказавшими являются разноименные разряды в различных БИС, то на выходе 22 блока 20 будет нулевой сигнал, единичный сигнал будет в случае отказа хотя бы двух (например, вторых или четвертых) одноименных ячеек. В последнем случае на выходе 22 блока 20 появляется сигнал «Неисправи.мая ошибка. Если на выходе 22-«О, то на выходе элементов И 19, соответствующих отказавшим разрядам, бу ly единичные сигналы, которые на соответствующих сумматорах 23 проинвертируют ошибочные биты из числа информационных, которые поступают на входы сумматоров 23 с выходов 9 регистра 7. Если среди отказавших окажутся разряды, принадлежащие

контрольным символам, то это не повлияет на достоверность информационных символов. Положим, что разряды накопителя соответствующие первому, второму и седь

Тйому символам кодового слова,являются дефектными и находятся в состоянии «1, разряды 16 и 17 (контрольный) - в состоянии «О т.е. считанное слово будет следующим: 1100 1110 0010 1110 0001 (отказавшие разряды подчеркнуты). Для считанных информационных символов в формирователе 10 будут вычислены контрольные символы 1110 и синдром 1110-|- 0001 1111 (суммируются одноименные разряды, суммирование ведется по модулю два). На выходах блока 8 сравнения будет слово 0100 0010 0000 0001 1000 (после записи в накопитель 1 инверсного кодового слова и его считывания). На выходе 22 блока 20 «О. На входы элементов И 19 поступят соответственно следующие двоичные символы: 1111 и 0100 0010 0000 0001, на выходах 25 сумматоров 23 по модулю два - исходное информационное слово без ошибок 1000 1100 0010 1111.

Формула изобретения

1. Запоминающее устройство с исправлением ощибок, содержащее адресный блок, накопитель, коммутатор, регистр числа, блок кодирования, блок сравнения, формирователь синдрома, элемент И, группу элементов И, элемент ИЛИ, сумматоры по модулю два и блок вывода информации, причем адресные входы накопителя подключены к выходам адресного блока, входы которого являются адресным входом устройства, информационные входы накопителя подключены к выходам коммутатора, одни из информационных входов которого и входы блока кодирования объединены и являются информационным входом устройства, другие информационные входы коммутатора соединены соответственно с выходами блока кодирования и инверсными выходами регистра числа, выходы накопителя соединены с информационными входами регистра числа и одними из входов блока сравнения, другие

входы которого и входы формирователя синдрома подключены к прямым выходам регистра числа, одни из входов сумматоров по модулю два соединены с прямыми выходами регистра числа, другие входы - с выходами элементов И группы, одни из входов которых и входы элемента ИЛИ подключены к выходам формирователя синдрома, выход элемента ИЛИ подключен к одному из входов элемента И, другой вход

которого, а также управляющий вход накопителя объединены и являются управляющим входом устройства, выход элемента И подключен к управляющим входам регистра числа и коммутатора, выходы сумматоров по модулю два соединены с информационными входами блока вывода информации, выходы которого являются информационным выходом устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введен блок обнаружения неисправимых ошибок, входы которого подключены к выходам блока сравнения, а выход подключен к управляющему входу блока вывода информации и является контрольным выходом устройства, другие входы группы элементов И подключены к одним

из выходов блока сравнения.

2. Устройство по п. 1, отличающееся тем, что блок обнаружения неисправимых ошибок содержит группы элементов И, первую и вторую группы элементов ИЛИ, сумматоры по модулю два и элемент ИЛИ, причел; входы

элементов И являются входами блока, а выходы элементов И каждой группы подключены к входам соответствующих элементов ИЛИ первой группы, выходы которых соединены с первыми входами соответствующих сумматоров по модулю два, вторые входы которых подключены к выходам соответствующих элементов ИЛИ второй группы входы которых подключены к входам блока, выходы сумматоров по модулю два соединены с входами элемента ИЛИ, выход которого является выходом блока.

Составитель В. Рудаков

Редактор Н. ГорватТехред И. ВересКорректор А. Знмокосов

Заказ 595/55Тираж 590Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж-35, Раушская наб., д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

ГI

фиг.З

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1238163A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

| Запоминающее устройство с автономным контролем | 1991 |

|

SU1837363A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1725261A1 |

| КОДЕК ПОМЕХОУСТОЙЧИВОГО ЦИКЛИЧЕСКОГО КОДА | 2003 |

|

RU2251210C1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

Изобретение относится к вычислительной технике и может быть использовано при создании систем памяти на базе БИС запоминающих устройств со словарной орга25. низацией обращения. Цель изобретения - по- выщение надежности устройства. Устройство содержит накопитель 1, адресный блок 4, коммутатор 5, регистр 7 числа, блок 8 сравнения, формирователь 10 синдрома, блок 14 коррекции, элемент И 15, элемент ИЛИ 17, группу элементов И 19, блок 20 обнаружения неисправимых ощибок, сумматоры 23 по модулю два, блок 26 вывода информации. Надежность устройства повышается за счет того, что в нем исправляются ощибки в нескольких БИС, входящих в состав накопителя 1, при условии, что ошибки не принадлежат одноименным (по порядку расположения) символам, записанным в различных БИС при хранении одного слова. 1 з.п. ф-лы, 3 ил. 1 (Л с to со N3

| Экспресс-информация | |||

| Серия «Вычислительная техника, 1978, № 36, с | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Запоминающее устройство с исправлением ошибок | 1981 |

|

SU964736A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-03-15—Публикация

1985-10-14—Подача