со

со -vl

4

1

143974

Изобретение относится к вычислительной технике и предназначено для использования в комплексе полунатурного моделирования систем воздушных сигналов, в цепях связи имитаторов входных параметров реальных систем с универсальной цифровой вычислительной машиной, а также в информационно-

измерительных системах.

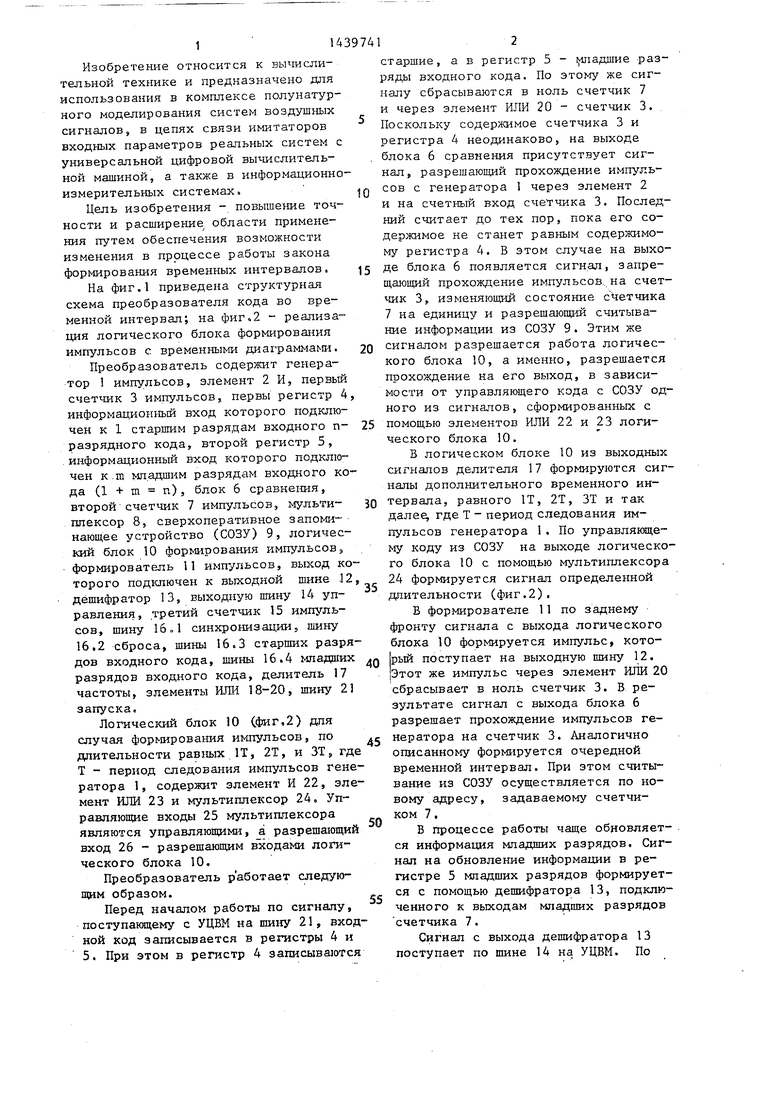

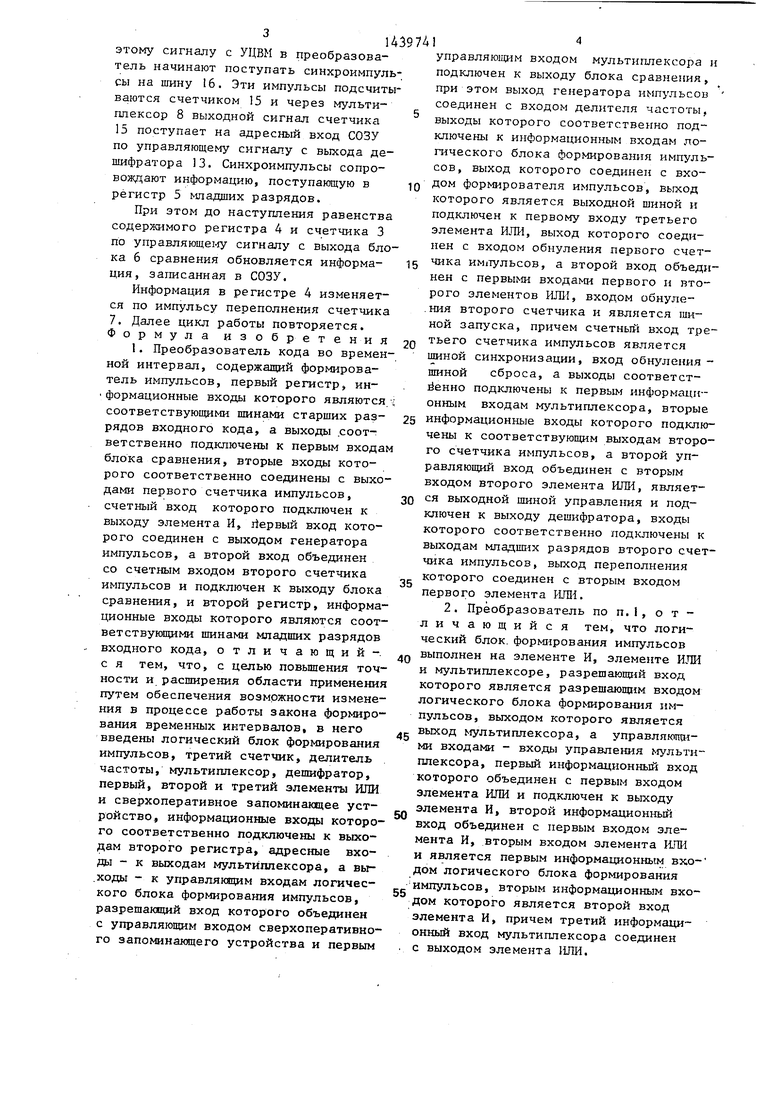

Цель изобретения - повышение точности и расширение области применения путем обеспечения возможности изменения в процессе работы закона формирования временных интервалов. На фнг.1 приведена структурная схема преобразователя кода во временной интервал; на фиг.2 - реализация логического блока формирования импульсов с временными диаграммами. Преобразователь содержит генератор 1 импульсов, элемент 2 И, первый счетчик 3 импульсов, первы регистр 4, информационный вход которого подключен к 1 старшим разрядам входного п разрядного кода, второй регистр 5, .информационный вход которого подключен к .т мп.адшим разрядам входного кода (1 + m п), блок 6 сравнения, второй счетчик 7 импульсов, мультиплексор 8, сверхоперативное запоминающее устройство (СОЗУ) 9, логический блок 10 формирования импульсов формирователь 11 импульсов, выход которого подключен к выходной шине 12 дешифратор 13, выходную шину 14 управления, третий счетчик 15 импульсов, шину 16 Л синхронизации, шину 16.2 сброса, шины 16.3 старших разрядов входного кода, шины 16.4 младших разрядов входного кода, делитель 17 частоты, элементы HJIli 18-20, шину 21 запуска.

Логический блок 10 (фиг,2) дпя случая фop шpoвaния импульсов, по длительности равных IT, 2Т, и ЗТ, где Т - период следования импульсов генератора 1, содержит элемент И 22, элемент ИЛИ 23 и мультиплексор 24. Уп- равляюш11е входы 25 мультиплексора являются управляющими, а разрешающий вход 26 - разрешаюшлм входами логического блока 10.

Преобразователь р аботает следующим образом.

Перед началом работы по сигналу, поступающему с УЦВМ на шину 21, входной код записывается в регистры 4 и 5. При этом в регистр 4 записываются

20

25

, , 1

е еей

дя

10

15

30

35

40

45

50

55

12

старшие, а в регистр 5 - 1;1ладшие разряды входного кода. По этому же сигналу сбрасываются в ноль счетчик 7 и через элемент ИЛИ 20 - счетчик 3. Поскольку содержимое счетчика 3 и регистра 4 неодинаково, на выходе блока 6 сравнения присутствует сигнал, разрешающий прохождение импульсов с генератора 1 через элемент 2 и на счетный вход счетчика 3. Последний считает до тех пор, пока его содержимое не станет равным содержимому регистра 4. В этом случае на выходе блока 6 появляется .сигнал, запрещающий прохождение импульсов., на счетчик 3, изменяюший состояние счетчика 7 на единицу и разрешаюшдй считывание информации из СОЗУ 9. Этим же сигналом разрешается работа логического блока 10, а именно, разрешается прохождение на его выход, в зависимости от управляющего кода с СОЗУ одного из сигналов, сформированных с помощью элементов ИЛИ 22 и 23 логического блока 10.

В логическом блоке 10 из выходных сигналов делителя 17 формируются сигналы дополнительного временного интервала, равного IT, 2Т, ЗТ и так далее, где Т - период следования импульсов генератора 1. По управлянще- му коду из СОЗУ на выходе логического блока 10 с помощью мультиплексора 24 формируется сигнал определенной длительности (фиг.2).

В формирователе 11 по заднему фронту сигнала с выхода логического блока 10 формируется импульс, который поступает на выходную шину 12. Этот же импульс через элемент ИЛИ 20 сбрасывает в ноль счетчик 3. В результате сигнал с выхода блока 6 разрешает прохождение импульсов генератора на счетчик 3. Аналогично описанному формируется очередной временной интервал. При этом считывание из СОЗУ осуществляется по новому адресу, задаваемому счетчиком 7.

В процессе работы чаще обновляется информация младших разрядов. Сигнал на обновление информации в регистре 5 младших разрядов формируется с помощью дешифратора 13, подключенного к выходам младших разрядов счетчика 7.

Сигнал с выхода дешифратора 13 поступает по щине 14 на УЦВМ. По

14397А

этому сигналу с УЦВМ в преобразователь начинают поступать синхроимпульсы на шину 16. Эти импульсы подсчитываются счетчиком 15 и через мультиплексор 8 выходной сигнал счетчика 15 поступает на адресный вход СОЗУ по управляющему сигналу с выхода дешифратора 13. Синхроимпульсы сопровождают информацию, поступающую в ю регистр 5 младших разрядов.

При этом до наступления равенства содержимого регистра 4 и счетчика 3 по управляюще1-1у сигналу с выхода блока 6 сравнения обновляется информа- 15 ция, записанная в СОЗУ.

Информация в регистре 4 изменяется по импульсу переполнения счетчика 7. Далее цикл работы повторяется. ормула изобретения 20

1. Преобразователь кода во временой интервал, содержащий формирователь импульсов, первый регистр, ин- ормационные входы которого являются ; соответствующими шинами старших раз- 25 ядов входного кода, а выходы .соответственно подключены к первым входам лока сравнения, вторые входы котоого соответственно соединены с выхоами первого счетчика импульсов, Q счетный вход которого подключен к выходу элемента И, йервый вход котоого соединен с выходом генератора мпульсов, а второй вход объединен со счетным входом второго счетчика импульсов и подключен к выходу блока сравнения, и второй регистр, информационные входы которого являются соот- ветствукнцими шинами младших разрядов входного кода, отличающий-. с я тем, что, с целью повьшгения точности и расширения области применения путем обеспечения возможности изменения в процессе работы закона формирования временных интервалов, в него введены логический блок формирования импульсов, третий счетчик, делитель частоты, мультиплексор, дешифратор, первый, второй и третий элементы ИЛИ и сверхоперативное запоминающее устройство, информационные входы которого соответственно подключены к выходам второго регистра, адресные вхо- дь: - к выходам мультиплексора, а вы- ходы - к управляющим входам логического блока формирования импульсов, разрешающий вход которого объединен с управляющим входом сверхоперативного запоминакнцего устройства и первым

35

50

55

5

0

5 Q

5

0

5

1

управляю1цим входом мультиплексора н подключен к выходу блока сравнения, при этом выход генератора импульсов соединен с входом делителя частоты, выходы которого соответственно подключены к информационным входам логического блока формирования импульсов, выход которого соединен с входом формирователя импульсов, выход которого является выходной шиной и подключен к первому входу третьего элемента ИЛИ, выход которого соединен с входом обнуления первого счетчика им1тульсов, а второй вход объединен с первыми входами первого и второго элементов ИЛИ, входом обнуле- .ния второго счетчика и является шиной запуска, причем счетньш вход третьего счетчика импульсов является шиной синхронизации, вход обнуления - шиной сброса, а выходы соответственно подключены к первым информационным входам мультиплексора, вторые информационные входы которого подключены к соответствующим выходам второго счетчика импульсов, а второй управляющий вход объединен с вторым входом второго элемента ИЛИ, является выходной шиной управления и подключен к выходу дешифратора, входы которого соответственно подключены к выходам младших разрядов второго счетчика импульсов, выход переполнения которого соединен с вторым входом первого элемента UTIli.

2. Преобразователь по п.1, о т - личающийся тем, что логический блок, формирования импульсов выполнен на элементе И, элементе ИТМ и мультиплексоре, разрешающий вход которого является разрешающим входом логического блока формирования импульсов, выходом которого является выход мультиплексора, а управляющими входами - входы управления мультиплексора, первый информационньй вход которого объединен с первым входом элемента ИЛИ и подключен к выходу элемента И, второй информационный вход объединен с первым входом элемента И, вторым входом элемента ИЛИ и является первым информационным вхо- дом логического блока формирования импульсов, вторым информационным входом которого является второй вход элемента И, причем третий информационный вход мультиплексора соединен с выходом элемента ИЛИ.

le.i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1989 |

|

SU1695314A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Преобразователь кода во временной интервал | 1987 |

|

SU1478335A1 |

| Программно-управляемый цифровой фильтр | 1987 |

|

SU1513475A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1985 |

|

SU1307462A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Устройство для отображения информации на экране телевизионного приемника | 1984 |

|

SU1265834A1 |

| Многоканальное устройство для ввода информации | 1988 |

|

SU1536369A1 |

Изобретение относится к вычислительной технике и может быть использовано в информационно-измерительных системах и моделирующих комплексах. Цель изобретения - повьшение точности и расширение области применения за счет возможности изменения в процессе работы закона формирования временных интервалов. Поставленная цель достигается путем введения в преобразователь сверхоперативного запоминающего устройства (СОЗУ), логического блока формирования импульсов, делителя частоты, дешифратора, третьего счетчика импульсов и мультиплексора. С помощью первого регистра, первого счетчика и блока сравнения формируется грубый временной интервал, который с помощью второго регистра, СОЗУ, логического блока формирования изменяется в. соответствии с изменением задаваемого кода. 1 з.п. ф-лы, § 2 ил. SS (Л

4

2J

70

26

4

К If

| Горелик А.Л | |||

| и др | |||

| Бортовые ЦВМ | |||

| М., 1975, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Преобразователь кода во временной интервал | 1984 |

|

SU1221756A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-11-23—Публикация

1986-07-07—Подача