Изобретение относится к вычислительной технике и может быть применено при создании устройств с ЭСЛ- элементами.

Цель изобретения - повышение надежности.

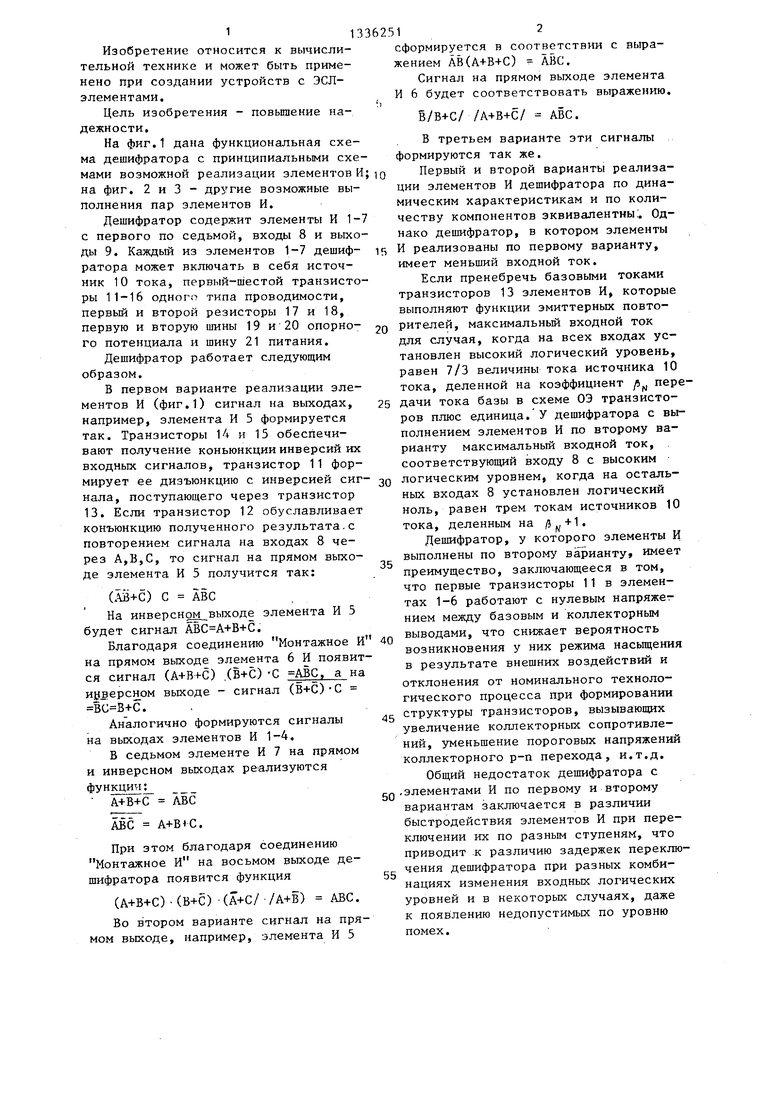

На фиг.1 дана функциональная схема дешифратора с принципиальными схесформируется в соответствии с выражением АВ(А+В+С) - ABC.

Сигнал на прямом выходе элемента И 6 будет соответствовать выражению.

В/В+С/ /А+В+С/ ABC.

В третьем варианте эти сигналы формируются так же.

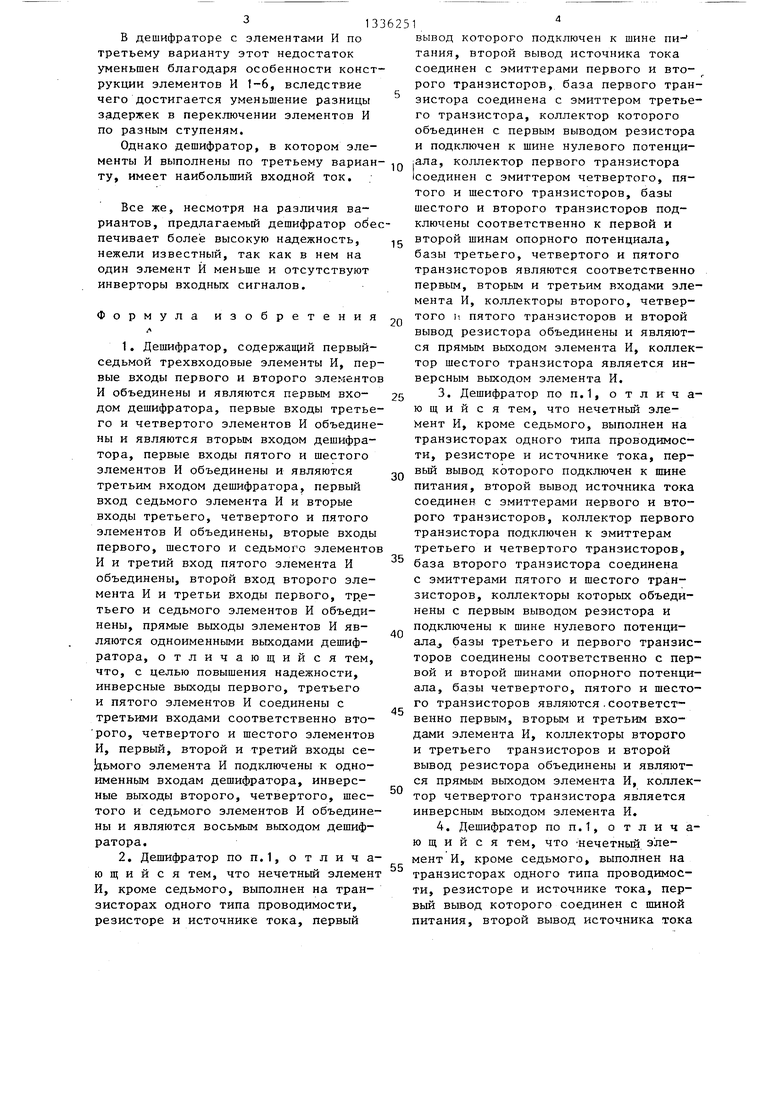

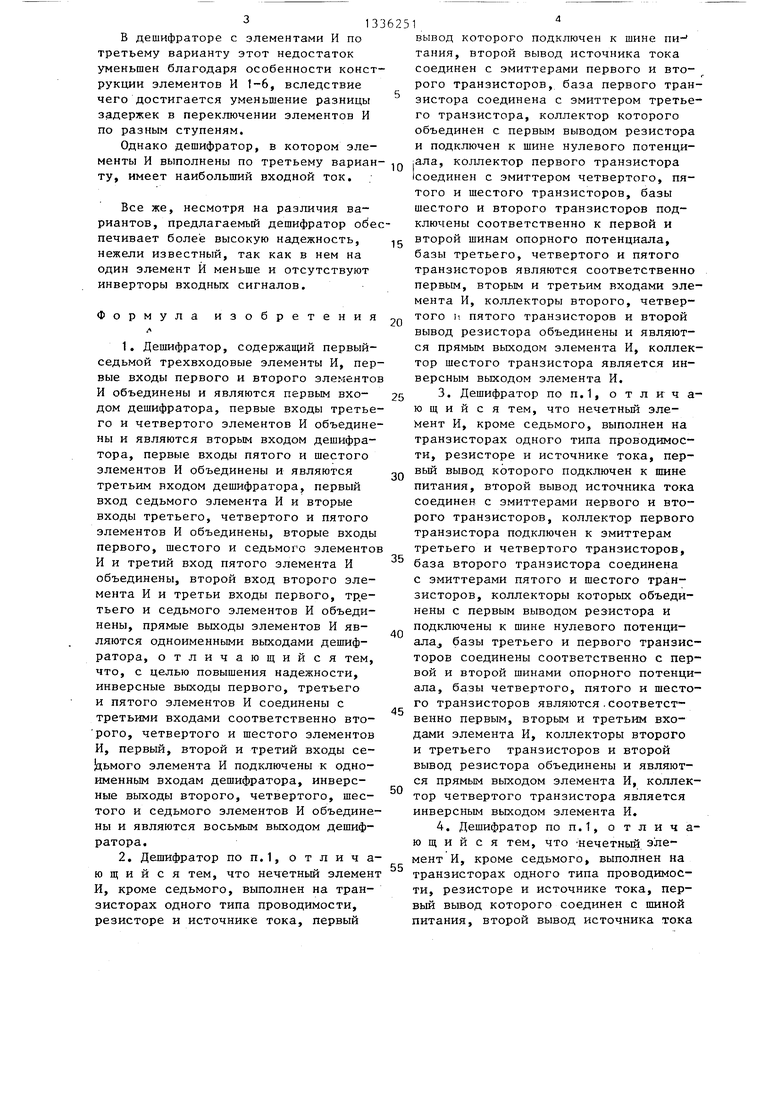

мами возможной реализации элементов И; ю Первый и второй варианты реализа- на фиг, 2 и 3 - другие возможные вы- ции элементов И дешифратора по динаполнения пар элементов И,

Дешифратор содержит элементы И 1-7 с первого по седьмой, входы 8 и выходы 9, Каждый из элементов 1-7 дешифратора может включать в себя источник 10 тока, первый-шестой транзисторы 11-16 одного типа проводимости, первый и второй резисторы 17 и 18, первую и вторую шины 19 и 20 опорного потенциала и шину 21 питания.

Дешифратор работает следующим образом,

В первом варианте реализации элементов И (фиг,1) сигнал на выходах, например, элемента И 5 формируется так. Транзисторы 14 и 15 обеспечивают получение коньюнкции инверсий их входных сигналов, транзистор 11 формирует ее дизъюнкцию с инверсией сиг- о логическим уровнем, когда на остальных входах 8 установлен логический ноль, равен трем токам источников 10 тока, деленным на ,

нала, поступающего через транзистор 13, Если транзистор 12 обуславливает конъюнкцию полученного результата.с повторением сигнала на входах 8 через А,Б,С, то сигнал на прямом выходе элемента И 5 получится так:

Дешифратор, у которого элементы выполнены по второму варианту, име преимущество, заключающееся в том что первые транзисторы 11 в элемен тах 1-6 работают с нулевым напряж нием между базовым и коллекторным

) С ABC

На инверснд1М выходе элемента И 5

будет сигнал АВС А+В+С,выводами, что снижает вероятность

Влагодаря соединению Монтажное И 40 на прямом выходе элемента 6 И появится сигнал (А+В+С) .(В+С) С АВС, а на

возникновения у них режима нacьш e в результате внешних воздействий отклонения от номинального техноло гического процесса при формировани дс структуры транзисторов, вызывающих увеличение коллекторных сопротивле ний, уменьшение пороговых напряжен коллекторного р-п перехода, и.т.д. Общий недостаток дешифратора с элементами И по первому и второму вариантам заключается в различии быстродействия элементов И при пер ключении их по разным ступеням, чт приводит к различию задержек перек чения дешифратора при разных комби нациях изменения входных логически уровней и в некоторых случаях, даж к появлению недопустимых по уровню помех.

инверсном выходе - сигнал (В+С)С ,

Аналогично формируются сигналы на выходах элементов И 1-4,

Б седьмом элементе И 7 на прямом и инверсном выходах реализуются функции; ЛВС

ABC ,

При этом благодаря соединению Монтажное И на восьмом выходе дешифратора появится функция

(А+В+С)(В+С) -(А+С/7А+В) ABC.

Во втором варианте сигнал на прямом выходе, например, элемента И 5

сформируется в соответствии с выражением АВ(А+В+С) - ABC.

Сигнал на прямом выходе элемента И 6 будет соответствовать выражению.

В/В+С/ /А+В+С/ ABC.

мическим характеристикам и по количеству компонентов эквивалентны:. Однако дешифратор, в котором элементы

И реализованы по первому варианту, имеет меньший входной ток.

Если пренебречь базовыми токами транзисторов 13 элементов И, которые выполняют функции эмиттерных повторителей, максимальный входной ток для случая, когда на всех входах установлен высокий логический уровень, равен 7/3 величины тока источника 10 тока, деленной на коэффициент передачи тока базы в схеме ОЭ транзисторов плюс единица, У дешифратора с выполнением элементов И п.о второму варианту максимальный входной ток, соответствующий входу 8 с высоким

логическим уровнем, когда на осталь

ных входах 8 установлен логический ноль, равен трем токам источников 10 тока, деленным на ,

Дешифратор, у которого элементы И выполнены по второму варианту, имеет преимущество, заключающееся в том, что первые транзисторы 11 в элементах 1-6 работают с нулевым напряжением между базовым и коллекторным

выводами, что снижает вероятность

возникновения у них режима нacьш eния в результате внешних воздействий и отклонения от номинального технологического процесса при формировании структуры транзисторов, вызывающих увеличение коллекторных сопротивлений, уменьшение пороговых напряжений коллекторного р-п перехода, и.т.д. Общий недостаток дешифратора с элементами И по первому и второму вариантам заключается в различии быстродействия элементов И при переключении их по разным ступеням, что приводит к различию задержек переключения дешифратора при разных комбинациях изменения входных логических уровней и в некоторых случаях, даже к появлению недопустимых по уровню помех.

3133

В дешифраторе с элементами И по третьему варианту этот недостаток уменьшен благодаря особенности конструкции элементов И 1-6, вследствие чего достигается уменьшение разницы задержек в переключении элементов И по разным ступеням.

Однако дешифратор, в котором элементы И выполнены по третьему варианту, имеет наибольший входной ток.

Все же, несмотря на различия вариантов, предлагаемый дешифратор обеспечивает более высокую надежность, g нежели известный, так как в нем на один элемент И меньше и отсутствуют инверторы входных сигналов.

Формула изобретения

А

1.Дешифратор, содержащий первый- седьмой трехвходовые элементы И, первые входы первого и второго элементов И обьединены и являются первым входом дешифратора, первые входы третьего и четвертого элементов И объединены и являются вторым входом дешифратора, первые входы пятого и шестого элементов И объединены и являются третьим входом дешифратора, первый вход седьмого элемента И и вторые входы третьего, четвертого и пятого элементов И объединены, вторые входы первого, шестого и седьмого элементов И и третий вход пятого элемента И объединены, второй вход второго элемента И и третьи входы первого, тр,е- тьего и седьмого элементов И объединены, прямые выходы элементов И являются одноименными выходами дешифратора, отличающийся тем, что, с целью повышения надежности, инверсные выходы первого, третьего

и пятого элементов И соединены с третьими входами соответственно вто- рого, четвертого и шестого элементов И, первый, второй и третий входы се- hbMoro элемента И подключены к одноименным входам дешифратора, инверсные выходы второго, четвертого, шестого и седьмого элементов И объединены и являются восьмым выходом дешифратора.

2.Дешифратор по п.1, отличающийся тем, что нечетный элемент И, кроме седьмого, выполнен на транзисторах одного типа проводимости, резисторе и источнике тока, первый

0

g

0

5

0

35

0

45

50

55

вывод которого подключен к шине пи- тания, второй вывод источника тока соединен с эмиттерами первого и второго транзисторов, база первого транзистора соединена с эмиттером третьего транзистора, коллектор которого объединен с первым выводом резистора и подключен к шине нулевого потенциала, коллектор первого транзистора соединен с эмиттером четвертого, пятого и шестого транзисторов, баэы шестого и второго транзисторов подключены соответственно к первой и второй шинам опорного потенциала, базы третьего, четвертого и пятого транзисторов являются соответственно первым, вторым и третьим входами элемента И, коллекторы второго, четвертого 1 пятого транзисторов и второй вывод резистора объединены и являются прямым выходом элемента И, коллектор шестого транзистора является инверсным выходом элемента И.

3.Дешифратор по п.1, отличающийся тем, что нечетньй элемент И, кроме седьмого, выполнен на транзисторах одного типа проводимости, резисторе и источнике тока, пер- вьй вывод которого подключен к шине питания, второй вывод источника тока соединен с эмиттерами первого и второго транзисторов, коллектор первого транзистора подключен к эмиттерам третьего и четвертого транзисторов, база второго транзистора соединена

с эмиттерами пятого и шестого транзисторов, коллекторы которых объединены с первым выводом резистора и подключены к шине нулевого потенци- aлaJ базы третьего и первого транзисторов соединены соответственно с первой и второй шинами опорного потенциала, базы четвертого, пятого и шестого транзисторов являются.соответственно первым, вторым и третьим входами элемента И, коллекторы второго и третьего транзисторов и второй вывод резистора объединены и являются прямым выходом элемента И, коллектор четвертого транзистора является инверсным выходом элемента И.

4.Дешифратор по п.1, отличающийся тем, что Нечетный элемент И, кроме седьмого, выполнен на транзисторах одного типа проводимости, резисторе и источнике тока, первый вывод которого соединен с шиной питания, второй вывод источника тока

Соединен с эмиттерами первого и второго транзисторов, коллектор первого транзистора подключен к эмиттерам третьего и четвертого транзисторов, коллектор и база второго транзистора объединены и подключены к эмиттерам пятого и шестого транзисторов, первый вывод резистора соединен с шиной нулевого потенциала, базы третьего- и первого транзисторов подключены соответственно к первой и второй шинам опорного потенциала, базы четвертого, пятого и шестого транзисторов являются соответственно первым, вторы и третьим входами элемента И, коллекто ры третьего, пятого и шестого транзисторов и второй вывод резистора объединены и являются выходом элемента И, коллектор четвертого транзис- тора является инверсным выходом элемента И.

5.Дешифратор поп.1, отличающийся тем, что четньш элемент

И выполнен на транзисторах одного типа проводимости, резисторе и источнике тока, первый вывод которого подключен к шине питания, второй вывод источника тока соединен с эмиттерами первого и второго транзисторов, база первого транзистора подключена к эмиттеру третьего транзистора, коллектор которого и первый вывод резистора объединены и подключены к шине нулевого потенциала, коллектор первого транзистора соединен с эмиттерами четвертого и пятого транзисторов, базы пятого и второго транзисторов подключены соответственно к первой и второй шинам опорного потенциала, базы третьего и четвертого транзисторов являются соответственно первым и вторым входами элемента И, коллекторы второго и четвертого транзисторов и второй вывод резистора объединены и. являются третьим входом и пря- ,мым вькодом элемента И, коллектор пятого транзистора является инверсным выходом элемента И.

6.Дешифратор по п.1, отличающийся тем, что четный элемент

И выполнен на транзисторах одного типа проводимости, резисторе и источнике тока, первый вывод которого подключен к шине питания, второй вывод источника тока соединен с эмиттерами первого и второго транзисторов,, коллектор первого транзистора подключен к эмиттерам третьего и четвертого

0

g п

5

0

35

0

5

0

5

транзисторов,.база второго транзистора соединена с змитте ром пятого транзистора, коллектор которого и первый вывод резистора объединены и подключены к шине нулевого потенциала, базы третьего и первого транзисторов подключены соответственно к первой и второй шинам опорного потенциала, базы четвертого и пятого транзисторов являются соответственно первым и вторьм входами элемента И, коллекторы второго и третьего транзисторов и второй вывод резистора объединены и являются третьим входом и прямым выходом элемента И, коллектор четвертого транзистора является инверсным выходом элемента И.

7,Дешифратор поп,1, отличающийся тем, что четньй элемент

И выполнен на транзисторах одного типа проводимости, резисторе и источнике тока, первый вывод которого подключен к шине питания, второй вывод источника тока соединен с эмиттерами первого и второго транзисторов, коллектор первого транзистора подключен к эмиттерам третьего и четвертого транзисторов, коллектор и база второго транзистора объединены и подключены к эмиттеру пятого транзистора, первый вывод резистора соединен с шиной нулевого потенциала, базы третьего и первого транзисторов подключены соответственно к первой и второй шинам опорного потенциала, базы четвертого и пятого транзисторов являются соответственно первым и вторым входами элемента И, коллекторы третьего и пятого транзисторов и второй вывод резистора объединены и являются третьим входом и прямым выходом элемента И, коллектор четвертого транзистора является инверсным выходом элемента И.

8,Дешифратор по п.1, отличающийся тем, что седьмой элемент И выполнен на транзисторах одного типа проводимости, резисторах и источ,нике тока, первый вывод которого подключен к шине питания, второй вывод источника тока соединен с эмиттерами первого и второго транзисторов, база первого транзистора подключена к эмиттерам третьего, четвертого и пятого транзисторов, коллекторы которых и первые выводы резисторов объединены и подключены к шине -нулевого потенциала, база второго транзистора

Г3362518

подключена к второй шине опорного вод первого резистора объединены и потенциала, базы, третьего, четвертого и пятого транзисторов являются соответственно первым,.вторым, и третьим входами элемента И, коллектор первого транзистора и второй выявляются прямым выходом элемента И коллектор второго транзистора и вт рой вывод второго резистора объедин ны и являются инверсным выходом эле мента И.

вод первого резистора объединены и

являются прямым выходом элемента И, коллектор второго транзистора и втог рой вывод второго резистора объединены и являются инверсным выходом элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Пересчетная декада | 1983 |

|

SU1112574A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Дешифратор запоминаюшего устройства | 1979 |

|

SU871330A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| Пересчетная декада | 1982 |

|

SU1064478A1 |

| Логический элемент "исключительное ИЛИ | 1982 |

|

SU1045397A1 |

| Десятичное счетно-индикаторное устройство | 1982 |

|

SU1078628A1 |

| Преобразователь двоичного кода в биполярный код | 1984 |

|

SU1249706A1 |

| Дешифратор адреса | 1988 |

|

SU1608745A1 |

Изобретение относится к вычислительной технике. Его применение при создании устройств с ЭСЛ-элемен- тами позволяет повысить надежность. Дешифратор содержит элементы И 1-7,, Благодаря специфическим соединениям этих элементов уменьшено их число по сравнению с прототипом и исключены инверторы входных сигналов. 7 з.п. ф-лы, 3 ил. (Л с

Составитель О.Ревинский Редактор Н.Егорова Техред И.Попович Корректор С.Шекмар

Заказ 4055/56 Тираж 901 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва: Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Трехвходовой дешифратор | 1974 |

|

SU517155A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Шляпоберский В.И | |||

| Основы техники передачи дискретных сообщений.- М.: Связь, 1973, с.144, рис.3.34 | |||

Авторы

Даты

1987-09-07—Публикация

1986-01-02—Подача