(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БОЛЬШИХ ИНТЕГРАЛЬНЫХ СХЕМ ПАМЯТИ

I

Изобретение относится к области запоминающих устройств.

Известно устройство для контроля больших интегральных схем памяти, которое содержит блок управления, формирователи управляющих сигналов, блоки считывания и лотические элементы 1.

Недостатком известного устройства являются большие аппаратурные затраты.

Наиболее близким к предлагаемому является устройство для контроля больших интегральных схем памяти, содержащее программное устройство, выход которого соединен с первым входом управления, задающий генератор; выход которого соединен со вторым входом схемы управления, первый выход которой соединен с первым входом регистра данных и входом регистра адреса, выход которого соединен с информашюнным входом формирователя сигналов адреса, а первый выход регистра данных, второй и третий выходы схемы управления соединены с первыми входами формирователей данных, строба и управляющих сигналов, а выход .формирователя стрюба соединен с, первым входом регистра приема данных, выход которого соединен с регистром данных, второй выход которого соединен с третьим входом схемы управления, а второй вход регистра приема данных соединен с выходом компаратора, вход которого подключен к выводу контролируемой большой интегральной схемы (БИС) памяти, а остальные выводы контролируемой БИС памяти подключены к соответствующим выходам преобразователей уровней сигналов, входы которых соединены с выходами формирователей данных, управления и адреса 2.

Недостатком данного устройства является отсутствие программируемой схемы синхронизации, что С1шжает область применения уст15ройства.

Цель изобретения - повышение быстродействия и расширение области применения устройства за счет обеспечения возможности программирования контроля.

20

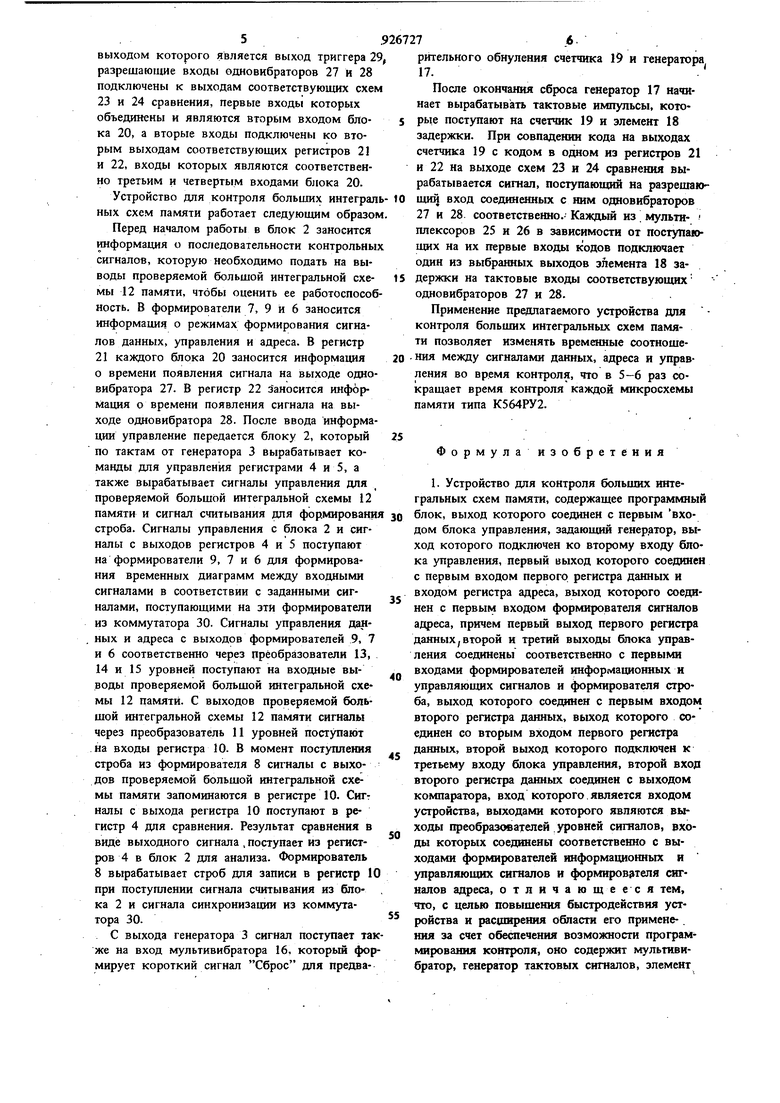

Поставленная цель достигается тем, что в устройство для контроля больших интегральных схема памяти, содержащее программный блок, выход которого соединен с первым вхо 39 дом блока управления, задающий генератор, выход которого подключен ко второму входу блока управления, первый выход которого соединен с первым входом первого регистра данных и входом регистра адреса, выход которого соединен с первым входом формирователя сигналов адреса, причем первый выход первого регистра данных, второй и третий выходы блока управления соединены соответ1Ственно с первыми входами формирователей информационных и управляющих сигналов и формирователя строба, выход которого соединен с первым входом второго регистра данных, выход которого соединен со вторым вхо дом первого регистра данных, второй выход которого подключен к третьему входу блока управления, второй вход второго регистра дан ных. Соединен с выходом компаратора, вход которого является входом устройства, выхода ми которого являются выходы преобразователей уровней сигналов, входы которых соедине ны соответственно с выходами формирователе информационных и управляющих сигналов и формирователя сигналов адреса, введены муль тивибратор, генератор тактовых сигналов, элемент задержки, счетчик тактов, коммутатор и логические блоки, причем вход мультивибратора соединен с входом задающего генератора а выход - со входом генератора тактовых сигналов и первым входом счетчика тактов, второй вход которого подключен к выходу генератора тактовых сигналов и выходу элемента задержки, входы логических блоков по ключены соответственно к выходам элемента задержки и счетчика тактов и к четвертому и пятому выходам блока управления, а выходы - ко входам коммутатора, выхоДы которого соединены со вторыми входами формирователей управляющих и информащюнных бигналов, формирователя строба и формирователя сигналов адреса. При этом каждый логический, блок целесоо разно выполнить в виде блока, содержащего р гистры, схемы сравнения, мультиплексоры, одновибраторы и триггер, причем первые входы мульхшшексоров объединены, и являются первым входом логического блока, вторые входы соединены с первыми выходами соответствумцдах регистров, а выходы - с тактовыми входами соответствующих одновибраторов, выходы которых соединены со входами триггера и являются одними из выходов логического блока, другим выходом которого является выход триггера, разрещающие входы одаовибраторов подключены к выходам соответствуюших схем сравнения, первые входы которых объединены и являются вторым входом логического блока, а вторые входы подключены ко вторым выходам соответствующих регистров, входы которых являются соответственно третьим и четвертым входами логического блока. На чертеже изображена структурная схема предлагаемого устройства, содержащая, например, два логических блока. Устройство содержит программный блок 1, выход которого соединен с первым входом блока 2 управления, задающий генератор 3, выход которого соединен со вторым входом блока 2, первый выход которого соединен с первым входом первого регистра 4 данных и входом регистра 5 адреса, выход которого соединен с первым входом формирователя 6 сигналов адреса, а первый выход регистра 4 данных, второй и третий выходы блока 2 управления соединены соответственно с первыми входами формирователей информационных сигналов 7, строба 8 и управляющих сигналов 9, а выход формирователя .8 строба соединен с первым входом второго регистра 10 данных, выход которого соединен со вторым входом регистра 5, второй выход которого соединен с третьим входом блока 2 управления, а второй вход регистра 10 соединен с выходом компаратора II, вход которого подключен к выводу контролируемой больщой интегральной схемы 12 памяти, остальные выводы которой подключены к соответствующим выходам преобразователей уровней сигналов 13, 14 и 15 , входы которых соединены соответственно с выходами формирователей 7, 9 и 6. Устройство также содержит мультивибратор 16, генератор 17 тактовых сигналов, элемент 18 задержки, счетчик 19 тактов, логические блоки 20, каждый из которых содержит регистры 21 и 22, схемы 23 и 24 сравнения, мультиплексоры 25 и 26 и одновибраторы 27 и 28 и триггер 29. Устройство также содержит коммутатор 30., Вход мультивибратора 16 соединен с выходом генератора 3, а выход - со входом генератора 17 и первым входом счетчика 19, второй вход которого подключен к выходу генератора 17 и входу элемента 18 задержки. Входы блоков 20 подключены соответс венно к выходам элемента 18 .задержки и .счетчика 19 и четвертому и пятому выходам блока 2, а выходы - ко входам коммутатора 30, выходы которого соединены со вторыми входами формирователей 6-9. В каждом логическом блоке первые входы мультиплексоров 25 и 26 объединены и являются первым входом блока 20, вторые входы соединены с первыми выходами соответствующих регистров 21 и 22, а выходы - с тактовыми входами соответству ющих одновибраторов 27 и 28, выходы которых соеданены со входами триггера 29 и являются одними из выходов блока 20, другим выходом которого является выход триггера 2 разрешающие входы одновибраторов 27 и 28 подключены к выходам соответствующих схем 23 и 24 сравнения, первые входы которых объединены и являются вторым входом блока 20, а вторые входы подключены ко вторым выходам соответствующих регистров 21 и 22, входы которых являются соответственно третьим и четвертым входами блока 20. Устройство для контроля больщих интеграл ных схем памяти работает следующим образом Перед началом работы в блок 2 заносится информация о последовательности контрольны сигналов, которую необходимо подать на выводы проверяемой большой интегральной схемы 12 памяти, чтобы оценить ее работоспособ ность. В формирователи 7, 9 и 6 заносится информация о режимах формирования сигналов данных, управления и адреса. В регистр 21 каждого блока 20 заносится информация о времени появления сигнала на выходе одновибратора 27. В регистр 22 заносится информащ1я о времени появления сигнала на выходе одновибратора 28. После ввода информации управление передается блоку 2, который по тактам от генератора 3 вырабатывает команды для управления регистрами 4 и 5, а также вырабатывает сигналы управления для проверяемой большой интегральной схемы 12 памяти и сигнал считывания дпя формировани строба. Сигналы управления с блока 2 и сигналы с выходов регистров 4 и 5 поступают на формирователи 9, 7 и 6 для формирования временных диаграмм между входными сигналами в соответствии с заданными сигналами, поступающими на эти формирователи из коммутатора 30. Сигналы управления данных и адреса с выходов формирователей 9, 7 и 6 соответственно через преобразователи 13, 14 и 15 уровней поступают на входные выводы проверяемой большой интегральной схемы 12 памяти. С выходов проверяемой большой интегральной схемы 12 памяти сигналы через преобразователь 11 уровней поступают на входы регистра 10. В момент поступления строба из формирователя 8 сигналы с выходов проверяемой большой интегральной схемы памяти запоминаются в регистре 10. Сигт налы с выхода регистра 10 поступают в регистр 4 для сравнения. Результат сравнения в виде выходного сигнала , поступает из регистров 4 в блок 2 для анализа. Формирователь 8 вырабатывает строб для записи в регистр 10 при поступлении сигнала считывания из блока 2 и сигнала синхронизации из коммутатора 30. . С выхода генератора 3 сигнал поступает так же на вход мультивибратора 16, который фор мирует короткий сигнал Сброс для предварительного обнуления счетчика 19 и генератора 17.. После окончания сброса генератор 17 начинает вырабатывать тактовые импульсы, котоpbie поступают на счетчик 19 и элемент 18 задержки. При совпадении кода на выходах счетчика 19 с кодом в одном из регистров 21 и 22 на выходе схем 23 и 24 сравнения вырабатывается сигнал, поступающий на разрешающий вход соединенных с ним одаовибраторов 27 и 28 соответственно. Каждый из мультиплексоров 25 и 26 в зависимости от поступающих на их первые входы кодов подключает один из выбранных выходов элемента 18 задержки на тактовые входы соответствующих одновибраторов 27 и 28.. Применение предлагаемого устройства для контроля больших интегральных схем памяти позволяет изменять временные соотношения между сигналами данных, адреса и управления во время контроля, тто в 5-6 раз сокращает время контроля каждой микросхемы памяти типа К564РУ2. Формулаизобретения 1. Устройство для контроля больших интегральных схем памяти, содержащее программный блок, выход которого соединен с первым входом блока управления, задающий генератор, выход которого подключен ко второму входу блока управления, первый выход которого соединен с первым входом первого регистра данных и входом регистра адреса, выход которого соединен с первым входом формирователя сигналов адреса, причем первый выход первого регистра данных,второй и третий выходы блока управления соединены соответственно с первыми входами форми|ювателей информационных и управляющих сигналов и формирователя строба, выход которого соедашен с первым входом второго регистра данных, выход которого соединен со вторым входом первого регистра данных, второй выход которого подключен к третьему входу блока управления, второй вход второго регистра данных соединен с выходом компаратора, вход которого является входом устройства, выходами которого являются выходы преобразователей уровней сигналов, входы которых соединены соответственно с выходами формирователей информационных и управляющих сигналов и формирователя сигналов адреса, отличающееся тем, что, с целью повышения быстродействия устройства и расишреиия области его примене-. ния за счет обеспечения возможности программирования контроля, оно содержит мультивибратор, генератор тактовых сигналов, элемент

задержки, счетчик тактов, коммутатор и логические блоки, причем вход мультивибратора соединен с выходом задающего геиератора а выход - со входом генератора тактовых сигналов и первым входом счетчика тактов, второй вход которого подключен к выходу генератора тактовых сигналов и к выходу элмента задержки, входы логических блоков подключены соответственно к выходам элемента задержки и счетчика тактов и к четвертому и пятому выходам блока управления, а выходы - ко входам коммутатора, выходы которого соединены со вторыми входами формирователей управляющих и информационных сигналов, формирователя строба и формирователя сигналов адреса.

2. Устройство по п. 1, о т л и ч а ю щ ее с я тем, что казкдый логический блок содержит регистры, схемы сравнения, мультиплексоры, одновибраторы и триггер, причем первые входы мультиплексоров объединены

И являются. первым входом логического блока, вторые входы соединены с первыми выходами соответствующих регистрюв, а выходы - с тактовыми входами соответствующих одновибраторов, выходы которых соединены со входами триггера и являются одними из вы ходов логического блока, другим выходом которого является выход триггера, разрещающие входы одновибраторов подключены к выходам соответствующих схем сравнения, первые входы которых объединены и являются вторым входом логического блока, а вторые входы подключены ко вторым выходам соответствующих регистров, входы которых являются соответственно третьим и четвертым входами логического блока.

Источники информащти, принятые во внимание цри экспертизе 1. Патент Японии № 48-41739, кл. 97(7) G 01, опублик. 1973.

2; Патент США N 3751649, кл. 235-153, опублик. 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля больших интегральных схем памяти | 1984 |

|

SU1179375A1 |

| Устройство для ввода в микроЭВМ дискретных сигналов | 1988 |

|

SU1608679A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| Устройство микропрограммного управления | 1989 |

|

SU1786486A1 |

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| Устройство для контроля микропроцессорных цифровых блоков | 1986 |

|

SU1383364A1 |

| СИСТЕМА ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ | 1993 |

|

RU2072546C1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

Авторы

Даты

1982-05-07—Публикация

1980-06-19—Подача