Изобретение относится к контрольно-испытательной технике и может быть использовано для функционального контроля больших интегральных схем (БИС), имеющих выходы с третьим состоянием.

Цель изобретения - расширение функциональных возможностей за счет возможности контроля третьего состо яния„

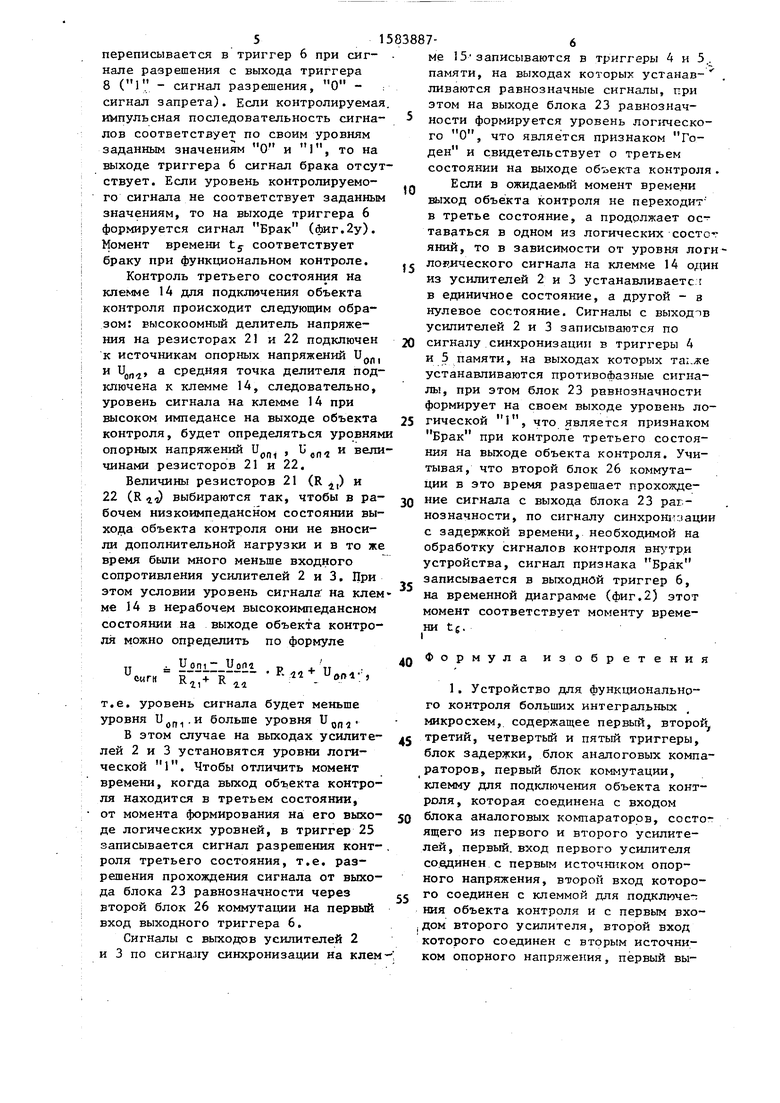

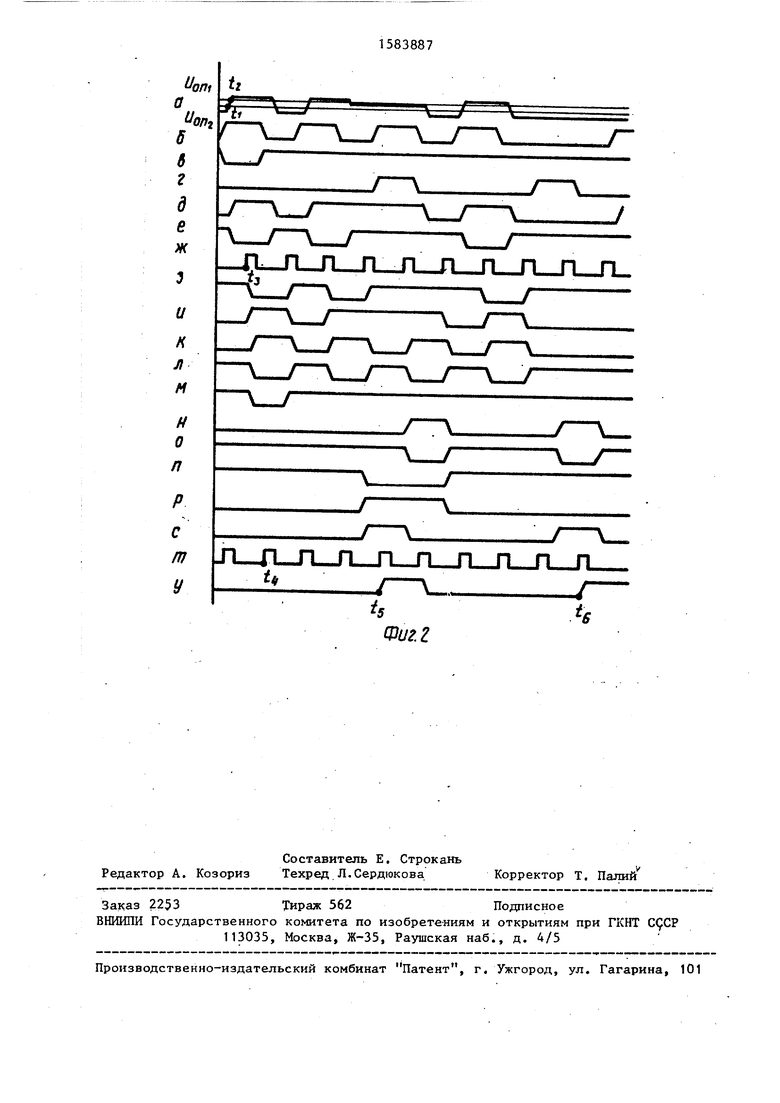

На фиг.1 изображена функциональная схема устройства; на фиг.2 - временные диаграммы.

Устройство (фиг.1) содержит блок 1 аналоговых компараторов, операционные усилители 2 и 3, D-триггеры 4 и 5 памяти, выходной D-тритгер 6, D-триггеры 7 и 8, блок 9 задержки, первый блок 10 коммутации, в состав которого входят логические элементы И-НЕ 11 «, И-НЕ 12, ИЛИ-НЕ 13, клемму 14 для подключения объек- та контроля, входные клеммы 15-17, выходную клемму J8, ;кдеммы J9 и 20 для подключения источников опорных напряжений, резисторы 21 и 22, блок 23 равнозначности, входную клемму 24 D-триггер 25, второй блок 26

коммутации, в состав которого вхо-- дят элементы И-НЕ 27 и 28, ИЛИ-НЕ 29 .Источники опорных напряжений U,

от и Uonaслужат для задания уровней

опорных напряжений логических 1 и О соответственно. Входная клем- ма 15 служит для подключения сигнала Строб-импульс.

Входная клемма 16 служит для подключения источника эталонной информации. Входная клемма 17 служит для подключения источника управляющих сигналов записи-считывания информации, входная клемма 24 - для подключения источника управляющих сигналов признака третьего состояния на выходе объекта контроля, выходная клемма 18 - для подключения средств обработки информации, ложного результата контроля.

ч

Устройство работает следующим

образом.

В режиме функционального контроля на входную клемму 14 устройства (входы усилителей 2 и 3 блока аналоговых компараторов) поступают сигналы с выхода БИС с заданной частотой контроля (фиг,2а). В блоке 1 аналоговых компараторрв происходит

0

5 0

5

0

5

5

0

0

сравнение уровней этих сигналов с . уровнями 1 и О, задаваемых источниками опорных 19 и 20 напряжений. На входную клемму 16 и, следовательно, второй вход триггера 7 поступает эталонный сигнал (фиг.2б). На входную клемму 17 и, следовательно, на второй вход триггера 8 поступает сигнал управления работой выходного триггера 6 (фиг.2в). На входную клемму 24 и, следовательно, на второй вход триггера 25 поступает сигнал управления контролем третьего состояния (фиг.2г). По достижении контролируемым сигналом уровня О (сЬиг.2а, момент времени tt), срабатывает усилитель 3 блока 1 аналоговых компараторов и на его выходе Формируется сигнал (фиг.2д). Аналогично в момент вре- времени t2 срабатывает.усилитель 2 (фиг,2е) с приходом стробирующего импульса на входную клемму 15 и вторые входы триггеров 4,5,7,8 и 25 (фиг.2ж, момент времени ts) в них записывается информация, установленная на первых входах этих триггеров. При этом на выходе триггера 4 устанавливается сигнал, показанный на фиг.2з, на выходе триггера 5 - сиг-, нал, показанный на фиг.2и, на прямом и инверсном выходах триггера 7 - сигналы, показанные на фиг.2к,л, на выходе триггера 8 - сигнал, показанный на фиг.2м, на прямом и инверсном выходах триггера 25 - сигналы, показанные на фиг,2н,о соответственно, на выходе блока 23 равнозначности установится сигнал, определяемый сигналами с выхода триггеров 4 и 5, показан на фиг.2п.

Выходные сигналы, поступающие с прямого и инверсного выходов триггера 7 на входы блока 10 коммутации, разрешают прохождение сигналов с выхода триггеров 4 и 5 памяти. Выходной сигнал блока 10 коммутации показан на фиг.2р.

Выходные сигналы, поступающие с прямого и инверсного выходов триггера 25 на входы второго блока 26 коммутации, разрешают прохождение сигналов с блока 10 коммутации и блока 23 равнозначности.

Выходная информация с второго блока 26 коммутации (фиг.2с), задержанная в блоке 9 стробирующим импульсом (фиг.2т, момент времени t4)

переписывается в триггер 6 при сиг- нале разрешения с выхода триггера 8 (1 - сигнал разрешения, О - сигнал запрета). Если контролируемая, импульсная последовательность сигналов соответствует по своим уровням заданным значениям О и 1, то на выходе триггера 6 сигнал брака отсутствует. Если уровень контролируемого сигнала не соответствует заданным значениям, то на выходе триггера 6 формируется сигнал Брак (фиг.2у). Момент времени ts соответствует браку при функциональном контроле.

Контроль третьего состояния на клемме 14 для подключения объекта контроля происходит следующим образом: высокоомный делитель напряжения на резисторах 21 и 22 подключен к источникам опорных напряжений U0fl| и Uor)i, а средняя точка делителя подключена к клемме 14, следовательно, уровень сигнала на клемме 14 при высоком импедансе на выходе объекта контроля, будет определяться уровням опорных напряжений Uoni , Uon1 и величинами резисторов 21 и 22.

Величины резисторов 21 (R 41) и 22 (R4.j) выбираются так, чтобы в рабочем низкоимпедансном состоянии выхода объекта контроля они не вносили дополнительной нагрузки и в то же время были много меньше входного сопротивления усилителей 2 и 3. При этом условии уровень сигнала на клемме 14 в нерабочем высокоимпедансном состоянии на выходе объекта контроля можно определить по формуле

ме 15 записываются в триггеры 4 и 5.. памяти, на выходах которых устанав- . ливаются равнозначные сигналы, при этом на выходе блока 23 равнозначности формируется уровень логического О, что является признаком Годен и свидетельствует о третьем состоянии на выходе объекта контроля .

Если в ожидаемый момент времени выход объекта контроля не переходит в третье состояние, а продолжает оставаться в одном из логических состояний, то в зависимости от уровня логилогического сигнала на клемме 14 один из усилителей 2 и 3 устанавливаете г в единичное состояние, а другой - в нулевое состояние. Сигналы с выходтв усилителей 2 и 3 записываются по

сигналу синхронизации в триггеры 4 и 5 памяти, на выходах которых таг.же устанавливаются противофазные сигналы, при этом блок 23 равнозначности формирует на своем выходе уровень логической 1, что является признаком Брак при контроле третьего состояния на выходе объекта контроля. Учитывая, что второй блок 26 коммутации в это время разрешает прохождение сигнала с выхода блока 23 раг- нозначности, по сигналу синхронгзации с задержкой времени, необходимой на обработку сигналов контроля внутри устройства, сигнал признака Брак записывается в выходной триггер 6, на временной диаграмме (фиг.2) этот момент соответствует моменту времени t«.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционального контроля больших интегральных схем | 1983 |

|

SU1109687A1 |

| Устройство для функционального контроля цифровых интегральных схем | 1987 |

|

SU1430915A1 |

| Устройство для функционального контроля больших интегральных схем | 1990 |

|

SU1809398A1 |

| Устройство для контроля параметров линейных стабилизаторов напряжения | 1990 |

|

SU1803891A1 |

| Автоматизированная система контроля | 1989 |

|

SU1695269A1 |

| Устройство для выделения наибольшего и наименьшего однополярных сигналов | 1976 |

|

SU773637A1 |

| Устройство для контроля средств числового программного управления | 1988 |

|

SU1675852A1 |

| Устройство для функционального контроля больших интегральных схем | 1985 |

|

SU1291905A1 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Устройство для интегрирования | 1983 |

|

SU1108470A1 |

Изобретение относится к контрольно-испытательной технике и может быть использовано для функционального контроля больших интегральных схем, имеющих выходы с третьим состоянием. Цель изобретения - расширение функциональных возможностей - достигается в результате возможности контроля третьего состояния. Устройство для контроля больших интегральных микросхем содержит блок 1 аналоговых компараторов, операционные усилители 2 и 3, D-триггеры 4 и 5 памяти, выходной D-триггер 6, Dтриггеры 7 и 8, блок 9 задержки, первый блок 10 коммутации, в состав которого входят логические элементы И-НЕ 11 и 12, ИЛИ-НЕ 13, клемму 14 для подключения объекта контроля, входные клеммы 15,16 и 17, выходную клемму 18, клеммы 19 и 20 для подключения источников опорных напряжений, резисторы 21 и 22, блок 23 равнозначности, входную клемму 24, блок 26 коммутации, в состав которого входят элементы И-НЕ 27 и 28, ИЛИ-НЕ 29, D-триггер 25. 1 з.п.ф-лы, 2 ил.

U Ra,+ R ai

R 14 + U

j

т.е. уровень сигнала будет меньше уровня иоП1.и больше уровня иоп1.

В этом случае на выходах усилителей 2 и 3 установятся уровни логической I. Чтобы отличить момент времени, когда выход объекта контроля находится в третьем состоянии, от момента формирования на его выходе логических уровней, в триггер 25 записывается сигнал разрешения конт- роля третьего состояния, т.е. разрешения прохождения сигнала от выхода блока 23 равнозначности через второй блок 26 коммутации на первый вход выходного триггера 6.

Сигналы с выходов усилителей 2 и 3 по сигналу синхронизации на клем40

Формула изобретения

третий, четвертый и пятый триггеры, блок задержки, блок аналоговых компараторов, первый блок коммутации, клемму для подключения объекта контроля, которая соединена с входом

блока аналоговых компараторов, состоящего из первого и второго усилителей, первый, вход первого усилителя соединен с первым источником опорного напряжения, второй вход которого соединен с клеммой для подключен ния объекта контроля и с первым вхо- ,дом второго усилителя, второй вход которого соединен с вторым источником опорного напряжения, первый выход блока аналоговых компараторов соединен с D-входом первого О-триг гера, С-вход которого соединен с С-входами второго D-триггера, третьего D-триггера, четвертого D-триг-, гера и клеммой для подключения строб импульса устройства и с входом блока задержки, выход которого соединен с С-входом пятого D-триггера, выход которого соединен с клеммой выхода устройства, а R-вход - с выходом четвертого D-триггера, D-вход которого соединен с первой клеммой управления устройства, клемма эталонной ин- формации устройства соединена с р-входом третьего D-триггера, прямой выход которого соединен с первым входом первого блока коммутации, второй вход которого соединен с выходом пер- вого D-триггера, а третий вход - с выходом второго D-триггера, четвертый - с инверсным выходом третьего D-триггера, D-вход второго D-триггера соединен с вторым выходом блока аналоговых компараторов, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности контроля третьего состояния, в устройство введены блок равнозначности, второй блок коммутации, шестой D-триггер, вторая клемма управления устройства, которая соединена с D-входом шестого D-триггера, которого соединен с входом строб-импульса, прямой выход которого соединен с первым входом второго блока коммутации,второй

вход которого соединен с выходом блока равнозначности, первый вход которого соединен с выходом первого D-триггера и вторым входом первого блока коммутации, выход которого соединен с третьим входом второго блока коммутации, -четвертый вход которого соединен с инверсным выходом шестого D-триггера, а выход - с D-ВХОДОМ пятого р-триггера, второй вход блока равнозначности соединен с выходом второго D-триггера и третьим входом первого блока коммутации, а в блок аналоговых компараторов введены первый и второй резисторы, первый вывод последнего соединен с вторым источником опорного напряжения, а второй вывод - с клеммой для подключения -объекта - контроля, с первым входом второго усилителя, вторым входом первого усилителя, с первым выводом перт вого резистора, второй вывод которого соединен с первым источником опорного напряжения.

Ut

6 в

г

д е ж

опг

и

к л м

н о

л

Р

с т

У

Фиг. Z

| Фазометр В.Б.Ибрагимова | 1986 |

|

SU1337810A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для функционального контроля больших интегральных схем | 1983 |

|

SU1109687A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-08-07—Публикация

1988-04-20—Подача