Изобретение относится к автоматике и вычислите. технике и может быть применено при разработке, наладке и рем()нте ЗВЛ и цифровых устройств.

Цель изобретения - расширение фуик циональных возможностей устройстиа и по вышение достоверности контроля состояния цифровых схем за счет определенип состояния «Обрыв иа входе щупа независимо ог полярности напряжения, и возможнсдти не только достоверно определять момент inj явления и исчезновения третьего сосгоянии на выходе цифровых схем, но и иссле.ч.с- вать амплитуды выходных сигиа. иж без до 11олнительн1 1х искажений, что позволяет зна чительно повысить достоверность контро,1я цп(})ровых схем, преимун1ественно с гремя гостояниями.

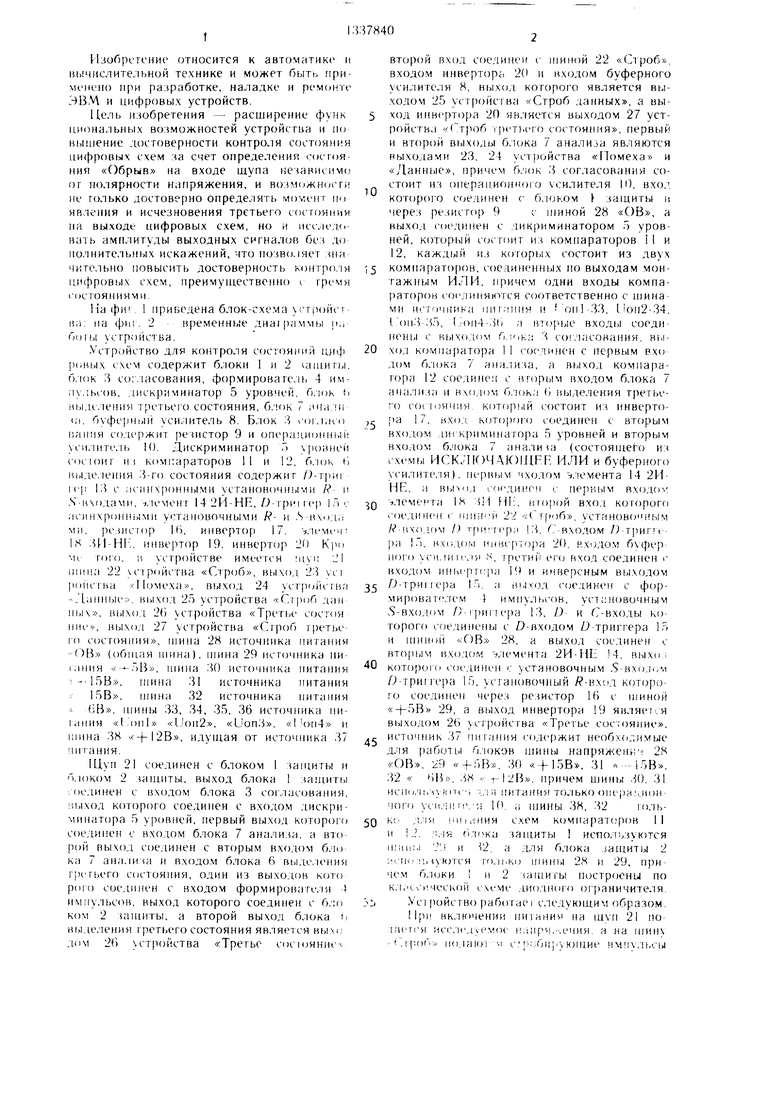

lia фи . 1 11ри зедена блок-схема чгтройсг на: на фиг. 2 временные диа1)а.ммы ,,- 01ИЫ устройства.

Устройство для контроля СОС1 ОЯИИЙ ЦЛ(|1

)(,ц|)1х схем содержит б.токи 1 и 2 илаиты. блок 3 согласования, формировагел, 4 им- ;|.1ьсов, дискриминатор 5 уровней, б.юк ii иьшмения т) состояния, б. юк 7 амали |, |. буферН|,1Й уси;1итель 8. Блок 3 ()Iл,lco а|1пя содержит резистор 9 и операционный уся. игге.И) 10. Дискриминатор Г) yjioaHcii сосюиг И компараторов II и 12, б.иж Г) .ie)niH .3-го состояния содержит / -триг |Г р 13 с ;к-||ихронными установ()чн1,1ми А и .Ч -к одами, . 14 2И-НЕ, О-т)11 гер 1..) . асинхронными установочными R- и .S вход,1 ми, рсзисгор И), инвертор 17. . ieMeii: IS ... инвертор 19. инвертор 20 Крп Ml того, ii стр()йстве имеется :uyi; 21 iiihiia 22 строЙ1 тва «Строб, выход 23 vci pniiciHa IIoMexa, выход 24 ycrpoi icina Данные, выход 25 устройства «Слроб дан ны, выход 2() устройства «Третье сосгои ние, 27 устройства «Сгроб третье го состояния, Н1ина 28 источника питания ОК ((.)б|цая И1ина), тина 29 источника ни- га1шя ..)В, тина 3f) источника питания --158, тина ,31 источника питания

1SB, 1иина 32 источника питания (;В. П1ИНЫ 33, 34, 35, 36 источника ни- 1ания «Ьон1 «L. on2, «Uon3. «1 oii4 и тина .38 -f 12В, идун1ая от источника 37 1и (ания.

1Цуп 21 соединен с блоком 1 запдиты и o.iOKOM 2 защиты, выход блока 1 защиты .оединен с входом блока 3 со|-ласования, 11,гход которого соединен с входом дискриминатора Г) у|м)вней, первый выход которого соединен с входом блока 7 анализа, а вто рой выход соединен с вторым входом бло ка 7 ана.1иза и входом блока 6 выделения г нчьего состояния, один из вьгходов кото рого соединен с входом формировате.тя i импульсов, выход которого соединен с б. :о ком 2 зап1иты, а второй выход блока t, , 1ения третьего состояния является вы.хг; дом 26 ст|1ойства «Трегье сосюянис

5

0

5

0

5

0

второй вход соединен с Н1иной 22 «Строб., входом инвертора 2(1 и входом буферного уси;1ителя 8, выход которого является выходом 25 уст)О11сгва «Строб данных, а выход иршертора 20 янлнетсн выходом 27 устройства «( греть(го состояния, первый и второй выходы блсжа 7 анали.за являются р ыходами 23, 24 устройства «Помеха и «/1анные, причем б. 1ок 3 согласования состоит ич операционного ч силителя 10, вход, которого соединен с блоком I защиты и через резистор 9 с тиной 28 «С)В, а выход (-оединен с .дикриминатором 5 уровней, который c(jcroHT из компараторов 1 1 и 12, каждый из когорых состоит из двух компараторов, соединенных по выходам мон- гажным ИДИ, цриче.м одни входы компараторов со1 линякггся соответственно с тинами источника III г. шпя и оц1-33, lk)n2-34. I ()||.3 35, (.oii4-.3i( а (.1рые входы соединены с F-ibixo;inM fj. I jK.- со ласонания, вы- х.)Д кг)мпа)атора 1 1 сос .тинен с первьгм BXCJ дом б,;1ока 7 анализа, а выход компаратора 12 соединен с вторым входом блока 7 ана.тиза и вхо.юм б.чок. (i выделения третьего соп1 ям;|и. который состоит из инверто- )а 17, нход KOTopoi o сс единен с вторым входом :1И( кримина гора 5 уровней и вторым входом блока 7 ана, (cocтoящe o из схемы ИСКД()Ч.ЛК)1ЛРГ- ИДИ и буферного уси, 1ителя). перв1 1м чх(хтом элемента 14 2И- ИЕ, а ВЫМ1Д со( .. riepj-sbiM входо - элемента 18 ПИ. нгорой BXO.I которого гоединен с 22 ()б. установочным /(-fixo.ioM ) три:-г-( р.;| .3, С-входом Л-триггс- ра Г), входо.м И|( 20. входом буферного vcn. |и 1 c. iji S, гретий соедипеп г входом и 1Ы рг(;ра 19 и инверсным выходом О-трипера 15. ,-i выхгхч сое.тинен с фор- мирова 4 импульсов, уст;:)1овочн| 1м -входкм //-григ1е)а 1.3, О и С-входы кг.)- торого соединещ с D-входом D-триггера 15 и iiiHHoii «OB 28. а выход соединен с вторым входом ;1емента 2И-И1: 4, выхи ; К(ггорог() соединен с установочным ,S-Bxoji/M 0-три Ч ра 15, установочный R-KXO.I которого соединен через )езистор 16 с ()й «4-5В 29, а выход инвертора 19 являемся выходом 26 устройства «Третье состояние, источник 37 1игания содержит необходимые д,1|я )аботы олоков тины напряженич 28 «ОВ, 29 «-f5B, 30 «+15В, 31 «-15В, ,32 « ИЬ:. .38 - t-l2fi.. причем щииы 30. 31 исц||.ч1,з г;пс-, :..;; ита)1ия только оиера..,ионЧОГО СИ. ;|| ( Д.-1Я

уси. ;11 (;; 10. а тины 38, 32 голь- |. 1я схем к(.1мнарат(;ров II . .:.1я олпка защиты 1 используются . и 2, а д,тя блока .защиты 2 :ьп К)тся rn.ii.Ki) 111ин1 1 28 и 29. при- б.:|(.)ки и 2 защиты построены по ..си.ческой схеме диодного ограничителя. Ус1ройс1во раб(ггае1 следующим образом. 1ри включении питании на щуп 21 по- ьаеггя Hcc. KMvevoc н.црч.- -.ения. а на тину лрог. iio.iaio -v: с: ;))щие имну.тьсы

и

I П . 11

: . чем

K. l,

(именпся в виду импульсы, ак швный p(i веиь у которых Еи 1сокий), причем строби- рующие HMiiv. ibcu расположены во времен ном интервале внутри исследуем,1х импульсов; что показана.) на диаграмме.

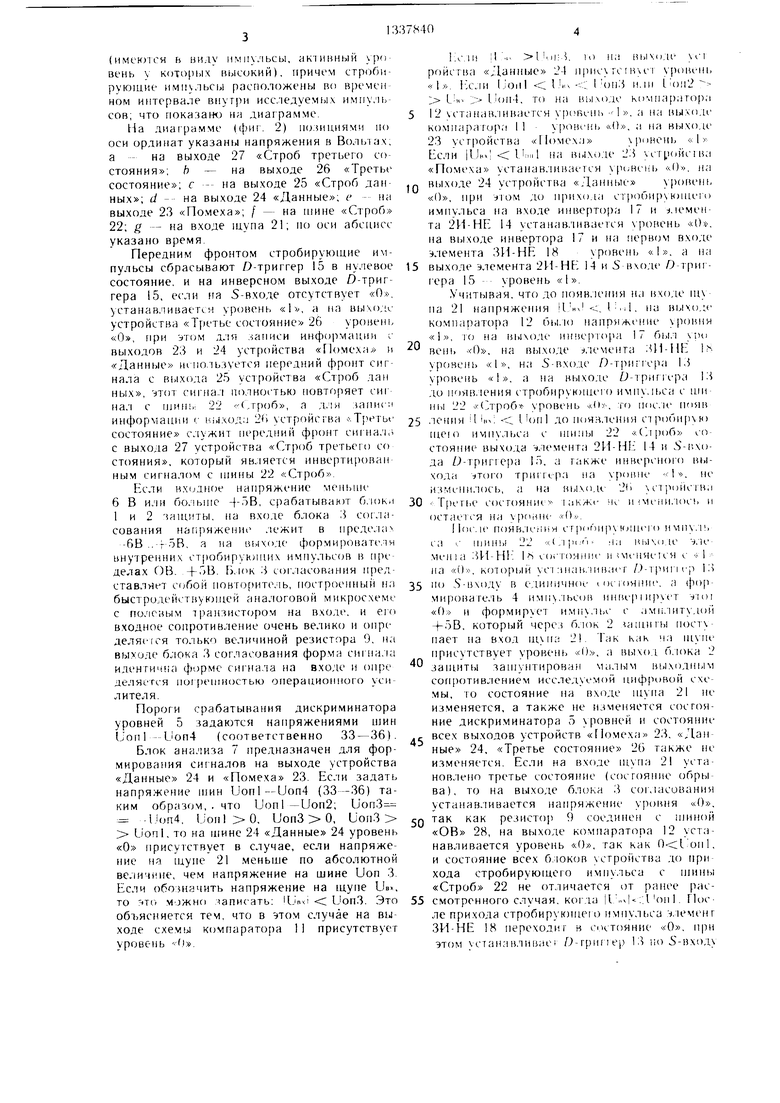

На диаграмме (фиг. 2) 11о.ициями но оси ординат указаны напряжения в Волы ах, а - на выходе 27 «Строб третьего состояния ; b - на выходе 26 «Третье состояние ; с --- на выходе 25 «Строб данных ; d -- на выходе 24 «Данные ; е - на выходе 23 «Помеха ; f - на ишне «Строб 22; g - на входе щупа 21; но оси абсцисс указано время

Передним фронтом стробирующие импульсы сбрасывают О-триггер 15 в нулевое состояние, и на инверсном выходе D-триг- гера 15, если на 5-входе отсутствует «О, устанавливается уровень «1, а на (),чс устройства «Третье состояние 26 уровень «О, при эт()м д:1я записи информации г выходов 23 и 24 устройства «Помеха и «Данные ипюльуп ется передний фронт сигнала с В1 1хода 25 ус1ройства «Строб дан ных, :)Т()т сигна.т шхтностью повторяет сиг нал с 1иип1, 22 ..троб, а дли :iarnic:i информации с 2(i устройсгва йТ;)еты состояние с. 1ужит передний фронт сигнал,i с выхода 27 устройства «Строб третьего со стояния, который является инверти(Н)ван ным сигналом с Н1ины 22 «Строб.

гели нх(.. ДНС)е напряжение меньше 6 В или больше , срабатывают блоки 1 и 2 защиты, на входе блока 3 co, ia- сования напряжение лежит в нpeдe.кl -6В .. f 5В, а на выходе формироват1 1и внутренних ст))1Пнх импульсов в делах ОВ. -|-Г)В. хюк 3 согласования представляет собой понтог)итоль, построенный на бысл родей. тнук)1лей аналоговой микрс схеме с поленым транзистором на входе, и его входное сопротивление очень великс.) и онре деляс ся только величиной резистора 9, на выходе блока 3 согласования форма сигнала идентична форме сигнала на входе и опре деляется ПО )ен1Н()стью операционного усилителя.

Пороги срабатывания дискриминатора уровней 5 задаются напряжениями н)ин Uonl - Llon4 (соответственно 33 - 36).

Блок анализа 7 предназначен для формирования сигналов на выходе устройства «Данные 24 и «Помеха 23. Если задать напряжение тин Uonl-Uon4 (33-36) таким образом,, что Uonl-Uon2; Uon3 11оп4, , , Uon3 Uonl, TO на тине 24 «Данные 24 уровень «О присутствует в случае, если напряжение на туне 21 меньше по абсолютной велич ше, чем напряжение на шине Uon 3. Если обозначить напряжение на щупе UB, то r-iTo М .;жнг) .записать: lUnxi Uon3. Это об1)Ясняется тем, что в этом случае на выходе схе.мы компарато)а 11 присутствует уровень ..

IA-.M iU.,, .Uui.5. 10 на 1 1 1ХоД1 - ci ройства «Данные 24 прнс гсшхст х ровень «1. 1;с,:1и Uoiil 1 « Uon3 или Uon2 : 1 и-- UoH4, то на выходе компарагора

12 станав,1ивается уровень , а на выходе KOMiiapa гора I 1 уроиоШ) .(, а на выхо.и 23 усгройстна «Помеха (i(iBeiii., «I Если .iil па Bi.ixo.ie 23 хстройспк «Помеха устанав.чинаегся П;ВС |{ь «О, на

выходе 24 устройства «Данн1 1е ровень «О, при угом до npnxo.ia стробирук)П1е1 о импульса на входе инвертора 17 и j,ieMeii- та 2И-ПЕ 14 устанав, 1иваегся р1)иень «(), на выходе инвертора 17 и на первом входе ь лемента ЗП-НЕ 18 уровень «1, а на

выходе элемента 2И-НЕ 14 и S входе /3-триг- г ера 15 - ypOBefib «I.

Учитывая, что до появления входе ni

0

0

напряжения

на выходе

компаратора 12 бы.ю напряжение уровня «1, К) на выходе инвертора 17 был siui BCiib d), на в1)Гходе :)лемента ЗП-ПЕ Ь уровень , на ,5-вх()дс D-триггера 13 уровень «1, а на выходе / -триг1ера 13 до появления стробируюшсмо имну,ьса с unt Н1,1 22 (троб уровень «(., го noc,ie ппяв

5 ления iUnx i llonl до появления С1роби)н) цею импульса с типы 22 «Слроб v o стояние выхода элемента 2П-ПЕ 14 и S-iixo- да ZJ -триггера 15, а гакже инверсного выхода этого триггер, на р) -Н , не измепнлось, а па ныходе 2ti c ipoiicTB,i

0 Т)егье сосгоянио 1акжг не и (Мгни.юсь и остается на р(|цн(- ;()...-.

ll(uM( появ:к пин егрог ) KjiiKTo имну. и, (.Л I тины 22 :(/I jii;n. .чи (i.ie э. К - MeHia ЗИ-П1 I coiTOHHiie и «меняемся с на «О, который ус 1:1на1(.111в;)(Ч /..) eji 13

5 II .S-входу в единичное (осгонпие, а ( .мировате,чь 4 имп, 1ьсов нн((ер1ирует эю: «0.- и формирует .е с амплитудой -Ь5В, которь1Й через б,1ок 2 uiiiuniji пост пает па вход 21. Так как чп щупе присутствует уровень «О, а выхо.т б.юка 2 защиты зашуптировам малым вь1хг)днь1м )тивлением исследуемой цифровой схемы, то состояние па входе niyna 21 не изменяется, а также не изменяется сосгоя- ние дискриминатора 5 ровней и состояние

с всех выходов устройств «Помеха 23, «Данные 24, «Третье состояние 26 также не изменяется. Если на входе щупа 21 установлено третье состояние (сосгояние обрыва), то на выходе блока 3 сог,тасовании устанавливается напряжение уровня «О,

Q так как резистор 9 соединен с тиной «ОВ 28, па выходе компаратора 12 устанавливается уровень «О, так как 0 ;Uonl, и состояние всех б. стройства до при хода стробирующего импу,тьса с тины «Строб 22 не отличается от ранее рас5 смотренного случая, когда 11,, :.Uoii 1. После прихода стробирукицего импульса элеменг ЗИ-НЕ 18 переходиг в состояние «О, при этом устан,чвлииаег D-rpnriei.) 1 i по S-входу

в единичное состояние и на влором входе .1 е м е н т н 14 2 И - Н Е у ст а и а в. i и н а етс я «I , на выходе блока 2 зашиты состояние изменяется из «О U «1, в этом случае на выходе блока 3 согласования устанавливается напряжение, уровень KOTopoi o выше, чем I oiil, на выходе компаратора 12 «I, которая переводит элемент 14 2И-НЕ: из состояния «I в «О. Таким образом, D-триггер 15 устанавливается по S-входу в единичное состояние, а на инверсном его входе формируется «О, на выходе 26 уст юйства «Третье состояние состояние изменяется с «О в «1. Кроме того, на выходе инвертора 17 устанавливается «О, на выходе : лемента 18 ЗИ-НЕ и на входе формирователя 4 импульсов и 5-вх{)де О-триггера 13 - «I, импульс на выходе формирователя 4 .1ьсов : ,аканчивается и состояние на входе inviia 21 не отличается от обрыва.

По заве)Н1ени1о импульса с Н1ины 22 -(/гроб на выходе инвертора 20 и выходе 27 усг|1ойства «Строб третьего состояния формируется :1о,-|ожитель)|ый перепад, предпаз- наченньи тля записи информации с В1)1хода 2ti ycrpoiiciBa «Третье С1)стояние, а также но завершению импульса с шины 22 «Строб /) триггер 13 устанавливается в нулевое сосгояние но Л -входу, ;i на выходе улемен- т; 14 2И-НЕ и S-входе A. -TpHiTepa 15 с ганаЕ , 1Ивается « I .

С.осгояние выхода 2Н «Третье coi-тояние Н( и (меияет -я до иоявлс ния очс-редног о )Са С шины 22 «(юб, кого|1ый передним фронтом по пе 1еводиг O-TfiHi- I ер 1 Г) в нулевое состояние и на ипверс ном |и)1ходе iron) )а устанавливаегся с(к Т()Яни1 «1, а на 1и) 2Г) устройства Г). ы. состожше «О. Да. 1ьнейп1ее сосгояние в Ixoдa 26 устройства «Третье со- сгояпие зависит от состояния на входе шу- па 21. Таким образом, информация на выходах 23 и 24 устройства «Помеха, «/1анные устанавливается до прихода импульса с шины 22 «(троб и в течение iroi o импульса не изменяется, а на выходе 2( устройства «Третье состояние информация устанавлнвается до окончания импу,1ьса с шины 22 «Строб и до начала с,тедую- шего этого имнульса не изменяется.

Быст)одейс гвие устройства он)еде, 1нется быстродействием операциоппого усплите,тя И), компараторов 11 и 12 и временем задержки цепи обратпой связи от выхода компа)атора 12 до входа шупа 21, резистор Я выбирается порядка десятков мОм для увеличения входного сопротивления устройства. Таким образом, устройство позволяет контролнровать цифровые схем1 1 не только с ноложительньим уровнем сигна

лов «О и «I, но и с отрицательным уровнем этих сигша.чов, а пороги срабатывания задаются произвольно напряжением П1ИН (Jon 1 1;оп4 (33 ,36), при эюм устройство реагирует одинаково как на сигналы положительного у(М)Вня, так и отрицательного.

Формула u:i itpi гения

,.., J.

Устроисгво д;1я конт)оля состс янии цифровых схем, содержащее шуп, соединенный через последовательно соединенные первый блок зашиты и б;1ок со асования с первым входом дискриминатора уровней, перг вый выход которого соединен с первым входом блока анализа, первый выход которого соединен с первым выходом устройства, шины д,тя иол,к.м1очения исгочника питании. формп)овате,1;. им |у:1ьсов. первый инвертор, отличаннцссся те.м, чт(, с це,1ью расн1ире0 ния функционалы1ых возможностей и новь1- шения Д(к товерр1ости контроля, в него введены второй 6,(jK зашиты, буферный уси- ,1ите;|. б.юк выде.аения третье1-о состояния, содержащий второй и третий инверторы, первый и второй D-г И1гге)ы, элемент 2И-НЕ,

резистор, племен г ЗИ-HF-., выход которо о соединен с иход(;м формирователя импу.чь- сов и установочн1)1м ..S-входом первого D- . Л -вход кого)ого соединен с «Строб, nej)BbiM вчо.чом элемента ЗИ-НЕ.

„ входом nepsiiH 1 инвг-ртора, пход(;м буферного уси. 1ите.:1я и С-ь;()До.м второго О-т)иггера. выход которою соединен с вторым входом элемента ЗИ-HL . и входом второго инве|| тора, выход KOToptJrtJ сое. щнен с BTOpiiiM выходом устройства, третий вход элемента

ЗИ-НЕ соединен с выходом третьего инвертора, вход когорого соединен с первым входом э. 2И-ЫЕ, вторым входом блока анализа и вторым выходом дискрими- нато)а уровней, второй, третий, четвертый и входы которого соединены с С(..ч.1Т0 г етствую1цими к.леммами ыя 1голк,)чения источника онорног ) н:|п)яжения, формироват(ля импульсов через второй блок защиты соединен со шупом, О-входы первого и второго D-триггеров соединене. с С -вх(.)дом нервого О-триг|-ера и с обшей шиной, выход первого /J-триггера соединен с вторым входом элемента 2И-НЕ, выход которого соединен с Л-входом второго / -триггера, / -вход KOTopoid через резистор соединен с клеммой д,1Я подк.1К.)чения источника питания, вто)ой выход блока анализа, выход буферно|() усилителя и выход перв .ио ин- ве| ГО|)а соединены соотве1ственно с г)е- тьим, четвертым и пятым выходами ст- ройства.

5

0

p

ъ

П П П П П П

о.

Г1.

F

дбрыб

П

-t t

t

J: t

«Ci

Q

.

П

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для компенсации реактивной мощности | 1990 |

|

SU1746463A1 |

| Цифровой фазометр | 1986 |

|

SU1368808A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1783582A1 |

| Устройство автоматического замедления полосы на участке нагона петли непрерывного профилегибочного агрегата | 1983 |

|

SU1233972A2 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Устройство для моделирования вентильного преобразователя | 1981 |

|

SU968829A1 |

| Устройство автоматического контроля правильности чередования и отсутствия обрыва фаз многофазных сетей переменного тока | 1989 |

|

SU1674015A2 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1988 |

|

SU1737731A1 |

| Устройство для регистрации информации | 1985 |

|

SU1308839A1 |

| Устройство для измерения времени задержки импульсов в разночастотных каналах | 1986 |

|

SU1337881A1 |

И:и)бретение относится к автоматике и вычислительной технике и может найти применение при разработке и наладке 3B.V и цифровых устройств. Изобретение расширяет функциональные возможности уст)ойст ва и повышает достоверность контроля состояния цифроны.х схем, так как иозво.чяот определять состояние 1)брыв, независимо от полярности напряжения, исследовать амм- выходных снгнале)В без дополнитс.и.- ных искажений. Устройство содержит блоки 1 и 2 зан1,иты, блок 3 согласования, формирователь 4 импульсов, дискриминатор 5 уровней, блок 6 выделения третьего состояния, блок 7 ана. нкза, буферный усилитель 8. Блок 3 содержит резистор 9 и операционный усилитель 10 13лок 5 состоит нл компараторов 11 и 12, б,1ок fi содержит О-трип еры 13 и 15, элемент 2 И-НН 14. pc.uicrop 16, инвертор 17. : лемент 3 И-HF. 8. инвертор 19. В устр(йсгве имеются niyn 21. входные и выходные шины, 1иины источников питания. зыст|)одсйстви( у1тройстиа определяелся быст)одействием ()ационп() ID усилителя 10, компараторов И и 2 и в)( менем заде)жки 1:еми обрмгио связи oi В11|хода компа|)атора 12 ю входа тупа 21. 2 ил. (Л гз СО СО 00 4 О фиг f

| Логический пробник | 1982 |

|

SU1045179A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля логических состояний цифровых схем | 1982 |

|

SU1113756A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-09-15—Публикация

1985-06-10—Подача