Изобретение относится к электросвязи и может использоваться в телеграфии.

Цель изобретения - обеспечение встречной работы с разными стартстоп- но-синхронными системами

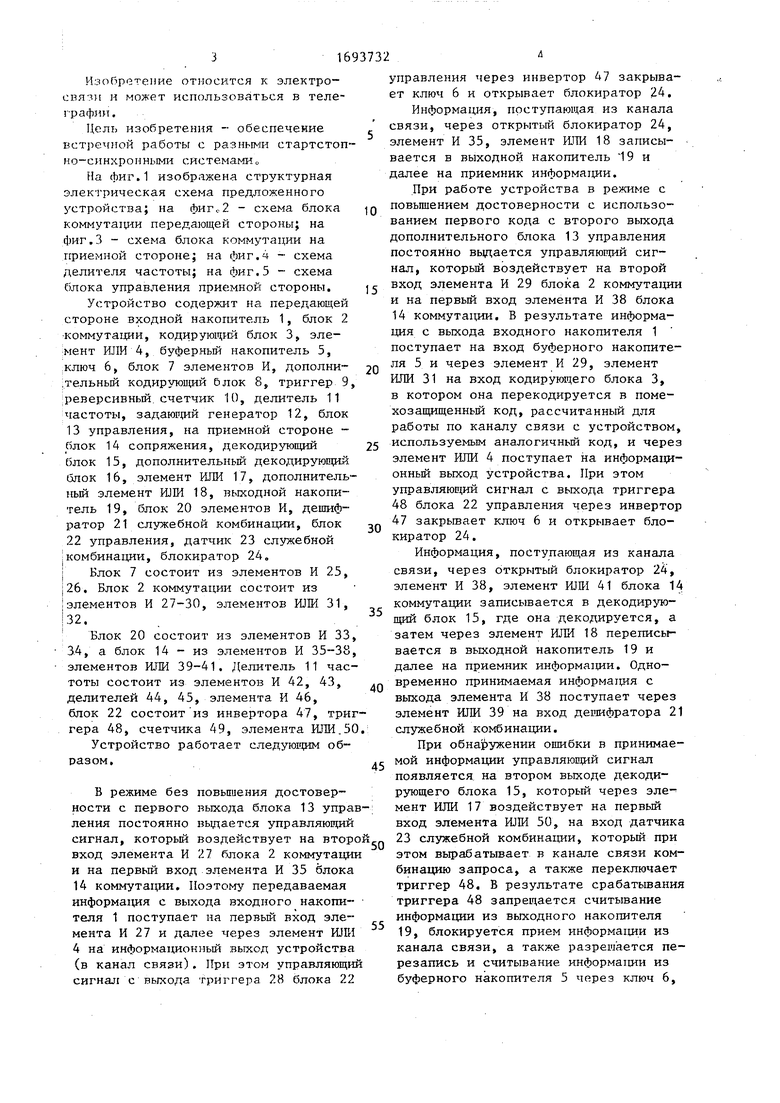

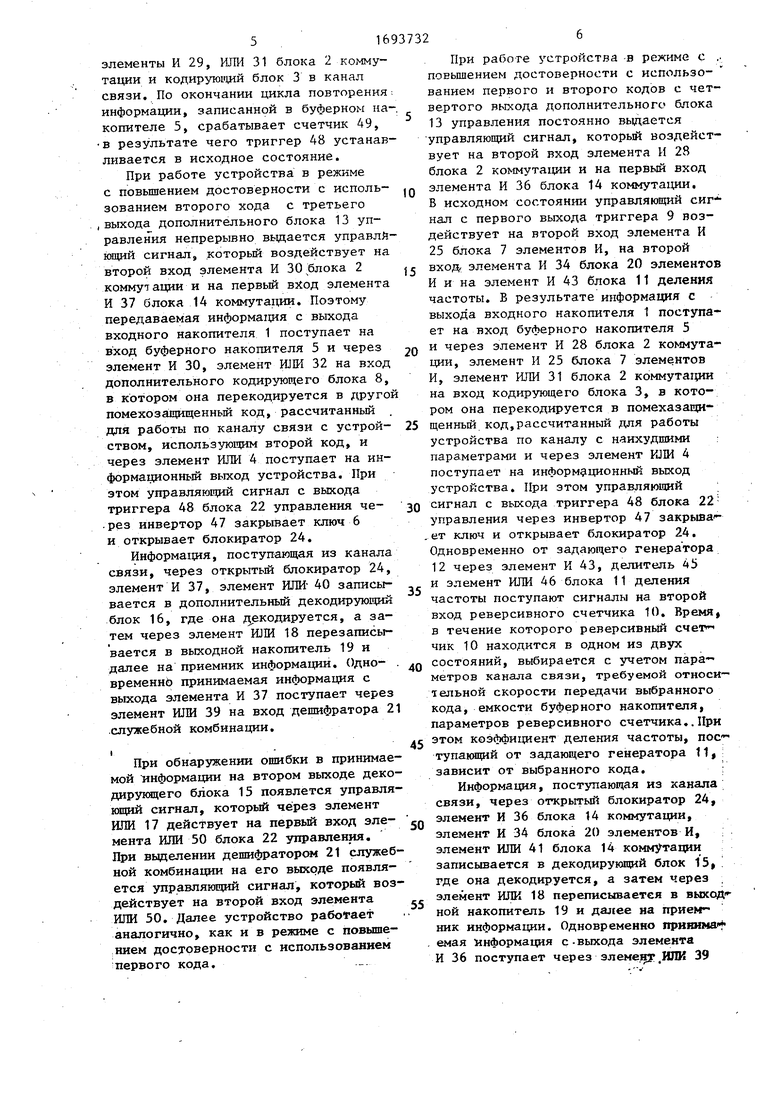

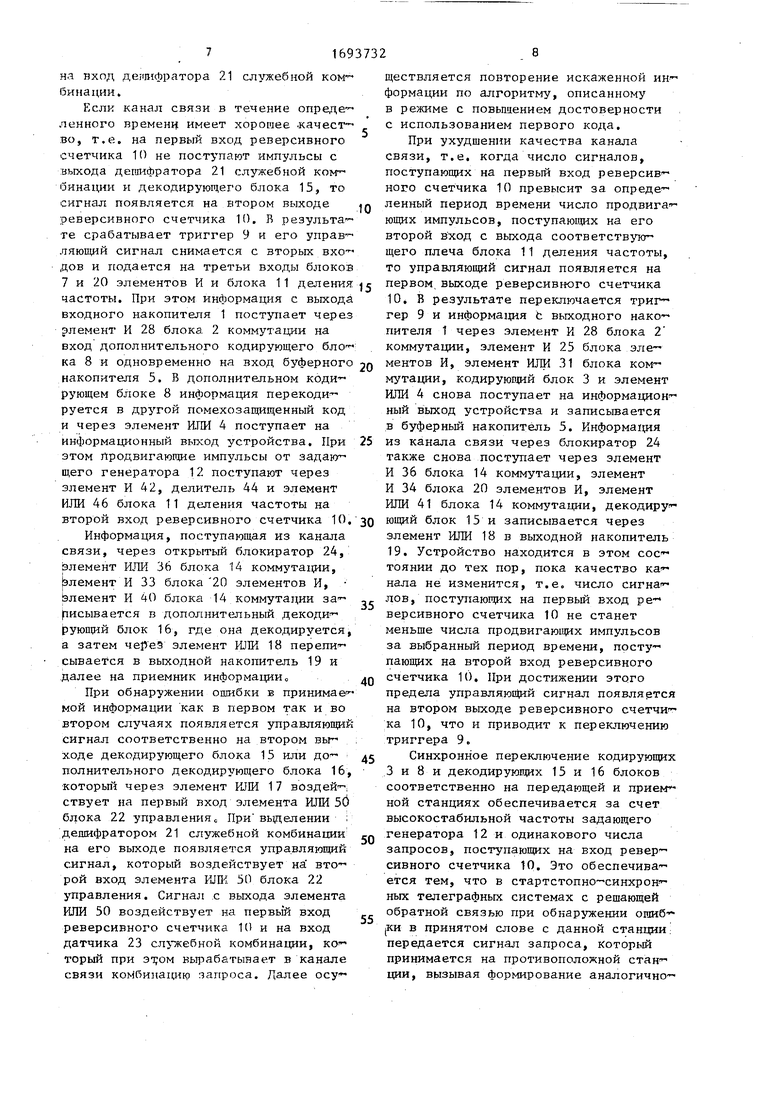

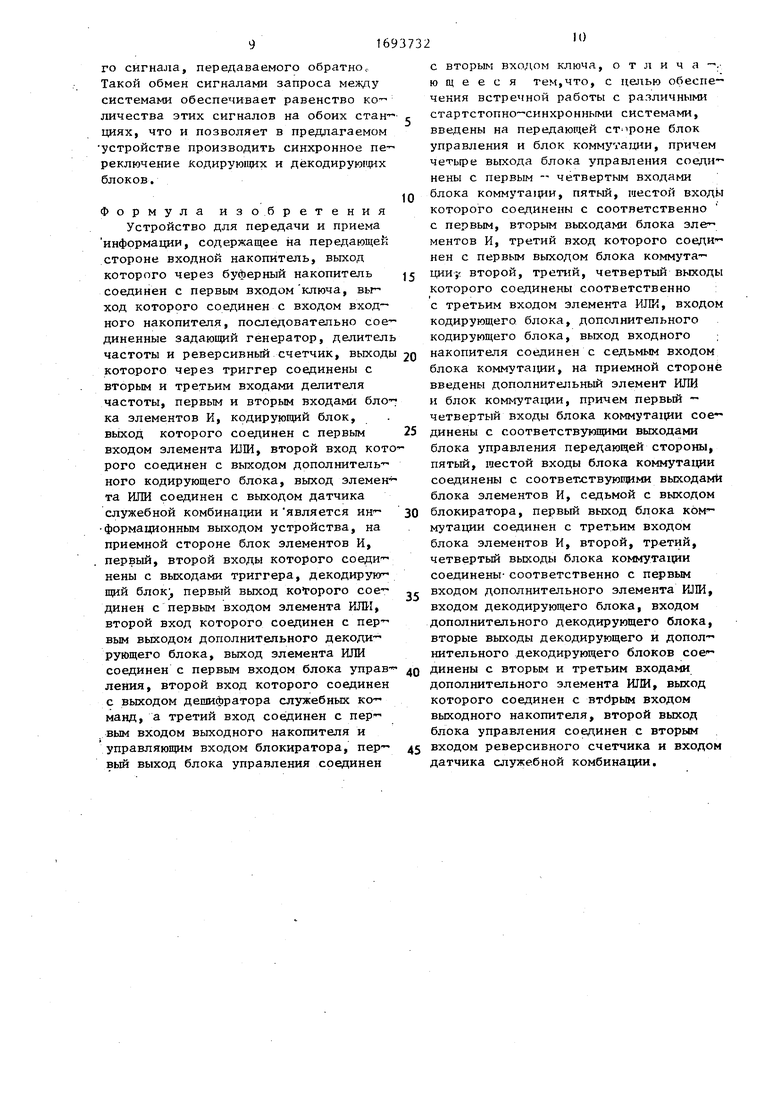

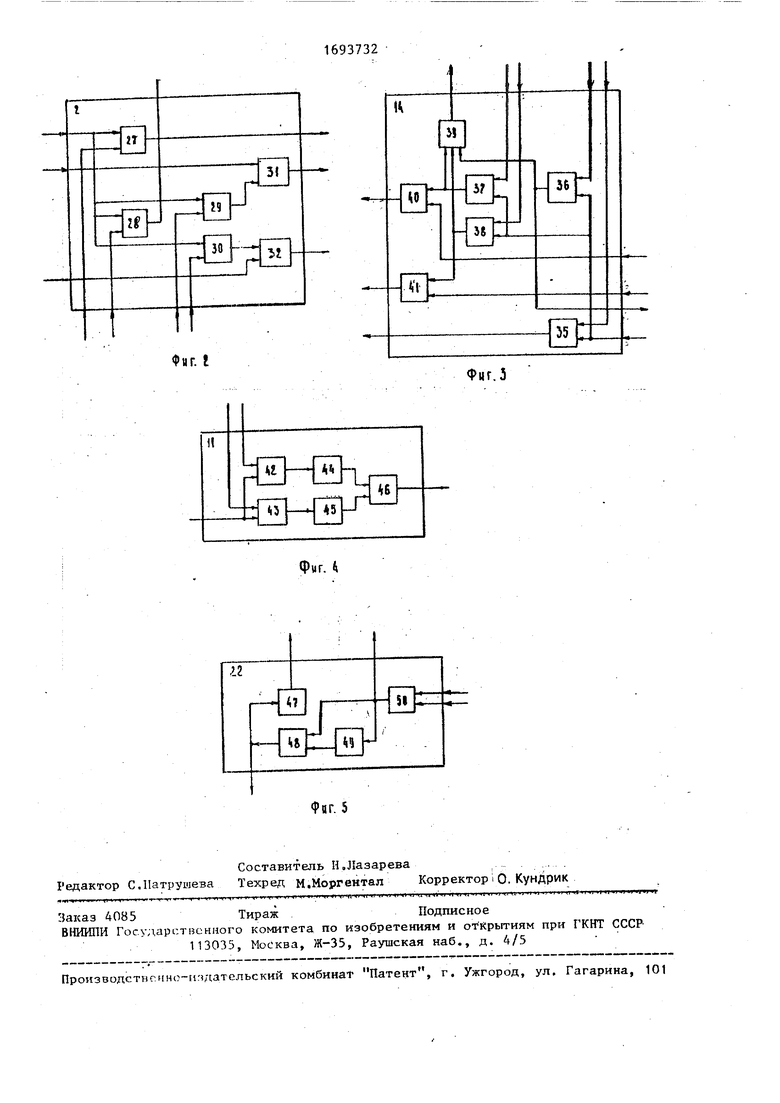

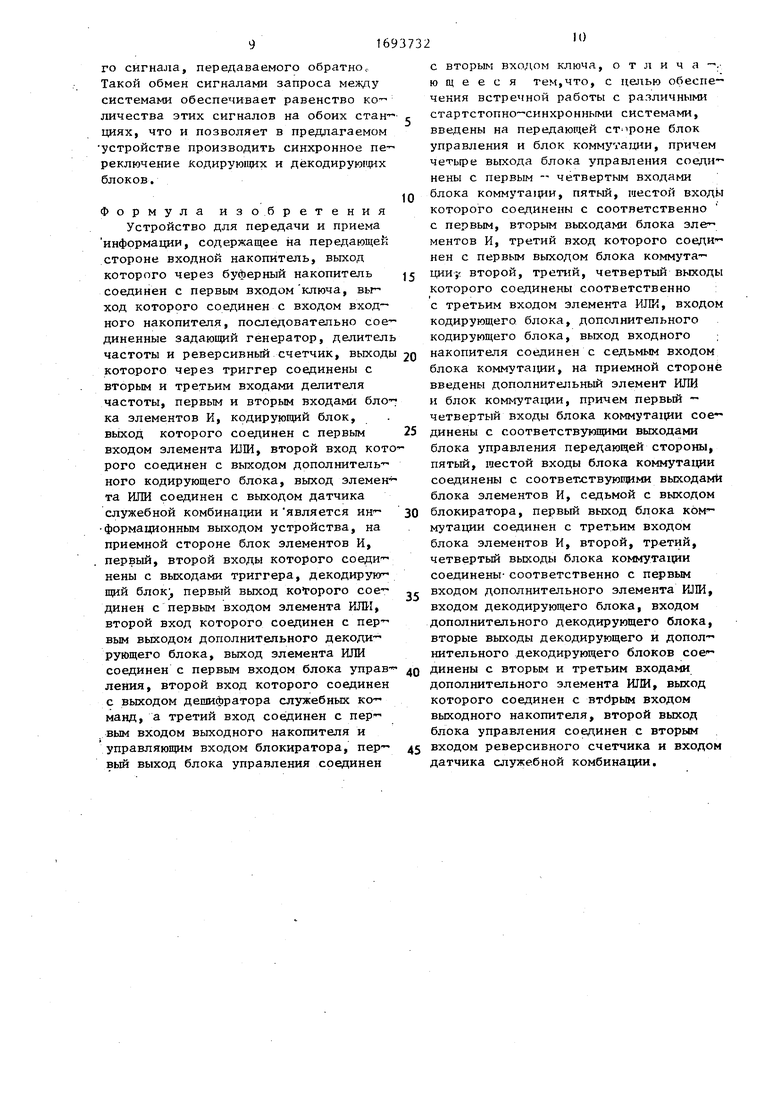

На фиг.1 изображена структурная электрическая схема предложенного устройства; на фиг„2 - схема блока коммутации передающей стороны; на фиг.З - схема блока коммутации на приемной стороне; на фиг.ч - схема делителя частоты; на фиг.5 - схема блока управления приемной стороны.

Устройство содержит на передающей стороне входной накопитель 1, блок 2 коммутации, кодирующий блок 3, элемент ИЛИ 4, буферный накопитель 5, ключ 6, блок 7 элементов И, дополнительный кодирующий блок 8, триггер 9, реверсивный счетчик 10, делитель 11 частоты, задающий генератор 12, блок 13 управления, на приемной стороне - блок 14 сопряжения, декодирующий блок 15, дополнительный декодирующий блок 16, элемент ИЛИ 17, дополнительный элемент ИЛИ 18, выходной накопитель 19, блок 20 элементов И, дешифратор 21 служебной комбинации, блок 22 управления, датчик 23 служебной комбинации, блокиратор 24.

Блок 7 состоит из элементов И 25, 26. Блок 2 коммутации состоит из элементов И 27-30, элементов ИЛИ 31, 32.

Блок 20 состоит из элементов И 33, 34, а блок 14 - из элементов И 35-38, элементов ИЛИ 39-41. Делитель 11 частоты состоит из элементов И 42, 43, делителей 44, 45, элемента И 46, блок 22 состоит из инвертора 47, триггера 48, счетчика 49, элемента ИЛИ.50

Устройство работает следующим образом.

При обнаружении ошибки в принимае- дс мой информации управляющий сигнал появляется на втором выходе декодирующего блока 15, который через элемент ИЛИ 17 воздействует на первый вход элемента ИЛИ 50, на вход датчика

В режиме без повышения достоверности с первого выхода блока 13 управления постоянно выдается управляющий сигнал, который воздействует на второй,.., 23 служебной комбинации, который при пэтом вырабатывает в канале связи комвход элемента И 27 блока 2 коммутации и на первый вход элемента И 35 блока 14 коммутации. Поэтому передаваемая информация с выхода входного накопителя 1 поступает на первый вход элемента И 27 и далее через элемент ИЛИ 4 на информационный выход устройства (в канал связи). При этом управляющий сигнал с выхода триггера 28 блока 22

55

в

бинацию запроса, а также переключает триггер 48. В результате срабатывания триггера 48 запрещается считывание информации из выходного накопителя 19, блокируется прием информации из канала связи, а также разрешается перезапись и считывание информации из буферного накопителя 5 через ключ 6,

5

0

управления через инвертор 47 закрывает ключ 6 и открывает блокиратор 24.

Информация, поступающая из канала связи, через открытый блокиратор 24, элемент И 35, элемент ИЛИ 18 записывается в выходной накопитель 19 и далее на приемник информации.

При работе устройства в режиме с повышением достоверности с использованием первого кода с второго выхода дополнительного блока 13 управления постоянно выдается управляющий сигнал, который воздействует на второй вход элемента И 29 блока 2 коммутации и на первый вход элемента И 38 блока 14 коммутации. В результате информация с выхода входного накопителя 1 поступает на вход буферного накопителя 5 и через элемент И 29, элемент ИЛИ 31 на вход кодирующего блока 3, в котором она перекодируется в поме- хозащищенный код, рассчитанный для работы по каналу связи с устройством, используемым аналогичный код, и через элемент ИЛИ 4 поступает на информационный выход устройства. При этом управляющий сигнал с выхода триггера 48 блока 22 управления через инвертор 47 закрывает ключ 6 и открывает блокиратор 24.

Информация, поступающая из канала связи, через открытый блокиратор 24, элемент И 38, элемент ИЛИ 41 блока 14 коммутации записывается в декодирующий блок 15, где она декодируется, а затем через элемент ИЛИ 18 переписывается в выходной накопитель 19 и далее на приемник информации. Одновременно принимаемая информация с выхода элемента И 38 поступает через элемент ИЛИ 39 на вход дешифратора 21 служебной комбинации.

При обнаружении ошибки в принимае- с мой информации управляющий сигнал появляется на втором выходе декодирующего блока 15, который через элемент ИЛИ 17 воздействует на первый вход элемента ИЛИ 50, на вход датчика

5

0

5

0

.., 23 служебной комбинации, который при этом вырабатывает в канале связи ком23 служебной комбинации, который при этом вырабатывает в канале связи ком

в

бинацию запроса, а также переключает триггер 48. В результате срабатывания триггера 48 запрещается считывание информации из выходного накопителя 19, блокируется прием информации из канала связи, а также разрешается перезапись и считывание информации из буферного накопителя 5 через ключ 6,

10

15

51693732

элементы И 29, ИЛИ 31 блока 2 коммутации и кодирующий блок 3 в канал вязи. По окончании цикла повторения нформации, записанной в буферном накопителе 5, срабатывает счетчик 49,

в результате чего триггер 48 устанавливается в исходное состояние.

При работе устройства в режиме с повышением достоверности с использованием второго хода с третьего

выхода дополнительного блока 13 упавления непрерывно выдается управлящий сигнал, который воздействует на второй вход элемента И 30 чблока 2 коммутации и на первый вход элемента И 37 блока 14 коммутации. Поэтому передаваемая информация с выхода входного накопителя 1 поступает на вход буферного накопителя 5 и через элемент И 30, элемент ИЛИ 32 на вход ополнительного кодирующего блока 8, в котором она перекодируется в другой помехозащшценный код, рассчитанный для работы по каналу связи с устройством, использующим второй код, и через элемент ИЛИ 4 поступает на информационный выход устройства. При этом управляющий сигнал с выхода триггера 48 блока 22 управления через инвертор 47 закрывает ключ 6 и открывает блокиратор 24.

Информация, поступающая из канала связи, через открытый блокиратор 24, элемент И 37, элемент ИЛИ 40 записывается в дополнительный декодирующий блок 16, где она декодируется, а затем через элемент ИЛИ 18 перезаписывается в выходной накопитель 19 и далее на приемник информации. Одновременно принимаемая информация с выхода элемента И 37 поступает через элемент ИЛИ 39 на вход дешифратора 21 служебной комбинации.

20

25

1 ч с т к па д5 э

30

35

40

При обнаружении ошибки в принимаемой информации на втором выходе декодирующего блока 15 появлется управляющий сигнал, который через элемент ИЛИ 17 действует на первый вход элемента ИЛИ 50 блока 22 управления. При выделении дешифратором 21 служебной комбинации на его выходе появляется управляющий сигнал, который воздействует на второй вход элемента ИЛИ 50. Далее устройство работает аналогично, как и в режиме с повышением достоверности с использованием первого кода.

0

5

0

5

При работе устройства в режиме с . повышением достоверности с использованием первого и второго кодов с четвертого выхода дополнительного блока 13 управления постоянно выдастся управляющий сигнал, который воздействует на второй вход элемента И 28 блока 2 коммутации и на первый вход элемента И 36 блока 14 коммутации. В исходном состоянии управляющий сиг нал с первого выхода триггера 9 воздействует на второй вход элемента И 25 блока 7 элементов И, на второй вход, элемента И 34 блока 20 элементов И и на элемент И 43 блока 11 деления частоты. В результате информация с выхода входного накопителя 1 поступает на вход буферного накопителя 5 и через элемент И 28 блока 2 коммутации, элемент И 25 блока 7 элементов И, элемент ИЛИ 31 блока 2 коммутации на вход кодирующего блока 3, в котором она перекодируется в помехазащн- щенный код,рассчитанный для работы устройства по каналу с наихудшими параметрами и через элемент ИЛИ 4 поступает на информационный выход устройства. При этом управляющий сигнал с выхода триггера 48 блока 22 управления через инвертор 47 закрыва - ет ключ и открывает блокиратор 24. Одновременно от задающего генератора 12 через элемент И 43, делитель 45 и элемент ИЛИ 46 блока 11 деления частоты поступают сигналы на второй вход реверсивного счетчика К), Время, в течение которого реверсивный чик 10 находится в одном из двух состояний, выбирается с учетом параметров канала связи, требуемой относительной скорости передачи выбранного кода, емкости буферного накопителя, параметров реверсивного счетчика.,При 5 этом коэффициент деления частоты, тупающий от задающего генератора 11, зависит от выбранного кода.

Информация, поступающая из канала связи, через открытый блокиратор 24, элемент И 36 блока 14 коммутации, элемент И 34 блока 20 элементов И, элемент ИЛИ 41 блока 14 коммутации записывается в декодирующий блок 15, где она декодируется, а затем через элемент ИЛИ 18 переписывается в выход - ной накопитель 19 и далее на прием- ник информации. Одновременно принимав емая информация с.выхода элемента И 36 поступает через элеменуДШК 39

0

5

0

0

5

на вход дешифратора 21 служебной ком бинации.

Если канал связи в течение опреде- ленного времени имеет хорошее -качество, т.е. на первый вход реверсивного счетчика 10 не поступают импульсы с выхода дешифратора 21 служебной ком- бинации и декодирующего блока 15, то сигнал появляется на втором выходе реверсивного счетчика 10. В результа- те срабатывает триггер 9 и его управ- ляющий сигнал снимается с вторых вхо- дов и подается на третьи входы блоков 7 и 20 элементов И и блока 11 деления частоты. При этом информация с выхода входного накопителя 1 поступает через элемент И 28 блока 2 коммутации на вход дополнительного кодирующего бло- ка 8 и одновременно на вход буферного накопителя 5. В дополнительном коди- рующем блоке 8 информация перекоди- руется в другой помехозащищенный код и через элемент ИЛИ 4 поступает на информационный выход устройства. При этом Продвигающие импульсы от задаю- щего генератора 12 поступают через элемент И 42, делитель 44 и элемент ИЛИ 46 блока 11 деления частоты на второй вход реверсивного счетчика 10. Информация, поступающая из канала связи, через открытый блокиратор 24, элемент ИЛИ 36 блока 14 коммутации, элемент И 33 блока 20 элементов И, элемент И 40 блока 14 коммутации за-™ писывается в дополнительный декоди- рующий блок 16, где она декодируется, а затем через элемент ИЛИ 18 перепи- сывается в выходной накопитель 19 и далее на приемник информации.

При обнаружении ошибки в принимав1 мой информации как в первом так и во втором случаях появляется управляющий сигнал соответственно на втором вы- ходе декодирующего блока 15 или дополнительного декодирующего блока 16, который через элемент ИЛИ 17 воздей- ствует на первый вход элемента ИЛИ 5Й блока 22 управления с При выделении дешифратором 21 служебной комбинации на его выходе появляется управляющий сигнал, который воздействует на второй вход элемента ИЛИ 50 блока 22 управления. Сигнал с выхода элемента ИЛИ 50 воздействует на первый вход реверсивного счетчика 10 и на вход датчика 23 служебной комбинации, ко- торый при эт,ом вырабатывает в канале связи комбинацию запроса. Далее осу-

5

0

5

0

5

0

5

0

5

ществляется повторение искаженной информации по алгоритму, описанному в режиме с повышением достоверности с использованием первого кода.

При ухудшении качества канала связи, т.е. когда число сигналов, поступающих на первый вход реверсивного счетчика 10 превысит за определенный период времени число продвигающих импульсов, поступающих на его второй вход с выхода соответствующего плеча блока 11 деления частоты, то управляющий сигнал появляется на первом выходе реверсивного счетчика 10. В результате переключается триггер 9 и информация с выходного накопителя 1 через элемент И 28 блока 2 коммутации, элемент И 25 блока элементов И, элемент ИЛИ 31 блока коммутации, кодирующий блок 3 и элемент ИЛИ 4 снова поступает на информационный выход устройства и записывается в буферный накопитель 5. Информация из канала связи через блокиратор 24 также снова поступает через элемент И 36 блока 14 коммутации, элемент И 34 блока 20 элементов И, элемент ИЛИ 41 блока 14 коммутации, декодирующий блок 15 и записывается через элемент ИЛИ 18 в выходной накопитель 19. Устройство находится в этом состоянии до тех пор, пока качество канала не изменится, т.е. число сигналов, поступающих на первый вход реверсивного счетчика 10 не станет меньше числа продвигающих импульсов за выбранный период времени, поступающих на второй вход реверсивного счетчика 10. При достижении этого предела управляющий сигнал появляется на втором выходе реверсивного счетчика 10, что и приводит к переключению триггера 9.

Синхронное переключение кодирующих 3 и 8 и декодирующих 15 и 16 блоков соответственно на передающей и приемной станциях обеспечивается за счет высокостабильной частоты задающего генератора 12 и одинакового числа запросов, поступающих на вход реверсивного счетчика 10. Это обеспечивается тем, что в стартстопно-синхрон- ных телеграфных системах с решающей обратной связью при обнаружении ошиб- (ки в принятом слове с данной станции передается сигнал запроса, который принимается на противоположной станции, вызывая формирование аналогично-

го сигнала, передаваемого обратнос Такой обмен сигналами запроса между системами обеспечивает равенство ко- личества этих сигналов на обоих стан- циях, что и позволяет в предлагаемом устройстве производить синхронное переключение кодирующих и декодирующих блоков.

Формула изобретения Устройство для передачи и приема информации, содержащее на передающей стороне входной накопитель, выход которого через буферный накопитель соединен с первым входом ключа, вы- ход которого соединен с входом входного накопителя, последовательно соединенные задающий генератор, делитель частоты и реверсивный счетчик, выходы которого через триггер соединены с вторым и третьим входами делителя частоты, первым и вторым входами блока элементов К, кодирующий блок, выход которого соединен с первым входом элемента ИЛИ, второй вход которого соединен с выходом дополнительного кодирующего блока, выход элемента ИЛИ соединен с выходом датчика служебной комбинации и является ин- формационным выходом устройства, на приемной стороне блок элементов И, первый, второй входы которого соединены с выходами триггера, декодирующий блок , первый выход которого сое- динен с первым входом элемента ИЛИ, второй вход которого соединен с первым выходом дополнительного декодирующего блока, выход элемента ИЛИ соединен с первым входом блока управ- ления, второй вход которого соединен с выходом дешифратора служебных команд, а третий вход соединен с первым входом выходного накопителя и управляющим входом блокиратора, пер- вый выход блока управления соединен

с вторым входом ключа, о т л и ч а -. ю щ е е с я тем,что, с целью обеспечения встречной работы с различными стартстопно-синхронными системами, введены на передающей ст фоне блок управления и блок коммутации, причем четыре выхода блока управления соединены с первым - четвертым входами блока коммутации, пятый, шестой входы которого соединены с соответственно с первым, вторым выходами блока элементов И, третий вход которого соединен с первым выходом блока коммутации-, второй, третий, четвертый выходы которого соединены соответственно с третьим входом элемента ИЛИ, входом кодирующего блока, дополнительного кодирующего блока, выход входного накопителя соединен с седьмым входом блока коммутации, на приемной стороне введены дополнительный элемент ИЛИ и блок коммутации, причем первый - четвертый входы блока коммутации соединены с соответствующими выходами блока управления передающей стороны, пятый, шестой входы блока коммутации соединены с соответствующими выходами блока элементов И, седьмой с выходом блокиратора, первый выход блока коммутации соединен с третьим входом блока элементов И, второй, третий, четвертый выходы блока коммутации соединены- соответственно с первым входом дополнительного элемента ИЛИ, входом декодирующего блока, входом дополнительного декодирующего блока, вторые выходы декодирующего и дополнительного декодирующего блоков соединены с вторым и третьим входами дополнительного элемента ИЛИ, выход которого соединен с втбрым входом выходного накопителя, второй выход блока управления соединен с вторым входом реверсивного счетчика и входом датчика служебной комбинации.

f

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство защиты от ошибок | 1987 |

|

SU1478362A2 |

| Устройство защиты от ошибок | 1984 |

|

SU1197115A1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С МОНОКАНАЛОМ | 1991 |

|

RU2032213C1 |

| Устройство для приема дискретной информации в системах с решающей обратной связью | 1986 |

|

SU1478361A1 |

| Устройство для передачи и приема информации | 1985 |

|

SU1338089A1 |

| Устройство для контроля телеграфного тракта | 1982 |

|

SU1059690A2 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

| Устройство передачи и приема дискретной информации | 1989 |

|

SU1646066A1 |

| Устройство для управления локальной сетью обмена данными | 1987 |

|

SU1478365A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ НАГРУЖЕНИЕМ ПРИ ПРОГРАММНЫХ ИСПЫТАНИЯХ МЕХАНИЧЕСКИХ КОНСТРУКЦИЙ НА УСТАЛОСТНУЮ ПРОЧНОСТЬ | 2007 |

|

RU2365963C2 |

Изобретение относится к электросвязи и может использоваться в телеграфии.1 Цель изобретения - обеспечение встречной работы с различными стартстопно-синхронными системами. Устройство содержит на передающей стороне входной накопитель 1, кодирующий блок 3, элемент ИЛИ 4, буферный накопитель 5, ключ 6, блок 7 элементов И, дополнительный кодирующий блок 8J триггер 9, реверсивный счетчик 10, делитель 11 частоты, задающий генератор 12, на приемной стороне - блокиратор 24, декодирующие блоки 15, 16, элемент ИЛИ 17, выходной накопитель 19, блок 20 элементов И, дешифратор 21 служебной комбинации, блок 22 управления и датчик 23 служебной комбинации. Для достижения цели введены на передающей стороне блок 13 управления и блок 2 коммутации, а на приемной стороне - блок 14 коммутации и дополнительный элемент ИЛИ 18. 5 ил. § (/ CS о 00 N 00

SJ

| Авторское свидетельство СССР № 1192149, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-11-23—Публикация

1989-04-11—Подача